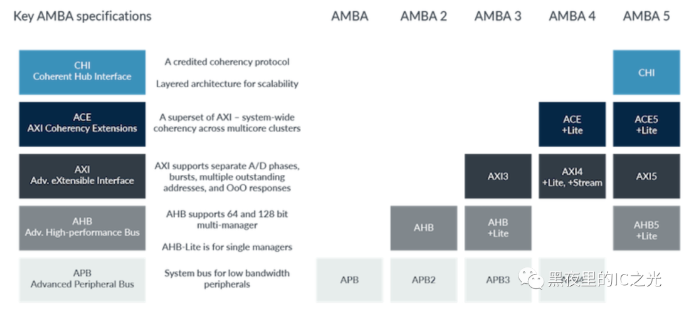

一、AHB-Lite協(xié)議介紹

AHB(Advanced High-performance Bus)高速總線(xiàn),接高速master設(shè)備,APB(Advanced Peripheral Bus)外設(shè)總線(xiàn),用來(lái)接低速slave,AHB主要用于高性能模塊(如CPU、DMA和DSP等)之間的連接,一個(gè)master可以有多個(gè)slave,AHB和APB之間通過(guò)一個(gè)AHB2APB橋轉(zhuǎn)接。這里是實(shí)現(xiàn)一個(gè)AHB-Lite協(xié)議,相較于A(yíng)HB-APB總線(xiàn)協(xié)議,AHB-Lite只有單主機(jī),且沒(méi)有HBUSREQ和HGRANT信號(hào),同時(shí)從設(shè)備信號(hào)接口也簡(jiǎn)單許多。

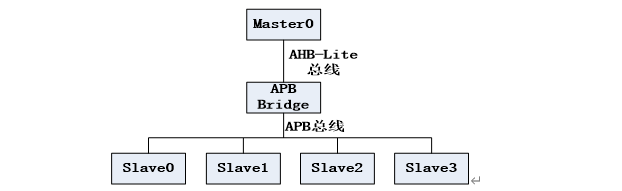

二、系統(tǒng)框架介紹

主設(shè)備Master0利用AHB-Lite總線(xiàn)協(xié)議通過(guò)AHB Bridge訪(fǎng)問(wèn)四個(gè)APB從設(shè)備Slave0、Slave、Slave2和Slave3。每個(gè)從設(shè)備的地址空間如下:

Slave0: 0x0000_0000 ~ 0x0000_00ff;

Slave1: 0x0000_0100 ~ 0x0000_01ff;

Slave2: 0x0000_0200 ~ 0x0000_02ff;

Slave3: 0x0000_0300 ~ 0x0000_03ff;

令從設(shè)備地址空間的下邊界為其地址的基址,假設(shè)每個(gè)從設(shè)備中有可訪(fǎng)問(wèn)APB寄存器16個(gè),位寬均為32比特,16個(gè)寄存器的訪(fǎng)問(wèn)地址計(jì)算方式為 基址 +寄存器編號(hào)左移2位(byte 偏移)

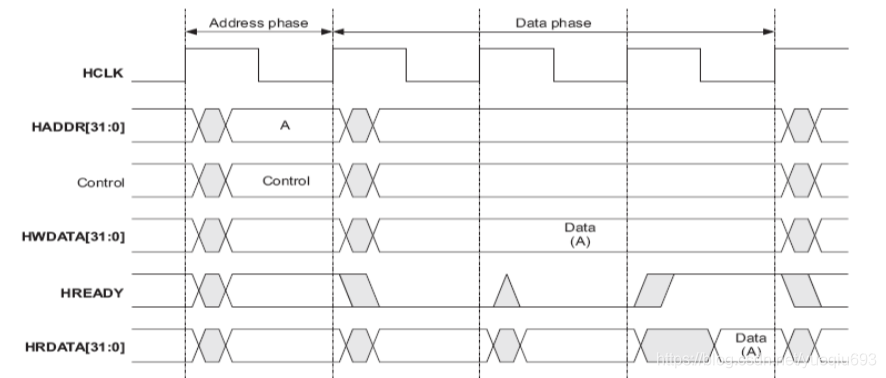

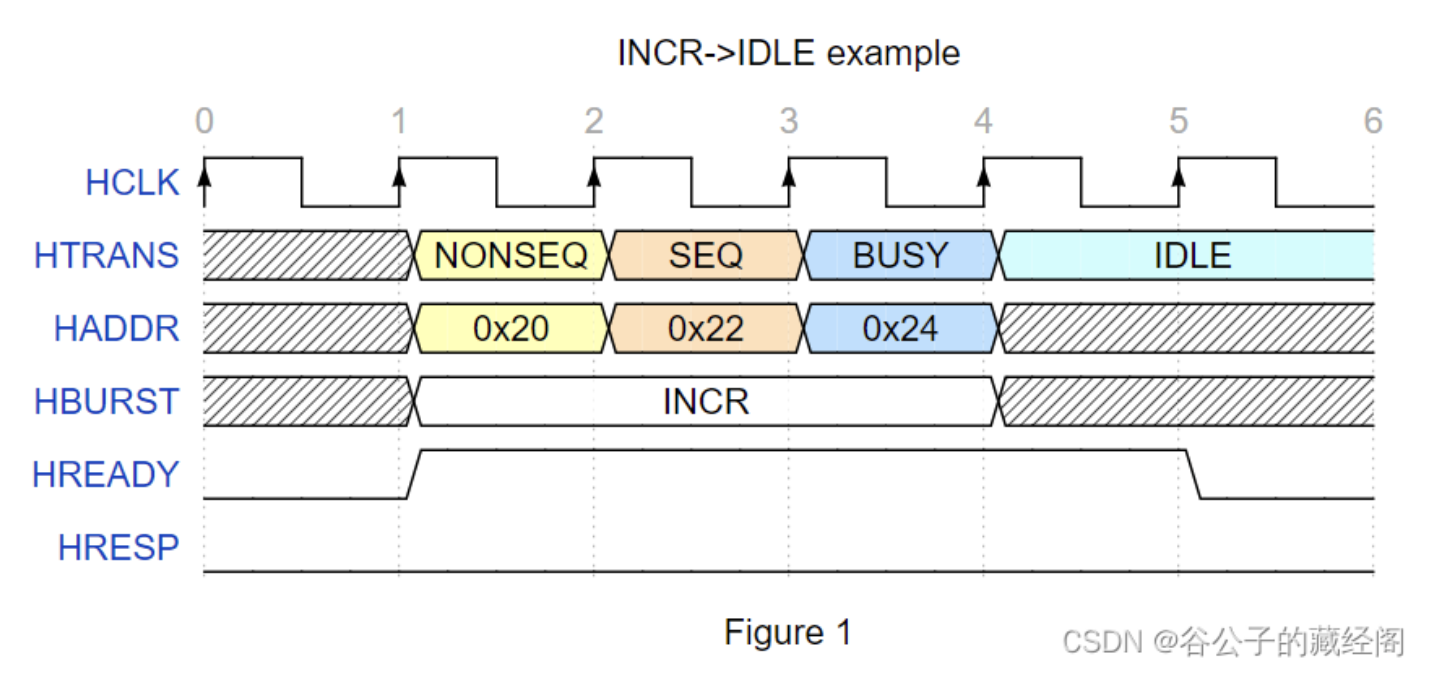

主設(shè)備接口的數(shù)據(jù)讀寫(xiě)采用AHB-Lite總線(xiàn)協(xié)議,并遵循如下時(shí)序規(guī)范:

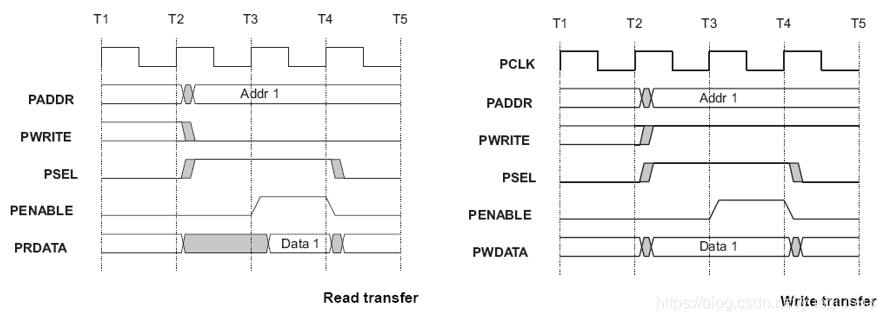

從設(shè)備讀寫(xiě)遵循APB時(shí)序規(guī)范:

三、代碼設(shè)計(jì)

模塊里包含Master 、Slave、Bridge設(shè)計(jì)

代碼如下:

//-------------------------

//File Name:AHB_APB.v

//Designer:Liang Genyuan

//-------------------------

module AHB_APB(

HCLK,

HRESETn,

HWRITE,

HADDR,

HWDATAin,

HRDATA,

PRDATAin,

PWDATA

);

input HCLK;

input HRESETn;

input HWRITE;

input [31:0] HADDR;

input [31:0] HWDATAin;

input [31:0] PRDATAin;

output[31:0] HRDATA;

output[31:0] PWDATA;

reg PCLK;

wire PRESETn;

wire PWRITE;

reg PSEL;

reg PENABLE;

wire[31:0] PADDR;

reg[31:0] PWDATA;

reg[31:0] PRDATA;

reg[31:0] HWDATA;

reg[31:0] HRDATA;

reg PSELS0;

reg PSELS1;

reg PSELS2;

reg PSELS3;

reg[31:0] HADDR_Reg;

reg HWRITE_Reg;

reg[3:0] HSEL_Reg;

reg[31:0] HWDATA_Reg;

reg[31:0] PRDATA_Reg;

reg HREADY;

reg [3:0] state_c ;

reg [3:0] state_n ;

parameter IDLE = 4'b0000 ;

parameter SETUP = 4'b0001;

parameter ENABLE = 4'b0010 ;

//PCLK二分頻

always @(posedge HCLK) begin

if(!HRESETn)begin

PCLK<=0;

end

else if(HCLK==1'b1)begin

PCLK<=~PCLK;

end

end

//slave選擇

`define S0BASE 4'b0000

`define S1BASE 4'b0001

`define S2BASE 4'b0010

`define S3BASE 4'b0011

wire[3:0] HSEL;

assign HSEL = HADDR[11:8];

always @(*)begin

if(!HRESETn) begin

PSELS0 = 1'b0;

PSELS1 = 1'b0;

PSELS2 = 1'b0;

PSELS3 = 1'b0;

end

case (HSEL)

`S0BASE :

PSELS0 = 1'b1;

`S1BASE :

PSELS1 = 1'b1;

`S2BASE :

PSELS2 = 1'b1;

`S3BASE :

PSELS3 = 1'b1;

endcase

end

//slave讀寫(xiě)

wire[5:0] reg_num;

reg [3:0] PSELx;

assign reg_num= PADDR[7:2];

assign PRESETn=HRESETn;

assign PADDR=HADDR_Reg;

assign PWRITE=HWRITE_Reg;

always @(posedge PCLK or negedge PRESETn) begin

if(!PRESETn)begin

PWDATA<=0;

PRDATA<=0;

end

else if(PWRITE)begin

if((state_c==SETUP)||(state_c==ENABLE))begin

PWDATA<=HWDATA_Reg;

end

else begin

PWDATA<=0;

end

end

else if(!PWRITE)begin

PRDATA<=PRDATAin;

end

else begin

PRDATA<=0;

end

end

//APB bridge狀態(tài)機(jī)

wire idle2setup_start ;

wire setup2enable_start;

wire enable2idle_start ;

always@(posedge HCLK or negedge HRESETn)begin

if(!HRESETn)begin

PSELx<=0;

end

else if(state_c!=IDLE)begin

PSELx<=HSEL_Reg;

end

end

always @(posedge PCLK or negedge PRESETn) begin

if (!PRESETn) begin

state_c <= IDLE ;

end

else begin

state_c <= state_n;

end

end

always @(*) begin

case(state_c)

IDLE :begin

if(idle2setup_start)

state_n = SETUP ;

else

state_n = state_c ;

end

SETUP :begin

if(setup2enable_start)

state_n = ENABLE ;

else

state_n = state_c ;

end

ENABLE :begin

if(enable2idle_start)

state_n = IDLE ;

else

state_n = state_c ;

end

default : state_n = IDLE ;

endcase

end

always@(posedge PCLK or negedge PRESETn)begin

if(PRESETn==1'b0)begin

PENABLE<=0;

PSEL<=0;

end

else if(state_c==SETUP)begin

PSEL<=1;

PENABLE<=0;

end

else if(state_c==ENABLE)begin

PSEL<=1;

PENABLE<=1;

end

else begin

PSEL<=0;

PENABLE<=0;

end

end

assign idle2setup_start = (state_c==IDLE)&&(HADDR!=32'b0) ;

assign setup2enable_start = state_c==SETUP ;

assign enable2idle_start = state_c==ENABLE ;

//橋寄存

always @ (negedge HRESETn or posedge HCLK) begin

if (!HRESETn)

begin

HADDR_Reg <= {32{1'b0}};

HWRITE_Reg <= 1'b0;

end

else

if (HREADY)begin

HADDR_Reg <= HADDR;

HWRITE_Reg <= HWRITE;

end

end

always @(posedge HCLK or negedge HRESETn)begin

if(HRESETn==1'b0)begin

HSEL_Reg<=0;

end

else if(HREADY)begin

HSEL_Reg<=HSEL;

end

end

always @(posedge HCLK or negedge HRESETn)begin

if(HRESETn==1'b0)begin

HWDATA_Reg<=0;

PRDATA_Reg<=0;

end

else if(HWRITE==1)begin

HWDATA_Reg<=HWDATA;

end

else begin

PRDATA_Reg<=PRDATA;

end

end

//master

//HREADY控制

always @(posedge PCLK or negedge PRESETn)begin

if(!PRESETn)begin

HREADY<=0;

end

else if((state_c==IDLE)&&(HWDATA==0))begin

HREADY<=1;

end

else if(state_c==SETUP)begin

HREADY<=0;

end

end

always @(posedge HCLK or negedge HRESETn)begin

if(HRESETn==1'b0)begin

HWDATA<=32'b0;

HRDATA<=32'b0;

end

else if(HWRITE==0)begin

HRDATA<=PRDATA_Reg;

end

else if(HWRITE==1)begin

HWDATA<=HWDATAin;

end

end

endmodule

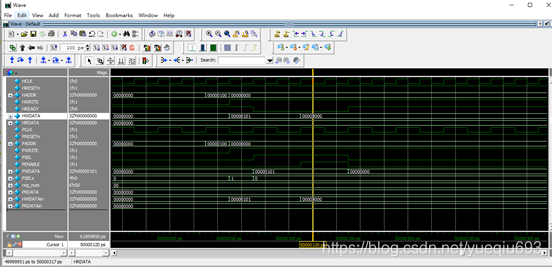

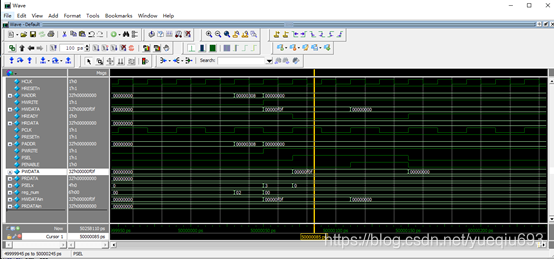

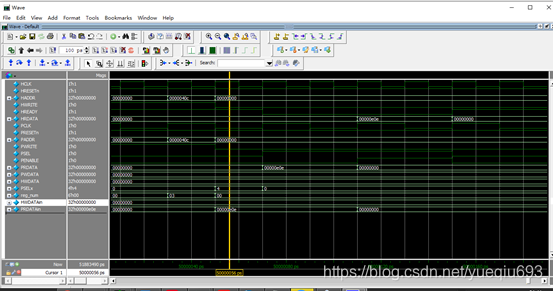

四、仿真測(cè)試

分別對(duì)讀寫(xiě)時(shí)序進(jìn)行兩組測(cè)試:

1、寫(xiě)時(shí)序

a、

HADDR=32’b0000_0000_0000_0000_0000_0001_0000_0000

HWDATAin=32’b0000_0000_0000_0000_0000_0001_0000_0001

PSELx=1,reg_num=0

即選中了第一個(gè)從設(shè)備中第一個(gè)寄存器

b、

HADDR=32’b0000_0000_0000_0000_0000_0011_0000_1000;

HWDATAin=32’b0000_0000_0000_0000_0000_1111_0000_1111;

PSELx=3,reg_num=2

即選中了第三個(gè)從設(shè)備中第三個(gè)寄存器

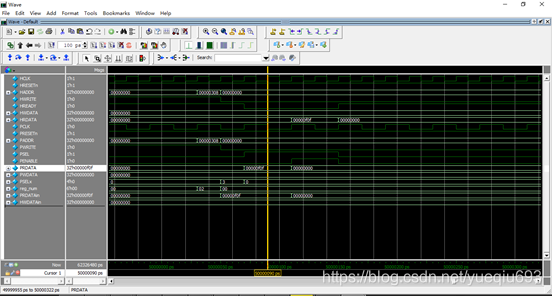

2、讀時(shí)序

a、

HADDR=32’b0000_0000_0000_0000_0000_0011_0000_1000

PRDATAin=32’b00000_0000_0000_0000_0000_1111_0000_1111

PSELx=3 reg_num=2

即第三個(gè)從設(shè)備第三個(gè)寄存器

b、

HADDR=32’b0000_0000_0000_0000_0000_0100_0000_1100

PRDATAin=32’b00000_0000_0000_0000_0000_1110_0000_1110

PSELx=4 reg_num=3

即第四個(gè)從設(shè)備第四個(gè)寄存器

原文鏈接:

https://blog.csdn.net/yueqiu693/article/details/119849052

-

寄存器

+關(guān)注

關(guān)注

31文章

5615瀏覽量

130336 -

接口

+關(guān)注

關(guān)注

33文章

9576瀏覽量

157556 -

總線(xiàn)協(xié)議

+關(guān)注

關(guān)注

0文章

176瀏覽量

15654 -

高速總線(xiàn)

+關(guān)注

關(guān)注

0文章

9瀏覽量

3609

原文標(biāo)題:AHB_Lite協(xié)議介紹

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

STM32—— AHB、APB詳解 精選資料分享

AMBA中的AHB總線(xiàn)協(xié)議詳解

搭建一個(gè)SoC下載到FPGA開(kāi)發(fā)板中設(shè)計(jì)實(shí)現(xiàn)

AHB-lite總線(xiàn)如何處理獨(dú)占訪(fǎng)問(wèn)

基于Cortex-M0搭建SoC并使用軟件驅(qū)動(dòng)蜂鳴器正常切歌播放的設(shè)計(jì)實(shí)現(xiàn)

在A(yíng)rm AMBA協(xié)議集中AHB-lite可否使用

Arm AMBA協(xié)議集中address phase是必須等到hready有效才結(jié)束嗎

ARM CoreLink AXI4至AHB Lite XHB-400橋接技術(shù)參考手冊(cè)

多層AHB技術(shù)概述

PrimeCell通用中斷控制器(PL390)循環(huán)模型9.1.0版用戶(hù)指南

PrimeCell基礎(chǔ)設(shè)施AMBA 2 AHB至AMBA 3 AXI橋(BP136)技術(shù)概述

剖析AHB2、AHB-Lite和AHB5區(qū)別

Arm AMBA 5 AHB5:加速嵌入式和物聯(lián)網(wǎng)世界

AMBA AHB協(xié)議的burst termination簡(jiǎn)析

一文詳解AHB-Lite協(xié)議

一文詳解AHB-Lite協(xié)議

評(píng)論