本文介時鐘頻率概念及其對系統性能的影響,并在電路板級、芯片級和單元模塊級分別提供了減小相位噪聲和抖動的有效方法。

2012-03-10 09:55:23 5225

5225

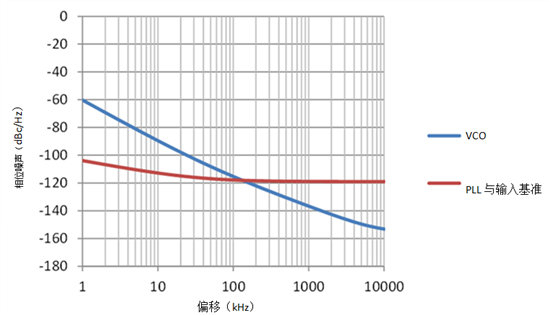

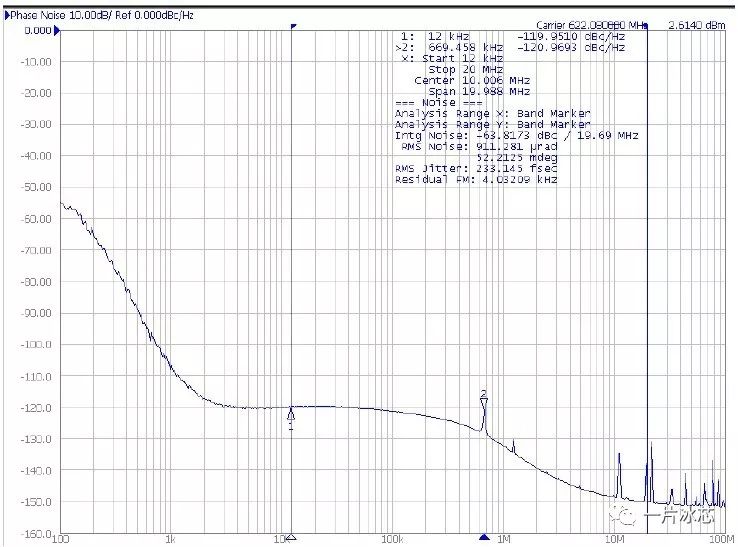

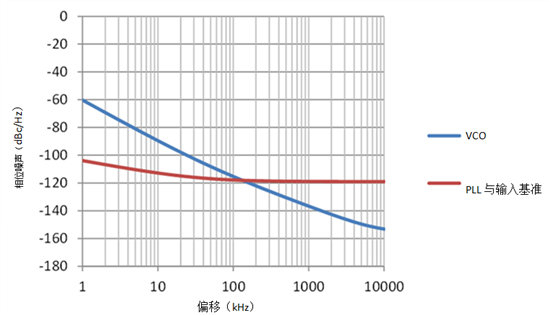

為了正確理解時鐘相關器件的抖動指標規格,同時選擇抖動性能適合系統應用的時鐘解決方案,本文詳細介紹了如何理解兩種類型時鐘驅動器的抖動參數,以及從鎖相環輸出噪聲特性理解時鐘器件作為合成器、抖動濾除功能時的噪聲特性。

2013-06-21 15:40:41 19925

19925

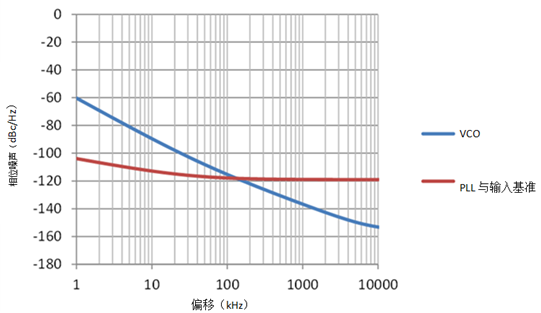

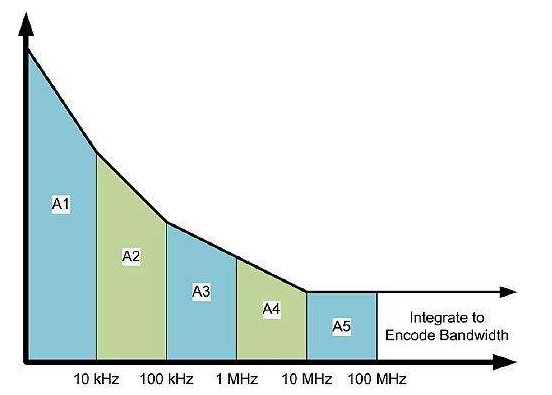

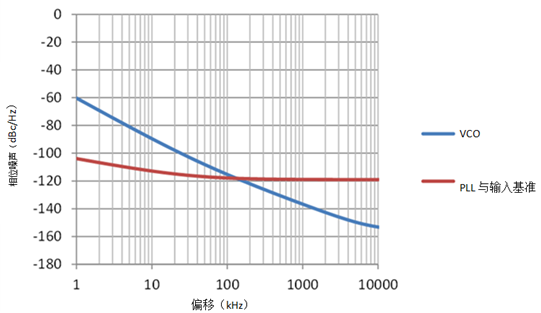

作為最重要的設計參數之一,選擇環路帶寬涉及到抖動、相位噪聲、鎖定時間或雜散之間的平衡。適合抖動的最優環路帶寬BWJIT也是數據轉換器時鐘等許多時鐘應用的最佳選擇。如果BWJIT并非最佳選擇,首先要做的仍是尋找最優環路帶寬。

2016-07-18 14:24:04 12191

12191

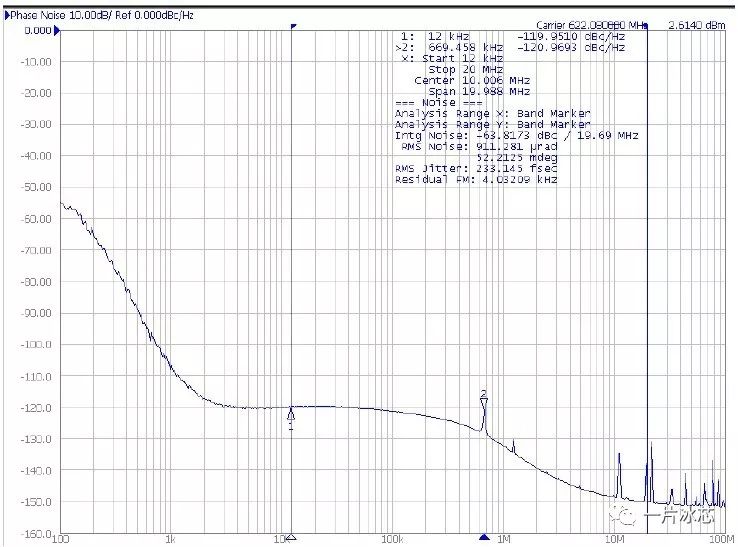

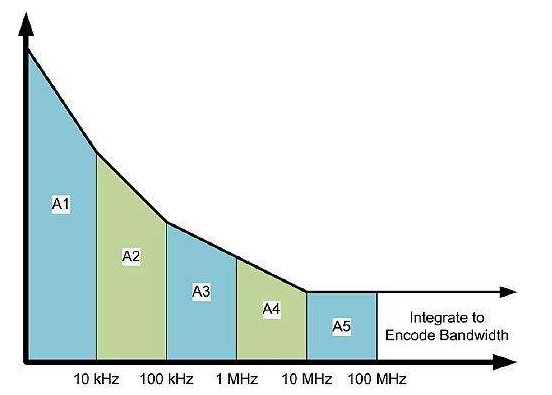

相位噪聲轉換到抖動的基本思想就是對相位噪聲曲線進行積分。

2023-10-30 16:06:01 7366

7366

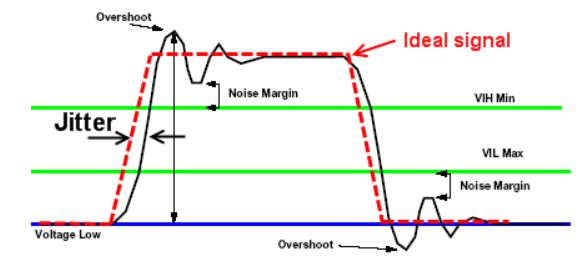

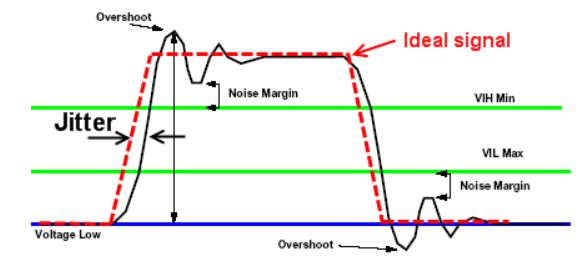

時鐘抖動是相對于理想時鐘沿實際時鐘存在不隨時間積累的、時而超前、時而滯后的偏移稱為時鐘抖動,簡稱抖動

2023-11-08 15:08:01 3278

3278

在高速光通信系統中,時鐘信號的相位穩定性與輸出結構決定了整個鏈路的同步能力與數據可靠性。傳統的CMOS單端輸出振蕩器難以滿足SerDes、CDR、PAM4調制等對低抖動與對稱輸出的要求。此背景下,集

2025-06-25 11:00:00 1837

1837

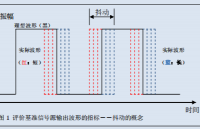

John Johnson 德州儀器 在本文中,我們將討論抖動傳遞及其性能,以及相位噪聲測量技術的局限性。 時鐘抖動和邊沿速率 圖1顯示了由一個通用公式表述的三種波形。該公式包括相位噪聲項“φ(t

2018-09-19 11:47:50

在本文中,我們將討論抖動傳遞及其性能,以及相位噪聲測量技術的局限性。 時鐘抖動和邊沿速率 圖1顯示了由一個通用公式表述的三種波形。該公式包括相位噪聲項“φ(t)”和幅度噪聲項“λ(t)。對評估的三個

2022-11-23 07:59:49

系統設計師通常側重于為應用選擇最合適的數據轉換器,在向數據轉換器提供輸入的時鐘發生器件的選擇上往往少有考慮。然而,如果不慎重考慮時鐘發生器的相位噪聲和抖動性能,數據轉換器動態范圍和線性度性能可能受到嚴重的影響。

2019-07-30 07:57:42

很多人都知道,抖動(這是時鐘邊沿不確定性)是不好的現象,其不僅可導致噪聲增加,而且還會降低數據轉換器的有效位數 (ENOB)。例如,如果系統需要 100MHz 14(最小值)位的 ENOB,我們

2022-11-21 07:26:27

作者:Richard Zarr很多人都知道,抖動(這是時鐘邊沿不確定性)是不好的現象,其不僅可導致噪聲增加,而且還會降低數據轉換器的有效位數 (ENOB)。例如,如果系統需要 100MHz 14

2018-09-13 14:18:06

我正在使用E5052B信號源分析儀來獲取相位噪聲數據,載波頻率為20.460802MHz,頻率范圍為1Hz至5MHz。我試圖將導出為.csv文件的相位噪聲數據轉換為RMS抖動(弧度),但是我在整個

2018-10-10 17:50:29

各位專家,我使用altera的cyclone5的DDR3硬核控制器,輸入時鐘是國產的125兆50PPM有源晶振,現在調試時發現對DDR3的讀寫偶爾出錯。我們測試DDR3接口的差分時鐘,發現左右抖動

2018-05-11 06:50:41

嗨,在ML605設計中,信號“PCIE_250M_MGT1_P / N”從器件“ICS874001”驅動到PCIe MGT參考時鐘。根據以下鏈接中給出的相位噪聲值,http

2020-06-08 15:30:33

大家好,我正在使用GTP進行項目。 GTP的時鐘在GTP SMA端口(2V5 LVPECL)。但是,MUX 4的輸出時鐘有一個影響GTP PLL鎖定狀態的抖動。有人幫我嗎?我做錯了什么?提前致謝!羅馬

2019-10-14 07:39:30

輸出信號波形穩定性的指標之一。英語的“Jitter”有神經過敏、緊張不安或激動的意思。在表現高頻石英振蕩器的穩定度時,指傳送數字信號時波形中產生的時間偏差和晃動。本次說明有關抖動和相位噪音的基礎知識

2018-04-12 16:02:30

&;ID = 2492 &;擺脫= 88149基于DDS的Verilog代碼。我的雙相的DDS的作品在一定程度上(演示項目附后),但顯示偶爾的相位翻轉在一定條件下180度,描述如下。我

2019-08-09 09:05:22

應用中的疑問:1、傳輸線為2~5米,產生的附加抖動易引起鎖相環失鎖嗎?鎖相環對輸入信號的抖動范圍有要求嗎?為保證輸出的200MHz時鐘穩定,鎖相環對輸入的時鐘信號有什么具體的要求?2、在鎖定的狀態下,若

2018-09-18 11:14:35

。抖動對系統穩定度的影響低噪聲KOAN晶振在精密電子儀器,無線電定位,高速目標跟蹤和宇航通信等領域十分重要,下面一組圖將說明抖動對系統穩定度的影響。假設有一個微處理器系統,其中處理器的時鐘上升前需要

2020-06-10 17:38:08

關于有源晶振的相位抖動和相位噪音

在通信網絡、無線傳輸、ATM和SONET等高速系統中,時鐘或振蕩器波形的時序誤差會限制一個數字I/O接口的最大速率。不僅如此,它還會導致通信鏈路的誤碼率增大,甚至

2023-12-14 09:19:08

時鐘頻率的不斷提高使相位噪聲和抖動在系統時序上占據日益重要的位置。本文介其概念及其對系統性能的影響,并在電路板級、芯片級和單元模塊級分別提供了減小相位噪聲和抖動的有效方法。

2019-06-05 07:13:30

于相位噪聲、鎖定時間或雜散卻并非如此。表1給出了環路帶寬對這些性能指標的影響的大致參考。 性能指標最優帶寬備注抖動BWJIT最優值一般為BWJIT。在低集成限制更高的一些情況下,有時較窄的環路帶寬實際上效果更好。鎖定時間無限VCO鎖定時間隨著環路帶寬的增加而提高,但有時會受到VCO校準時間…

2022-11-16 07:56:45

一般考量采樣時鐘抖動對ADC ENOB的影響都是用相位噪聲的隨機抖動Rj計算,想請教周期性抖動例如電源上的抖動造成時鐘的Dj對 ENOB有影響嗎?如何計算這部分的影響?

2024-11-13 08:15:51

什么是抖動和相位噪聲?如何區分抖動和相位噪聲?

2021-03-11 07:03:13

假設您已經通過迭代信息傳遞相位邊限和回路帶寬在鎖相環(PLL)上花費了一些時間。但遺憾地是,還是無法在相位噪聲、雜散和鎖定時間之間達成良好的平衡。感到泄氣?想要放棄?等一下!你是否試過伽馬優化參數?

2019-07-31 07:26:15

高信噪比=低ADC孔徑抖動嗎?在設計中,為了避免降低ADC的性能,工程師一般會采用抖動極低的采樣時鐘。然而,用于產生采樣時鐘的振蕩器常常用相位噪聲而非時間抖動來描述特性。那么,有木有方法將振蕩器相位噪聲轉換為時間抖動呢?

2019-08-13 06:27:54

隨著通信系統中的時鐘速度邁入GHz級,相位噪聲和抖動這兩個在模擬設計中十分關鍵的因素,也開始在數字芯片和電路板的性能中占據日益重要的位置。在高速系統中,時鐘或振蕩器波形的時序誤差會限制一個數字I/O

2009-10-13 17:23:19

需求。作為該最新博客系列的開篇文章,我將幫助您了解如何正確測量時鐘緩沖器的附加抖動。為什么抖動很重要?在當今數據通信、有線及無線基礎設施以及其它高速應用等高級系統中,時鐘抖動是整體系統性能的關鍵因素。要

2018-09-13 14:38:43

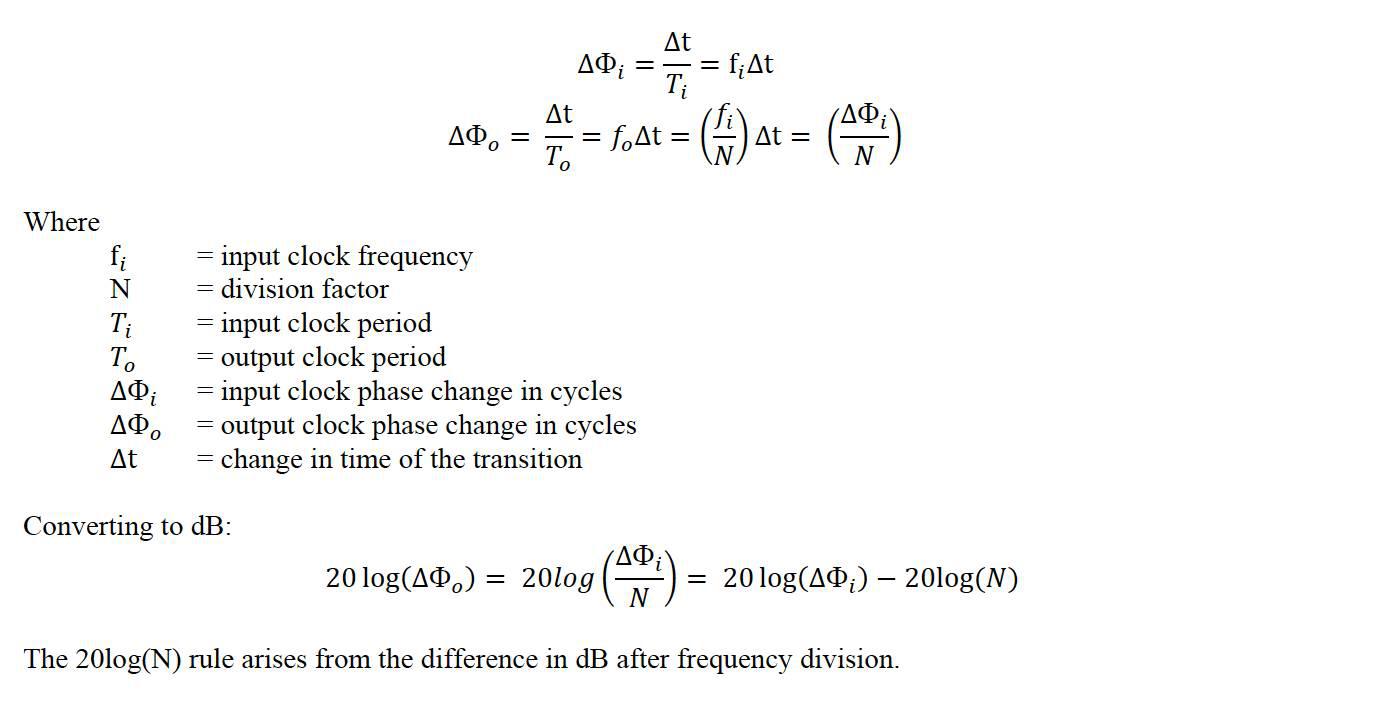

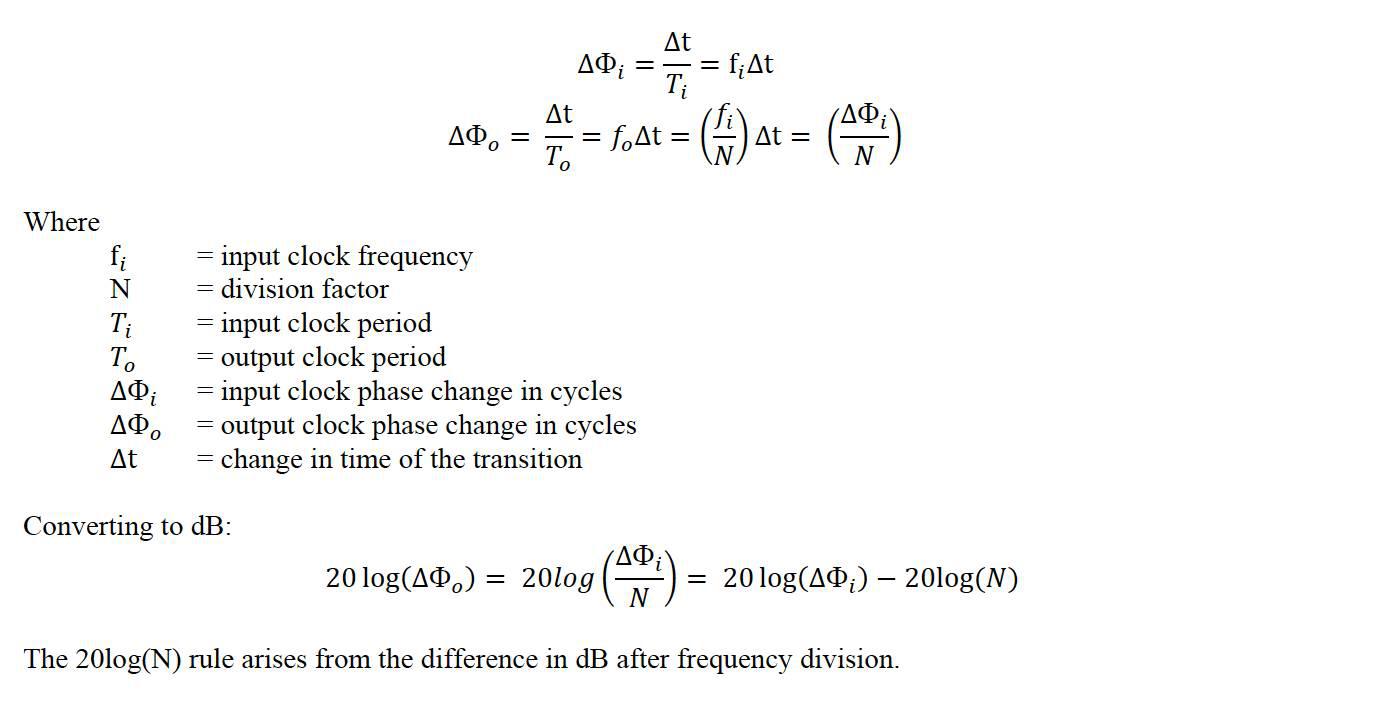

本期我將討論在測量較低時鐘頻率的相位噪聲和相位抖動時出現的一個非常常見的問題。在所有條件相同的情況下,我們通常期望分頻的低頻時鐘產生比高頻時鐘更低的相位噪聲。在數量上,你可能會記得這是20log(N

2021-06-24 07:30:00

電動助力轉向系統EPS(electricpowersteering)是一種直接依靠電機提供輔助扭矩的動力轉向系統,與傳統的液壓助力轉向系統HPS(hydraulicpowersteering)相比

2019-10-16 06:16:06

最近調試有兩個問題需要您釋疑: 1.9548有頻率鎖定和相位鎖定。兩者之間有關系嗎?鎖定有無先后順序的要求? 2.在9548頻率和相位都鎖定之后,9548還是在不停的校準,為什么還會時不時的失去鎖定,這是什么原因?配置問題嗎?謝謝!

2018-09-05 11:45:27

作為最重要的設計參數之一,選擇環路帶寬涉及到抖動、相位噪聲、鎖定時間或雜散之間的平衡。適合抖動的最優環路帶寬BWJIT也是數據轉換器時鐘等許多時鐘應用的最佳選擇。如果BWJIT并非最佳選擇,首先要

2018-08-29 16:02:55

本文主要討論采樣時鐘抖動對ADC 信噪比性能的影響以及低抖動采樣時鐘電路的設計。

2009-11-27 11:24:07 15

15 隨著支持直接IF采樣的更高分辨率數據轉換器的上市,系統設計師在選擇低抖動時鐘電路時,需要在性能/成本之間做出權衡取舍。許多用于標定時鐘抖動的傳統方法都不適用于數

2010-11-27 17:12:46 33

33

雙調諧回路中頻放大電路

2008-12-15 17:38:29 1338

1338

摘要:這是一篇關于時鐘(CLK)信號質量的應用筆記,介紹如何測量抖動和相位噪聲,包括周期抖動、逐周期抖動和累加抖動。本文還描述了周期抖動和相位噪聲譜之間的關系,并介紹

2009-04-22 10:16:50 4761

4761

正反饋回路和非最小相位系統根軌跡

2009-07-27 14:22:56 4477

4477 AD9547 具有高出66%的抖動性能、100倍的更窄回路濾波器帶寬的時鐘器件

AD9552能夠替代包括OCXO(恒溫

2009-09-01 17:28:35 1222

1222 相位噪聲和抖動的概念及其估算方法

時鐘頻率的不斷提高使相位噪聲和抖動在系統時序上占據日益重要的位置。本文介其概念及其對系統性能的影

2009-12-27 13:30:21 3180

3180

理解不同類型的時鐘抖動

抖動定義為信號距離其理想位置的偏離。本文將重點研究時鐘抖動,并探討下面幾種類型的時鐘抖動:相鄰周期抖動、周期抖動、時間間隔誤

2010-01-06 11:48:11 2094

2094

模數和數模轉換器采樣時鐘內的抖動會對可實現的最大信噪比造成限制(參見參考文獻部分van de Plassche著《集成模數和數模轉換器》)。本應用筆記闡述了相位噪聲和抖動的定義,繪制

2011-11-24 14:31:55 75

75 采用CD4046和AD630設計了一個雙相位鎖相放大器,并進行了實驗驗證,實驗驗證結果表明,該放大器可以測量1 mA以下的交流電流,靈敏度為20 mV/mA,精度0.05%,是一種高精度、實用型鎖相放大電路。

2012-03-23 10:59:17 175

175 時鐘抖動時域分析(下):

2012-05-08 15:26:25 29

29 如果明智地選擇時鐘,一份簡單的抖動規范幾乎是不夠的。而重要的是,你要知道時鐘噪聲的帶寬和頻譜形狀,才能在采樣過程中適當地將它們考慮進去。很多系統設計師對數據轉換器

2012-05-08 15:29:00 47

47 雙相時鐘脈電路.ms8

2012-07-16 23:10:28 48

48 設計人員可以通過控制器的開關頻率抖動,減少一個脈沖寬度調制(PWM)控制器的電磁干擾(EMI)分布中頻譜分量的峰值幅度。時鐘抖動擴頻技術并非意在取代傳統的EMI降低技術,但它們與傳統技術的結合使用,可以減少系統中的EMI分布。它們還可以利用減少通過某些排放標準所需的屏蔽和濾波量來降低成本。

2013-02-19 14:07:10 3441

3441

業內大多數FPGA 均提供數字時鐘管理( 賽靈思公司的全部FPGA 均具有這種特性)。賽靈思公司推出最先進的FPGA 提供數字時鐘管理和相位環路鎖定。相位環路鎖定能夠提供精確的時鐘綜合,且能夠降低抖動,并實現過濾功能。

2017-02-11 17:01:11 2173

2173

介紹 此應用筆記側重于不同類型的時鐘抖動。時鐘抖動是從它的時鐘邊沿偏差理想的位置。了解時鐘抖動非常重要在應用中,因為它起著關鍵作用,在時間預算一個系統。 隨著系統數據速率的增加,定時抖動成為關鍵

2017-04-01 16:13:18 6

6 很多人都知道,抖動(這是時鐘邊沿不確定性)是不好的現象,其不僅可導致噪聲增加,而且還會降低數據轉換器的有效位數 (ENOB)。例如,如果系統需要 100MHz 14(最小值)位的 ENOB,我們

2017-04-08 04:51:23 1767

1767

采樣時鐘抖動可對高性能ADCs信噪比性能的災難。雖然信噪比和抖動之間的關系是眾所周知的,但是大多數振蕩器都是根據相位噪聲來指定的。

2017-08-03 10:57:33 13

13 當PLL參考時鐘和PLL反饋時鐘的頻率和相位相匹配時,PLL則被稱為是鎖定狀態。達到鎖定狀態所需的時間稱為鎖定時間,這是PLL設計最關鍵的參數之一。

2018-03-14 15:17:00 7951

7951

本文介紹了一種通過單邊帶來估計時鐘源的相位噪聲的通用公式。載波比(SSCR),振蕩周期的周期抖動。該鏈接允許無縫聚合。

外部時鐘源相位噪聲,通常以dBC/Hz給出,與片上時鐘同步電路的相位穩定圖

2018-05-16 17:56:54 6

6 如果一個時鐘的載波頻率下降了N倍,那么我們預計相位噪聲會減少20log(N)。例如,每個除以因子2的除法應該導致相位噪聲減少20log(2)或大約6dB。這里的主要假設是無噪聲的傳統數字分頻器。

2018-09-28 08:14:00 12629

12629

時鐘設計人員通常會提供一個相位噪聲,但不提供抖動規格。相位噪聲規格可以轉換為抖動,首先確定時鐘噪聲,然后通過小角度計算將噪聲與主時鐘噪聲成分進行比較。相位噪聲功率通過計算圖9中的灰色區域積分得出。

2019-08-20 11:06:53 9314

9314

時鐘抖動性能主題似乎是時鐘,ADC和電源的當前焦點供應廠家。理由很清楚;時鐘抖動會干擾包括高速ADC在內的數字電路的性能。高速時鐘可以對它們所接收的功率的“清潔度”非常敏感,盡管量化關系需要一些努力。

2019-09-14 11:24:00 9399

9399

電子發燒友網為你提供測量較低時鐘頻率的相位噪聲和相位抖動資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-03-27 08:40:37 10

10 電子發燒友網為你提供為什么雜散會帶來額外抖動?時鐘相位噪聲測量解析資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-02 08:55:37 6

6 電子發燒友網為你提供相位噪聲處理:時鐘抖動或結束時鐘抖動的最佳方法是什么?資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-04 08:49:06 26

26 超低抖動時鐘的產生與分配

2021-04-18 14:13:51 8

8 LTC6950:1.4 GHz低相位噪聲、低抖動鎖相環,帶時鐘分布數據表

2021-04-19 12:13:04 3

3 作為最重要的設計參數之一,選擇環路帶寬涉及到抖動、相位噪聲、鎖定時間或雜散之間的平衡。適合抖動的最優環路帶寬BWJIT也是數據轉換器時鐘等許多時鐘應用的最佳選擇。如果BWJIT并非最佳選擇,首先要

2022-01-11 16:00:28 3269

3269 發現抖動、相位噪聲、鎖定時間或雜散問題?請檢查鎖相環的環路濾波器帶寬

2022-11-02 08:16:24 15

15 時鐘采樣系統最大限度減少抖動

2022-11-04 09:52:12 0

0 時鐘抖動使隨機抖動和相位噪聲不再神秘

2022-11-07 08:07:29 4

4 時鐘抖動解秘—高速鏈路時鐘抖動規范基礎知識

2022-11-07 08:07:30 2

2 在設計中使用超快速數據轉換器的高速應用通常需要非常干凈的時鐘信號,以確保外部時鐘源不會對系統的整體動態性能產生不需要的噪聲。因此,選擇合適的系統組件至關重要,這有助于產生低相位抖動時鐘。以下應用筆記可作為選擇合適的元件的寶貴指南,以設計適用于超快速數據轉換器的基于PLL的低相位噪聲時鐘發生器。

2023-02-25 10:50:48 4207

4207

采用PLL的時鐘發生器廣泛用于網絡設備中,用于生成高精度和低抖動參考時鐘或保持同步網絡操作。大多數時鐘振蕩器使用理想、干凈的電源給出其抖動或相位噪聲規格。然而,在實際的系統環境中,電源可能會因板載開關電源或嘈雜的數字ASIC而受到干擾。為了在系統設計中實現最佳性能,了解這種干擾的影響非常重要。

2023-03-08 15:33:00 2184

2184

抖動和相位噪聲是晶振的非常重要指標,本文主要從抖動和相位噪聲定義及原理出發,闡述其在不同場景下對數字系統、高速串行接口、數據轉換器和射頻系統的影響。 1.?抖動和相位噪聲 1.1.?抖動

2023-03-10 14:54:32 1847

1847

抖動和相位噪聲是晶振的非常重要指標,本文主要從抖動和相位噪聲定義及原理出發,闡述其在不同場景下對數字系統、高速串行接口、數據轉換器和射頻系統的影響。

2023-03-26 09:09:11 1867

1867

系統時序設計中對時鐘信號的要求是非常嚴格的,因為我們所有的時序計算都是以恒定的時鐘信號為基準。但實際中時鐘信號往往不可能總是那么完美,會出現抖動(Jitter)和偏移(Skew)問題。

2023-04-04 09:20:56 5281

5281 作為最重要的設計參數之一,選擇環路帶寬涉及到抖動、相位噪聲、鎖定時間或雜散之間的平衡。適合抖動的最優環路帶寬BWJIT也是數據轉換器時鐘等許多時鐘應用的最佳選擇。如果BWJIT并非最佳選擇,首先要做的仍是尋找最優環路帶寬。

2023-04-12 10:32:17 3831

3831

) 頻帶內和頻帶外 (VCO) 噪聲的影響。基準時鐘發生器的相位噪聲性能需要在PLL環路帶寬內和帶寬外都表現得很出色,以符合更加嚴格的抖動技術規格要求。

2023-04-17 10:37:30 1249

1249

理想值附近的一個范圍內,從而造成相鄰的時鐘邊沿存在偏差。在時序分析時,時鐘抖動是一個重要的因素。多種因素會導致時鐘抖動,包括PLL回路噪聲、電源紋波、熱噪聲以及信號之間的串擾等。

2023-06-09 09:40:50 3109

3109

這是為數不多的跨越圍欄是有利的情況之一。目前市面上的許多時鐘產品都指定器件的相位噪聲,而不指定抖動。讓我們來看看如何從相位噪聲變為抖動。然后,我們將能夠預測具有一定抖動的ADC的SNR。一個例子將不得不等待,因為我在這里只有這么多空間。現在讓我們專注于數學。下圖顯示了我們如何根據時鐘源的相位噪聲計算抖動。

2023-06-30 16:58:01 1811

1811

本文主要介紹了時鐘偏差和時鐘抖動。

2023-07-04 14:38:28 3231

3231

相噪是與哪種類型的抖動相對應?如何理解相位噪聲與時間抖動的關系? 相位噪聲與時間抖動是兩個在信號處理領域中經常涉及的概念。在討論相位噪聲時,我們常常聽到相位噪聲和時間抖動的聯系。因此,本文將探討相位

2023-10-20 15:08:11 2180

2180 相位噪聲和抖動是對時鐘頻譜純度的兩種表述形式,一個是頻域一個是時域,從原理上來說,它們是等效的。

2023-10-30 16:02:46 4314

4314

抖動是相位抖動的主要原因之一。在通信系統中,時鐘扮演著非常重要的角色,它確定了信號的采樣時間和傳輸速率。然而,由于各種原因,包括晶體振蕩器的溫度變化、電力供應的不穩定、電磁干擾等,時鐘信號會產生偏移和抖動,導

2024-01-25 15:29:28 2314

2314 ,包括電路穩定性不良、時鐘補償誤差、溫度變化、電磁干擾等。相位噪聲對信號有著廣泛的影響,包括降低信號的頻譜純度、引起功率泄露、產生頻率副瓣、導致系統誤碼率的提高等。 抖動是指信號的周期性變化,通常表現為時間軸上信號

2024-01-29 13:54:34 2335

2335 相位噪聲與時間抖動有何關系?如何測試時間抖動? 相位噪聲和時間抖動在信號處理中是兩個非常重要的概念。它們都是衡量信號或系統的穩定性和準確性的指標。雖然它們在一些方面是相關的,但它們也有一些不同之處

2024-01-31 09:29:00 1918

1918 隨著數據傳輸速率的不斷提升,時鐘信號的抖動分析變得越來越重要。在Gb/s范圍,任何一個小的抖動都會對系統性能造成顯著影響。

2024-05-15 16:09:34 2487

2487 EPSON(愛普生)-抖動與相位噪音

2024-06-20 10:07:20 940

940

時鐘抖動(Clock Jitter)是時鐘信號領域中的一個重要概念,它指的是時鐘信號時間與理想事件時間的偏差。這種偏差不僅影響數字電路的時序性能,還可能對系統的穩定性和可靠性造成不利影響。以下是對時鐘抖動工作原理的詳細闡述,內容將圍繞其定義、類型、產生原因、影響及應對措施等方面展開。

2024-08-19 17:58:11 5343

5343 在FPGA(現場可編程門陣列)設計中,消除時鐘抖動是一個關鍵任務,因為時鐘抖動會直接影響系統的時序性能、穩定性和可靠性。以下將詳細闡述FPGA中消除時鐘抖動的多種方法,這些方法涵蓋了從硬件設計到軟件優化的各個方面。

2024-08-19 17:58:54 3756

3756 時鐘抖動和相位噪聲是數字系統和通信系統中兩個至關重要的概念,它們之間存在著緊密而復雜的關系。以下是對時鐘抖動和相位噪聲關系的詳細探討,旨在全面解析兩者之間的相互作用和影響。

2024-08-19 18:01:57 2380

2380 時鐘抖動(Jitter)和時鐘偏移(Skew)是數字電路設計中兩個重要的概念,它們對電路的時序性能和穩定性有著顯著的影響。下面將從定義、原因、影響以及應對策略等方面詳細闡述時鐘抖動和時鐘偏移的區別。

2024-08-19 18:11:30 3230

3230 通過上一期我們了解到:數字電子產品中電源軌噪聲和時鐘抖動是有關聯的,以及測量電源軌噪聲的方案,接下來我們基于實際測量,揭示電源軌噪聲對系統時鐘抖動的影響。

2024-11-22 16:11:22 1176

1176

鎖定時鐘倍頻器具有低抖動多相時鐘產生、緊湊布局、高能效和高魯棒性等優勢,成為有線收發機系統中多相時鐘產生的有效解決方案。但注入鎖定時鐘倍頻器面臨固有注入相位誤差、最優注入脈沖寬度及其隨PVT變化的漂移等挑戰,限制

2025-01-15 14:24:41 893

893

一、相位與相位噪聲相位(Phase):交流信號表達式A*sin(2πft+φ)中的φ為相位,描述的是“波形在時間軸上的位置”,它是一個瞬時量,單位是弧度(rad)。圖1正弦信號的相位在實際系統中

2025-08-15 17:22:36 2502

2502

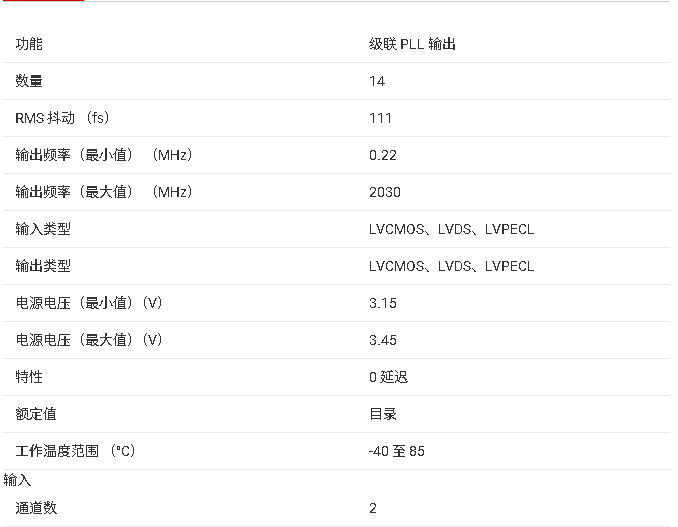

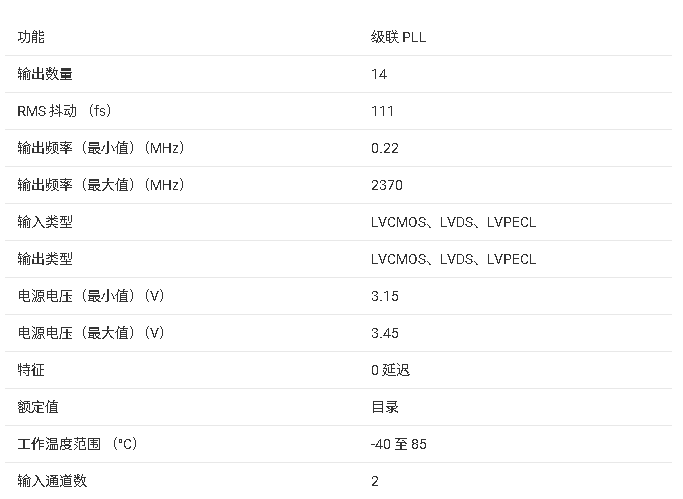

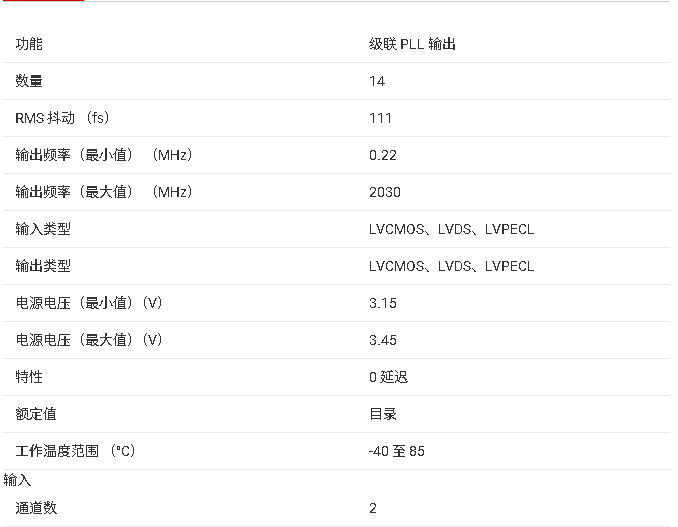

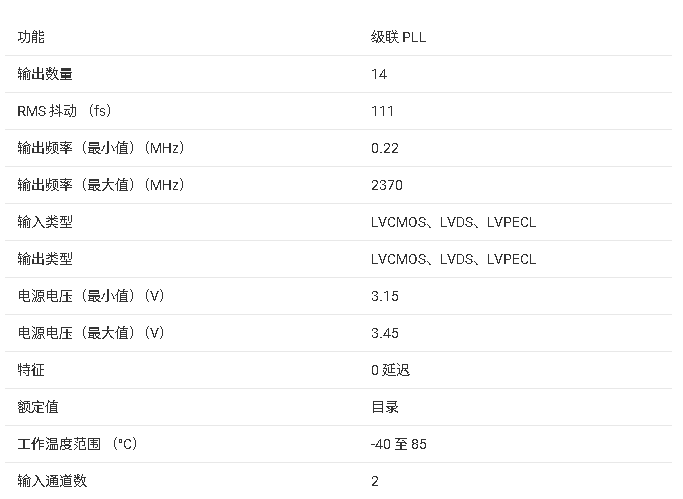

LMK0480x 系列是業界性能最高的時鐘調節器,具有卓越的 時鐘抖動清理、生成和分配,具有滿足下一代需求的高級功能 系統要求。雙回路PLLatinum 該架構能夠使用低噪聲VCXO模塊實現111

2025-09-16 10:37:21 687

687

LMK0480x 系列是業界性能最高的時鐘調節器,具有卓越的 時鐘抖動清理、生成和分配,具有滿足下一代需求的高級功能 系統要求。雙回路PLLatinum 該架構能夠使用低噪聲VCXO模塊實現111

2025-09-16 10:42:44 728

728

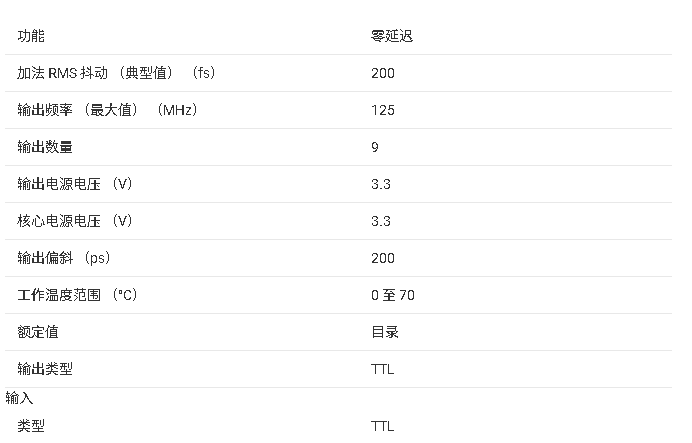

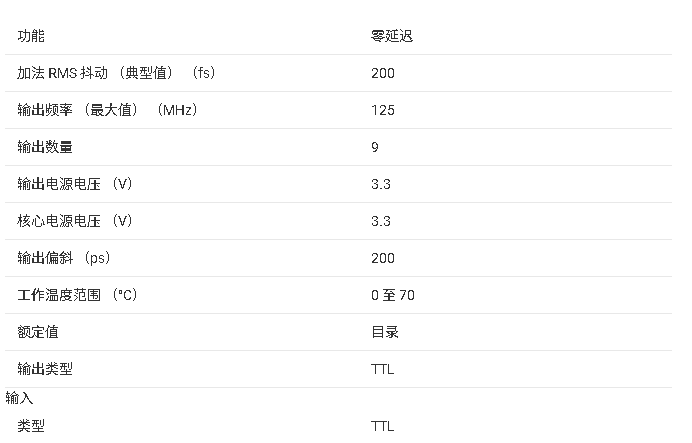

CDC509 是一款高性能、低偏斜、低抖動、鎖相環 (PLL) 時鐘驅動器。它使用 PLL 在頻率和相位上將反饋 (FBOUT) 輸出精確對齊到時鐘 (CLK) 輸入信號。它專為與同步 DRAM 一起使用而設計。CDC509 的工作電壓為 3.3V V~CC~設計用于驅動每個輸出多達五個時鐘負載。

2025-09-23 10:09:13 796

796

電子發燒友App

電子發燒友App

評論