電子發(fā)燒友網(wǎng)>模擬技術(shù)>接口/時(shí)鐘/PLL>

接口/時(shí)鐘/PLL

電子發(fā)燒友網(wǎng)接口/時(shí)鐘/PLL欄目提供pll鎖相環(huán),鎖相環(huán),鎖相環(huán)電路,鎖相環(huán)原理,數(shù)字鎖相環(huán)等接口/時(shí)鐘/PLL設(shè)計(jì)所需的所有最新行業(yè)新聞、產(chǎn)品信息及技術(shù)熱點(diǎn)方案及介紹。瀾起科技推出支持9200 MT/s速率的DDR5時(shí)鐘驅(qū)動(dòng)器(CKD)芯片

瀾起科技今日正式推出新一代DDR5時(shí)鐘驅(qū)動(dòng)器(CKD)芯片,該芯片最高支持9200 MT/s的數(shù)據(jù)傳輸速率,可有效優(yōu)化客戶端內(nèi)存子系統(tǒng)性能,為下一代高性能PC、筆記本電腦及工作站提供關(guān)鍵技術(shù)支撐。...

2025-11-10 標(biāo)簽:DRAM瀾起科技時(shí)鐘驅(qū)動(dòng)器DDR5 1605

詳解配置控制器局域網(wǎng)絡(luò)(CAN)位時(shí)序?qū)崿F(xiàn)系統(tǒng)性能優(yōu)化

隔離有利于提高魯棒性,但同時(shí)也會(huì)增加發(fā)射和接收兩個(gè)方向的傳播延遲。必須使該延遲增加一倍,以支持兩個(gè)節(jié)點(diǎn)參與仲裁。如果系統(tǒng)允許的傳播延遲是固定的,在增加隔離措施之后,可以減...

2024-11-15 標(biāo)簽:CAN時(shí)序CAN收發(fā)器adm3052CANCAN收發(fā)器局域網(wǎng)絡(luò)時(shí)序 2506

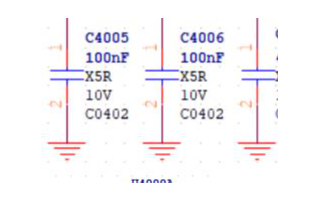

eMMC模塊電路的PCB設(shè)計(jì)建議

eMMC電路簡(jiǎn)介 eMMC(Embedded Multi Media Card)是MMC協(xié)會(huì)訂立、主要針對(duì)手機(jī)或平板電腦等產(chǎn)品的內(nèi)嵌式存儲(chǔ)器標(biāo)準(zhǔn)規(guī)格。 eMMC在封裝中集成了一個(gè)控制器,提供標(biāo)準(zhǔn)接口并管理閃存。原理電路8位數(shù)據(jù)...

2023-08-17 標(biāo)簽:PCB設(shè)計(jì)時(shí)鐘emmcRK3588emmcPCB布線PCB設(shè)計(jì)RK3588上拉下拉電阻上拉電阻下拉電阻華秋電路多層板時(shí)鐘模塊電路 112998

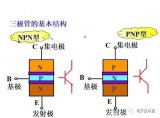

三極管開關(guān)電路驅(qū)動(dòng)電阻如何選擇

當(dāng)三極管基極偏置電壓小于PN結(jié)的導(dǎo)通電壓,基極電流Ib=0時(shí),集電極Ic和發(fā)射極Ie沒電流(或只有微弱的弱電電流)通過,此時(shí)三極管失去了電流放大作用,我們稱三極管工作在截止?fàn)顟B(tài),...

2023-08-10 標(biāo)簽:三極管開關(guān)電路電流控制器三極管開關(guān)電路電流控制器驅(qū)動(dòng)電阻 1725

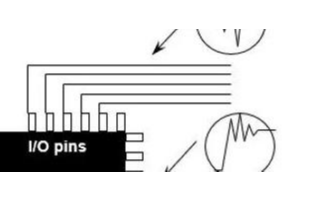

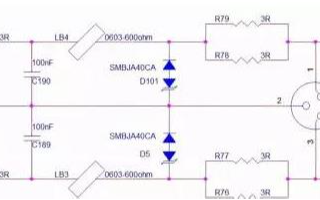

如何為逐次逼近型ADC設(shè)計(jì)可靠的數(shù)字接口?

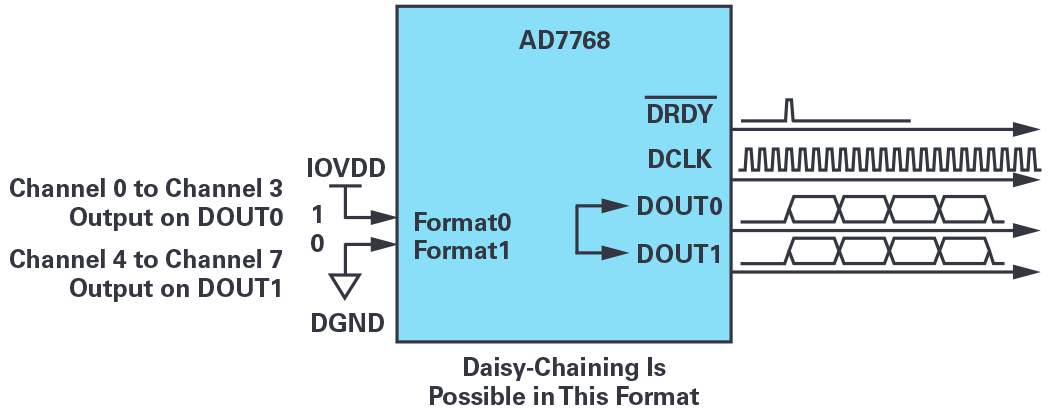

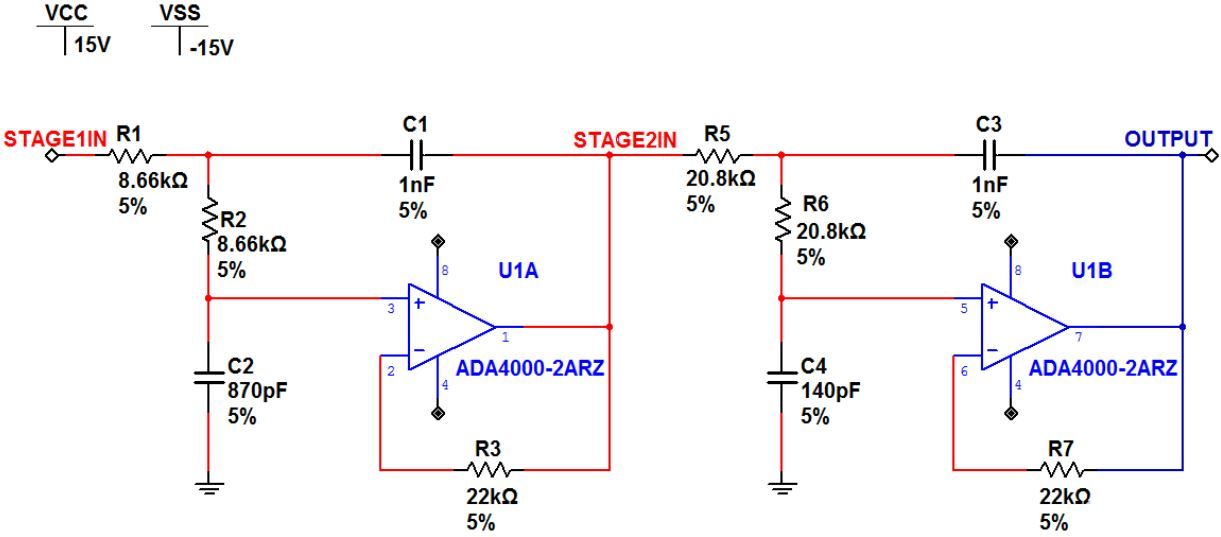

逐次逼近型模數(shù)轉(zhuǎn)換器(因其逐次逼近型寄存器而稱為SAR ADC)廣泛運(yùn)用于要求最高18 位分辨率和最高5 MSPS 速率的應(yīng)用中。其優(yōu)勢(shì)包括尺寸小、功耗低、無流水線延遲和易用。 主機(jī)處理器可以通...

2023-07-20 標(biāo)簽:寄存器adc模數(shù)轉(zhuǎn)換器亞德諾adcADCSAR ADC亞德諾寄存器模數(shù)轉(zhuǎn)換器 2124

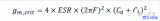

PCB上晶體振蕩電路的設(shè)計(jì)

今天主要給大家簡(jiǎn)單介紹一下:PCB 上晶體振蕩電路的設(shè)計(jì)。...

2023-07-18 標(biāo)簽:電路圖pcb電路設(shè)計(jì)振蕩電路ESR晶體振蕩器ESRpcbPCB振蕩電路晶體振蕩器晶體振蕩電路電路圖電路設(shè)計(jì) 1891

模擬鎖相環(huán)和數(shù)字鎖相環(huán)區(qū)別

模擬鎖相環(huán)和數(shù)字鎖相環(huán)的主要區(qū)別在于它們的控制方式不同。模擬鎖相環(huán)是通過模擬電路來控制頻率和相位,而數(shù)字鎖相環(huán)是通過數(shù)字信號(hào)處理技術(shù)來控制頻率和相位。此外,模擬鎖相環(huán)的精...

2023-02-15 標(biāo)簽:數(shù)字鎖相環(huán)模擬鎖相環(huán) 6434

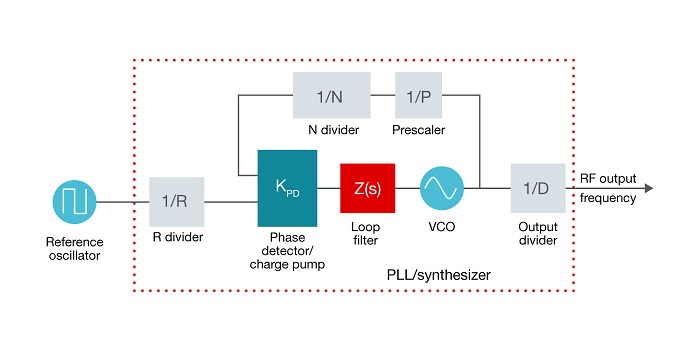

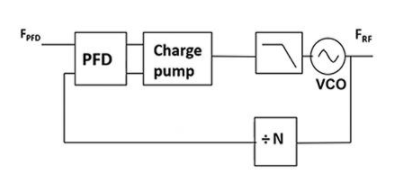

pll是什么意思_pll鎖相環(huán)參數(shù)

PLL是指鎖相環(huán),是一種用于控制頻率和相位的電路,它可以將一個(gè)輸入信號(hào)的頻率和相位轉(zhuǎn)換成另一個(gè)輸出信號(hào)的頻率和相位,從而實(shí)現(xiàn)頻率和相位的控制。...

pll鎖相環(huán)版圖設(shè)計(jì)注意

PLL鎖相環(huán)版圖設(shè)計(jì)時(shí)應(yīng)注意以下幾點(diǎn):1)確定PLL的頻率范圍;2)確定PLL的控制電路;3)確定PLL的調(diào)節(jié)電路;4)確定PLL的輸出電路;5)確定PLL的濾波電路;6)確定PLL的控制參數(shù);7)確定PLL的...

幾款常用的保護(hù)電路

? 鑒于電源電路存在一些不穩(wěn)定因素,而設(shè)計(jì)用來防止此類不穩(wěn)定因素影響電路效果的回路稱作保護(hù)電路。在各類電子產(chǎn)品中,保護(hù)電路比比皆是,例如:過流保護(hù)、過壓保護(hù)、過熱保護(hù)、空載...

對(duì)比機(jī)電繼電器 干簧管有哪些優(yōu)勢(shì)

磁簧開關(guān)(Reed Switch)也稱之為干簧管,它是一個(gè)通過所施加的磁場(chǎng)操作的電開關(guān)。磁簧開關(guān)是由兩片磁***(通常由鐵和鎳這兩種金屬所組成的)?密封在玻璃管內(nèi)。?兩片磁***呈重迭狀況但中間間隔...

2023-02-06 標(biāo)簽:干簧管磁簧開關(guān)干簧管磁場(chǎng)磁簧開關(guān) 2033

FPGA物理約束-網(wǎng)表約束CLOCK_DEDICATED_ROUTE

Vivado工具在編譯時(shí)通常會(huì)自動(dòng)識(shí)別設(shè)計(jì)中的時(shí)鐘網(wǎng)絡(luò),并將其分配到專用的時(shí)鐘布局布線資源中。...

2022-10-24 標(biāo)簽:FPGAFPGA圖像數(shù)據(jù)時(shí)鐘網(wǎng)絡(luò) 4277

時(shí)序分析中的一些基本概念

時(shí)序分析是FPGA設(shè)計(jì)中永恒的話題,也是FPGA開發(fā)人員設(shè)計(jì)進(jìn)階的必由之路。慢慢來,先介紹時(shí)序分析中的一些基本概念。...

2022-10-21 標(biāo)簽:FPGAFPGA時(shí)序分析時(shí)鐘信號(hào) 3822

jitter的關(guān)鍵術(shù)語和參數(shù)

時(shí)鐘電路是芯片中最基礎(chǔ)的電路,時(shí)鐘電路性能的好壞關(guān)乎SoC中所有電路能否達(dá)到預(yù)期目標(biāo),例如:計(jì)算核(CPU/GPU/NPU)的主頻,DDR的帶寬,高速接口(PCIE)的帶寬等。...

SPI接口說明及原理

最基本的SPI通信就是一主一從,比如:一個(gè)STM32作為主機(jī),一個(gè)W25Q16(SPI Flash)作為從機(jī)。還有兩個(gè)MCU之間進(jìn)行SPI通信等。...

為什么組件集成對(duì)天基PLL合成器很重要

通過將射頻和合成器組件集成到單片射頻 IC 中,工程師可以解決星載應(yīng)用中的尺寸和復(fù)雜性設(shè)計(jì)挑戰(zhàn)...

如何從時(shí)序分析中排除跨時(shí)鐘域路徑?

要從時(shí)序分析刪除一組路徑,如果您確定這些路徑不會(huì)影響時(shí)序性能(False 路徑),可用FROM-TO 約束以及時(shí)序忽略 (TIG) 關(guān)鍵字。...

傳統(tǒng) PLL 與平移環(huán)系統(tǒng)級(jí)封裝技術(shù)

低噪聲平移環(huán)的設(shè)計(jì)涉及眾多電路塊的實(shí)現(xiàn),導(dǎo)致設(shè)計(jì)復(fù)雜,通常體積龐大,靈活性有限。此外,整個(gè)電路必須針對(duì)目標(biāo)操作進(jìn)行驗(yàn)證和特征化。...

2022-07-28 標(biāo)簽:pll混頻器壓控振蕩器信號(hào)發(fā)生器電壓穩(wěn)壓器 1697

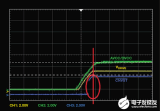

如何降低地彈噪聲對(duì)單板信號(hào)完整性影響

本文結(jié)合某單板(下文中統(tǒng)一稱M單板)FPGA調(diào)試過程中發(fā)現(xiàn)地彈噪聲造成某重要時(shí)鐘信號(hào)劣化從而導(dǎo)致單板業(yè)務(wù)丟包的故障,來談下如何最大程度地降低地彈噪聲對(duì)單板信號(hào)完整性影響。...

2022-07-27 標(biāo)簽:FPGA時(shí)鐘信號(hào)FPGA地彈時(shí)鐘信號(hào) 1429

帶有時(shí)鐘使能和同步清零的D觸發(fā)器

每個(gè) Slice 有 8 個(gè) FF 。四個(gè)可以配置為 D 型觸發(fā)器或電平敏感鎖存器,另外四個(gè)只能配置為 D 型觸發(fā)器,但是需要記得是:當(dāng)原來的四個(gè) FF 配置為鎖存器時(shí),不能使用這四個(gè) FF 。...

2022-07-22 標(biāo)簽:數(shù)據(jù)時(shí)鐘觸發(fā)器 4488

i.MXRT1170 的時(shí)鐘架構(gòu)

目前 i.MXRT1xxx 系列主要分為 i.MX RT10xx 和 i.MXRT11xx 兩大分支。這兩個(gè)分支的時(shí)鐘系統(tǒng)設(shè)計(jì)是有一些差異的,不過總體來說,架構(gòu)差別不大,我們以如下 i.MXRT1170 的時(shí)鐘架構(gòu)為例來具體介紹。...

2022-07-08 標(biāo)簽:寄存器引腳寄存器引腳時(shí)鐘系統(tǒng) 1261

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語言教程專題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動(dòng)駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺 | 無人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國(guó)民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |