作為最重要的設計參數之一,選擇環路帶寬涉及到抖動、相位噪聲、鎖定時間或雜散之間的平衡。適合抖動的最優環路帶寬BWJIT也是數據轉換器時鐘等許多時鐘應用的最佳選擇。如果BWJIT并非最佳選擇,首先要做的仍是尋找最優環路帶寬。

圖1中,鎖相環(PLL)與壓控振蕩器(VCO)噪聲交叉處的偏移,BWJIT(約為140kHz)通過減少曲線下方的面積來優化抖動。

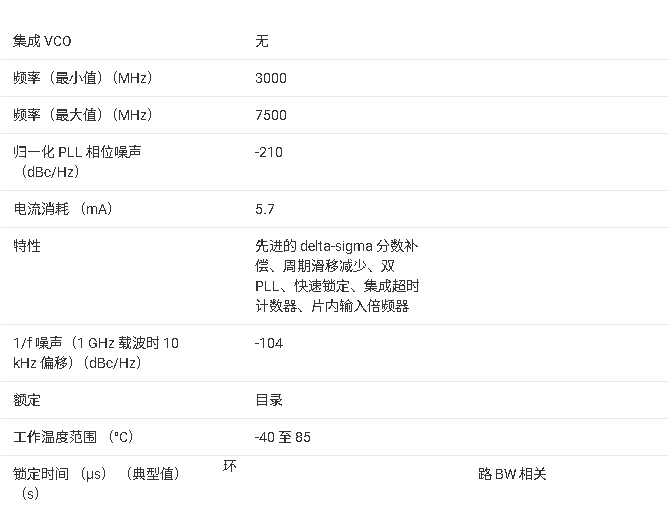

盡管此帶寬BWJIT對抖動而言是最優的,但對于相位噪聲、鎖定時間或雜散卻并非如此。表1給出了環路帶寬對這些性能指標的影響的大致參考。

| 性能指標 | 最優帶寬 | 備注 |

| 抖動 | BWJIT | 最優值一般為BWJIT。在低集成限制更高的一些情況下,有時較窄的環路帶寬實際上效果更好。 |

| 鎖定時間 | 無限 | VCO鎖定時間隨著環路帶寬的增加而提高,但有時會受到VCO校準時間(用于集成VCO)的限制,或因VCO輸入電容等寄生電容而使帶寬無法增加。 |

| 雜散 | 0Hz | 一般而言環路帶寬越窄,雜散越好,但有時會由環路濾波器周圍來自主板或芯片上的串擾所主導。 |

| 相位噪聲 | 0Hz或無限 |

如果相位噪聲低于最優抖動帶寬,相位噪聲會隨著帶寬的變寬而增大,直到變成僅為輸入基準和PLL造成的噪聲。 如果相位噪聲偏移大于最優抖動帶寬,相位噪聲會隨著環路帶寬的變窄而增大,直到變成僅為獨立的VCO噪聲。 |

表1:環路帶寬對關鍵參數的影響

為了說明表1,圖2中的模擬顯示了變化的環路帶寬的影響。鎖定時間與抖動標準化指標為圖2中從最小值增加的百分比。雜散與相位噪聲指標為圖2中從最小值增加的分貝。

如圖1所預測,環路帶寬為140kHz左右時,最優抖動確實為最佳。環路帶寬超出此范圍會有利于鎖定時間和10kHz相位噪聲,但是會降低雜散和1MHz偏移的相位噪聲。

因此,選擇環路帶寬的一種較好的方法是先選擇最優抖動帶寬(BWJIT),然后增加帶寬提高鎖定時間或低頻偏相位噪聲,或者降低帶寬提高高頻偏相位噪聲或雜散。

選擇正確的環路帶寬遇到問題?登錄并在下方評論。

審核編輯:金巧

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

振蕩器

+關注

關注

28文章

4172瀏覽量

142880 -

噪聲

+關注

關注

13文章

1156瀏覽量

49227 -

模擬

+關注

關注

7文章

1447瀏覽量

85381

發布評論請先 登錄

相關推薦

熱點推薦

相位噪聲分析儀(相噪儀)使用與選型指南

相位噪聲分析儀功能強大,例如安鉑克科技APPH系列用于評估信號源(晶體振蕩器、VCO、發射器、鎖相環、頻率合成器等,范圍從 VHF 到微波頻

TLC2932A高性能鎖相環芯片詳解:設計與應用指南

TLC2932A高性能鎖相環芯片詳解:設計與應用指南 在電子設計領域,鎖相環(PLL)是一種至關重要的電路,它能夠實現信號的相位同步和頻率合成,廣泛應用于通信、雷達、儀器儀表等眾多領域。今天要給大家

探索TLC2933A高性能鎖相環:特性、應用與設計要點

,了解其特性、工作原理及應用中的設計要點。 文件下載: tlc2933a.pdf 一、TLC2933A概述 TLC2933A專為鎖相環系統設計,主要由電壓控制振蕩器(VCO)和邊緣觸發型相位頻率檢測

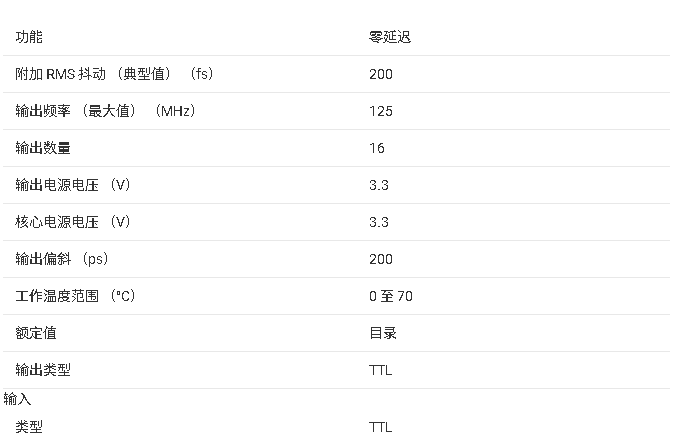

?CDCVF2510 3.3V鎖相環時鐘驅動器技術文檔總結

該CDCVF2510是一款高性能、低偏斜、低抖動、鎖相環 (PLL) 時鐘驅動器。它使用鎖相環 (PLL) 將反饋 (FBOUT) 輸出與時鐘 (CLK) 輸入信號在頻率和相位上精確對

?CDC516 3.3V相位鎖定環時鐘驅動器技術文檔總結

CDC516 是一款高性能、低偏斜、低抖動、鎖相環時鐘驅動器。它使用鎖相環 (PLL) 將反饋輸出 (FBOUT) 與時鐘 (CLK) 輸入信號在頻率和相位上精確對齊。它專為與同步 D

基于鎖相環的無軸承同步磁阻電機無速度傳感器檢測技術

使用場合。為實現無軸承同步磁阻電機高速超高速、低成本、實用化運行,提出了一種基于鎖相環法的無速度傳感自檢測技術。通過應用鎖相環原理,設計出無軸承同步磁阻電機無速度傳感器,并基于 Matlab

發表于 07-29 16:22

【RK3568+PG2L50H開發板實驗例程】FPGA部分 | Pango 的時鐘資源——鎖相環

: Window11 PDS2022.2-SP6.4

芯片型號: PG2L50H-484

2.實驗原理

2.1. PLL 介紹

鎖相環作為一種反饋控制電路,其特點是利用外部輸入的參考信號來控制環路內部

發表于 07-10 10:28

Analog Devices Inc. ADF4382x小數N分頻鎖相環 (PLL)數據手冊

Analog Devices ADF4382x小數N分頻鎖相環 (PLL) 是一款高性能、超低抖動、小數N分頻鎖相環 (PLL)。它集成了壓控振蕩器 (VCO),是5G或數據轉換器時鐘

ADF4151小數N/整數N分頻PLL頻率合成器技術手冊

= (INT + (FRAC/MOD))]。RF輸出相位可通過編程設置,適合要求輸出與基準之間存在特定相位關系的應用。ADF4151還具有周跳減少電路,可進一步縮短鎖定時間,而無需修改環路

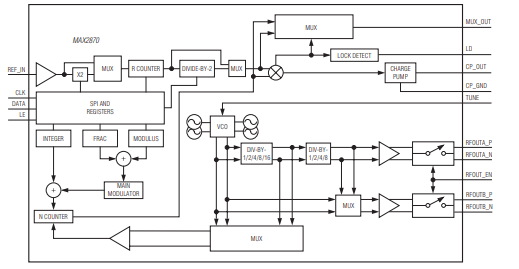

MAX2870 23.5MHz至6000MHz分數/整數N分頻合成器/VCO技術手冊

MAX2870為超寬頻帶鎖相環(PLL),集成壓控振蕩器(VCO),能夠工作在整數和分數N分頻模式。配合外部參考時鐘振蕩器和環路濾波器,MA

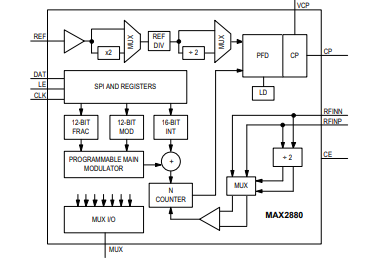

MAX2880 250MHz-12.4GHz、高性能、分數/整數型N分頻PLL技術手冊

MAX2880為高性能鎖相環(PLL),提供整數或分數N分頻工作模式。器件配合外部參考時鐘振蕩器、環路濾波器和VCO,可以構成超低噪聲、低

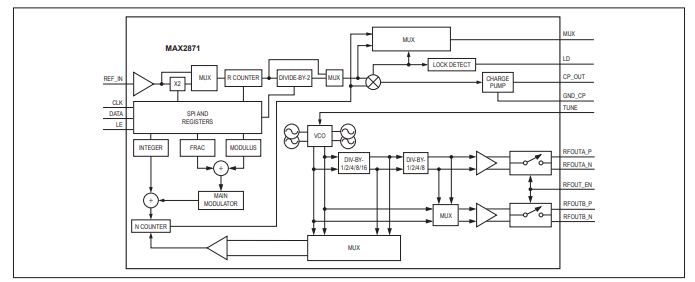

MAX2871 23.5MHz至6000MHz小數/整數N分頻頻率合成器/VCO技術手冊

MAX2871是一款超寬帶鎖相環(PLL),集成壓控振蕩器(VCO),可在整數N分頻和小數N分頻模式下工作。與外部基準振蕩器和環路濾波器結合

鎖相環(PLL)電路設計與應用(全9章)

內容介紹本文檔主要介紹鎖相環(PLL)電路的設計與應用,內容包括PLL工作原理與電路構成、PLL電路的傳輸特性、PLL電路中環路濾波器的設計方法、PLL電路的測試與評價方法、PLL特性改善技術

發表于 04-18 15:34

發現相位噪聲、鎖定時間或雜散問題請檢查鎖相環的環路濾波器帶寬

發現相位噪聲、鎖定時間或雜散問題請檢查鎖相環的環路濾波器帶寬

評論