LMK0480x 系列是業(yè)界性能最高的時鐘調(diào)節(jié)器,具有卓越的 時鐘抖動清理、生成和分配,具有滿足下一代需求的高級功能 系統(tǒng)要求。雙回路PLLatinum 該架構(gòu)能夠使用低噪聲VCXO模塊實(shí)現(xiàn)111 fs rms抖動(12 kHz至20 MHz)或 低于 200 fs rms 抖動(12 kHz 至 20 MHz),使用低成本外部晶體和變?nèi)輼O管 二極管。

*附件:lmk04803.pdf

雙環(huán)架構(gòu)由兩個高性能鎖相環(huán) (PLL) 組成,一個 低噪聲晶體振蕩器電路和高性能壓控振蕩器 (VCO)。 第一個PLL(PLL1)提供低噪聲抖動清除器功能,而第二個PLL(PLL2) 執(zhí)行時鐘生成。PLL1 可以配置為與外部 VCXO 模塊配合使用 或帶有外部可調(diào)諧晶體和變?nèi)荻O管的集成晶體振蕩器。什么時候 PLL1 與非常窄的環(huán)路帶寬配對,使用卓越的近相位噪聲(失調(diào) 低于 50 kHz)或可調(diào)諧晶體,以清潔輸入時鐘。的輸出 PLL1用作PLL2的干凈輸入基準(zhǔn)電壓源,鎖定集成VCO。循環(huán) 可以優(yōu)化 PLL2 的帶寬,以清除遠(yuǎn)相位噪聲(偏移高于 50 kHz),其中 集成VCO的性能優(yōu)于PLL1中使用的VCXO模塊或可調(diào)諧晶體。

特性

- 超低RMS抖動性能

- 111 fs RMS 抖動(12 kHz 至 20 MHz)

- 123 fs RMS 抖動(100 Hz 至 20 MHz)

- 雙環(huán)路PLLatinum? PLL架構(gòu)

- PLL1

- 集成低噪聲晶體振蕩器

電路 - 輸入時鐘丟失時的保持模式

- 自動或手動觸發(fā)/恢復(fù)

- 集成低噪聲晶體振蕩器

- PLL2

- 歸一化PLL本底噪聲為–227 dBc/Hz

- 相位檢測器速率高達(dá) 155 MHz

- OSCin 倍頻器

- 集成低噪聲VCO

- 2 個帶 LOS 的冗余輸入時鐘

- 自動和手動切換模式

- 50 % 占空比輸出分頻,1 至 1045(偶數(shù)

和奇數(shù)) - 12 個 LVPECL、LVDS 或 LVCMOS 可

編程輸出 - 數(shù)字延遲:固定或動態(tài)可調(diào)

- 25 ps 步進(jìn)模擬延遲控制。

- 14 個差分輸出。多達(dá) 26 個單端。

- 多達(dá)6個VCXO/晶體緩沖輸出

- 時鐘速率高達(dá) 1536 MHz

- 0-延遲模式

- 上電時三個默認(rèn)時鐘輸出

- 多模:雙 PLL、單 PLL 和時鐘

分配 - 工業(yè)溫度范圍:–40 至 85°C

- 3.15V 至 3.45V 工作電壓

- 2 個專用緩沖/分頻 OSCin 時鐘

- 封裝:64 引腳 WQFN (9.0 × 9.0 × 0.8 mm)

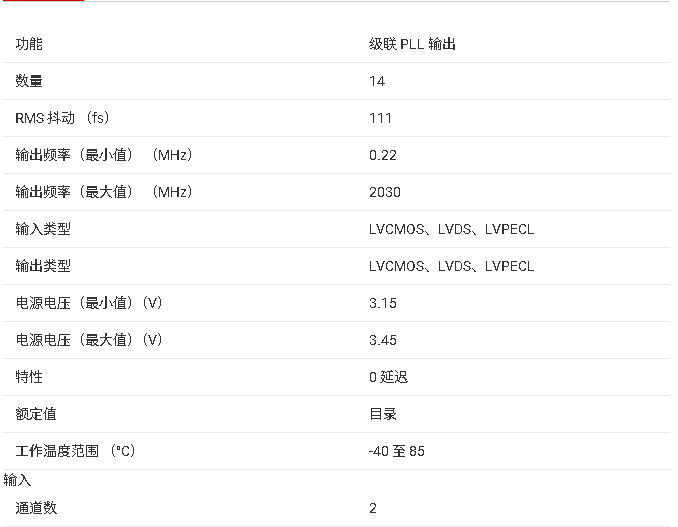

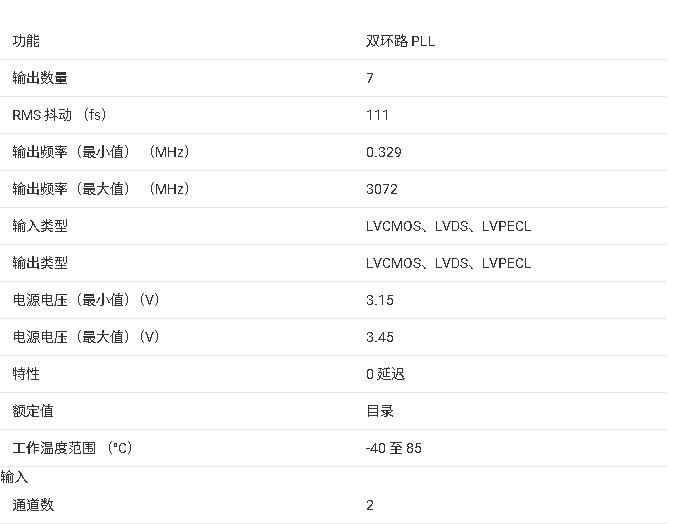

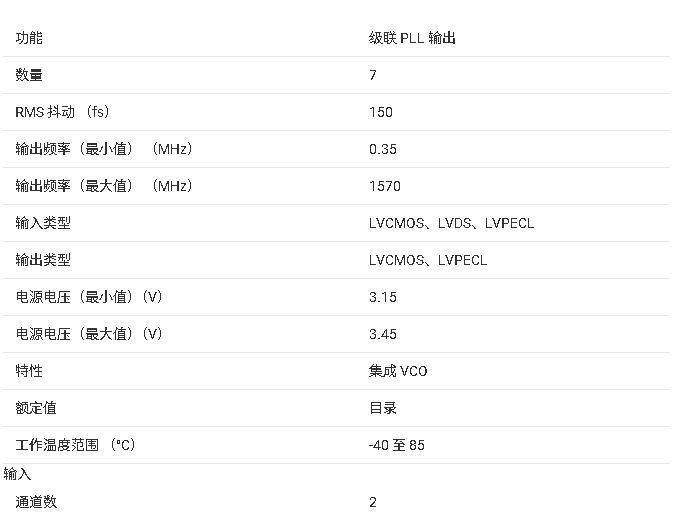

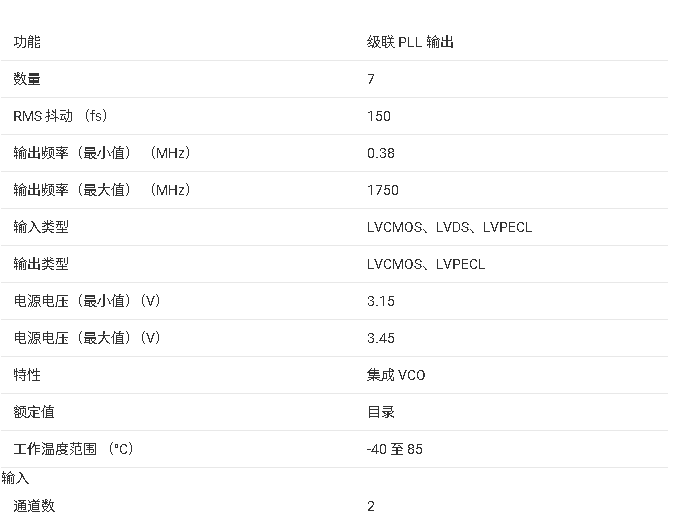

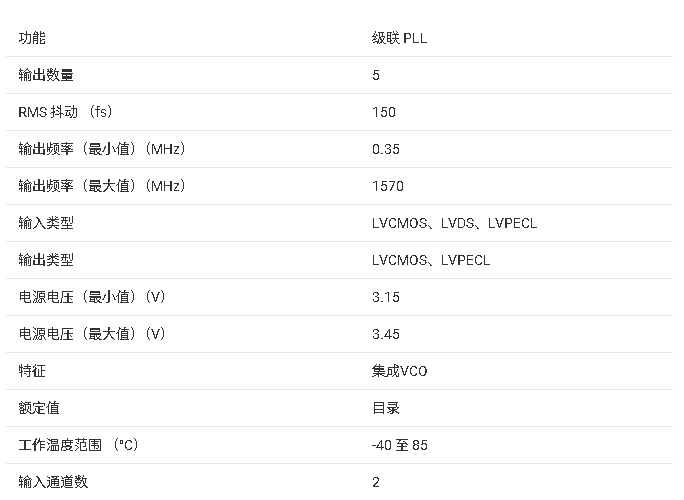

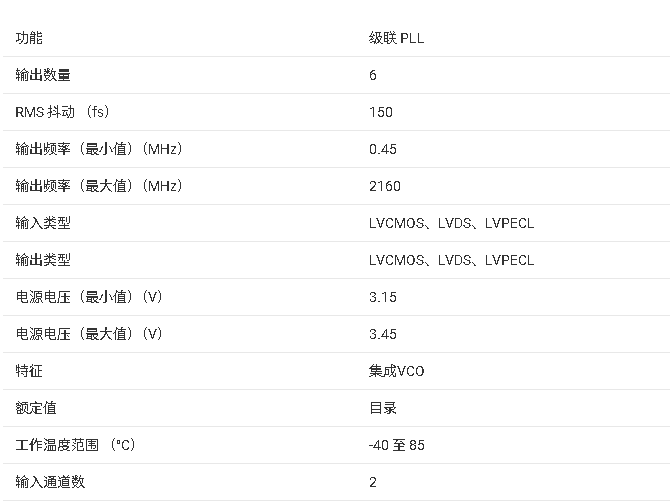

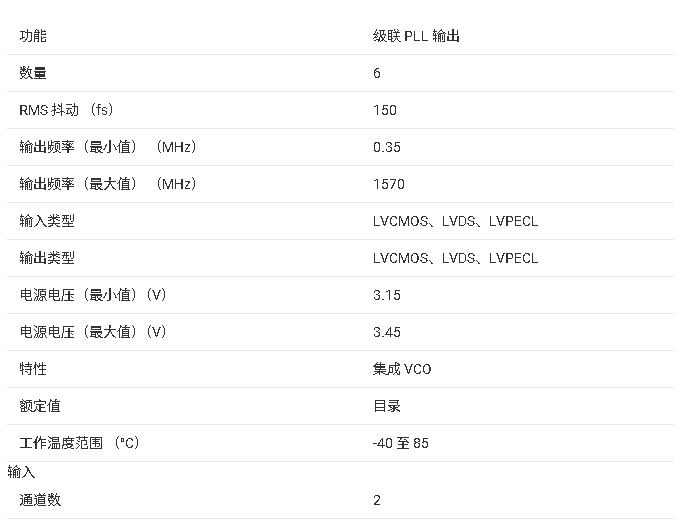

參數(shù)

方框圖

?1. 產(chǎn)品概述?

LMK0480x系列是德州儀器(TI)推出的高性能時鐘調(diào)節(jié)器家族,包含LMK04803/05/06/08等型號,專為低噪聲時鐘抖動清理、生成和分配設(shè)計(jì)。其核心特性包括:

- ?雙環(huán)PLLatinum?架構(gòu)?:PLL1用于抖動清理,PLL2用于時鐘生成,支持111 fs RMS超低抖動(12 kHz–20 MHz頻段)。

- ?多模式工作?:支持雙PLL、單PLL或純時鐘分配模式。

- ?靈活輸出配置?:12個可編程輸出(LVPECL/LVDS/LVCMOS),支持50%占空比分頻(1–1045分頻比)。

- ?冗余輸入與故障切換?:2路冗余輸入時鐘,支持自動/手動切換和保持模式(Holdover)。

?2. 關(guān)鍵特性?

- ?抖動性能?:

- 111 fs RMS(12 kHz–20 MHz)

- 123 fs RMS(100 Hz–20 MHz)

- ?集成功能?:

- 數(shù)字/模擬延遲控制(25 ps步進(jìn))

- 14路差分輸出(最高26路單端)

- 6路VCXO/晶體緩沖輸出

- ?工作范圍?:

- 電壓:3.15–3.45 V

- 溫度:-40°C至85°C

?3. 應(yīng)用領(lǐng)域?

- 數(shù)據(jù)轉(zhuǎn)換器時鐘

- 無線基礎(chǔ)設(shè)施(如基站)

- 網(wǎng)絡(luò)設(shè)備(SONET/SDH、DSLAM)

- 醫(yī)療/視頻/軍工/航空航天

- 測試與測量設(shè)備

?4. 技術(shù)細(xì)節(jié)?

- ?PLL1?:集成低噪聲晶體振蕩電路,支持外部VCXO或晶體+變?nèi)荻O管方案。

- ?PLL2?:集成低噪聲VCO,相位檢測速率達(dá)155 MHz,支持頻率倍增。

- ?封裝?:64引腳WQFN(9.0×9.0×0.8 mm),帶裸露焊盤(DAP)散熱設(shè)計(jì)。

?5. 文檔結(jié)構(gòu)?

- ?功能描述?:包括雙PLL架構(gòu)、時鐘切換邏輯、延遲控制等。

- ?寄存器配置?:詳細(xì)編程指南及寄存器映射表(共51頁)。

- ?應(yīng)用示例?:典型電路設(shè)計(jì)、布局建議及電源管理方案。

?6. 修訂歷史?

- 最新版本(Rev. K)優(yōu)化了電氣特性參數(shù),新增PLL2頻率倍增器說明,并修正了部分模式配置描述。

-

二極管

+關(guān)注

關(guān)注

149文章

10325瀏覽量

176849 -

時鐘

+關(guān)注

關(guān)注

11文章

1955瀏覽量

134615 -

調(diào)節(jié)器

+關(guān)注

關(guān)注

5文章

911瀏覽量

49184 -

清除器

+關(guān)注

關(guān)注

0文章

56瀏覽量

6065 -

VCXO

+關(guān)注

關(guān)注

0文章

55瀏覽量

10000

發(fā)布評論請先 登錄

LMK04832-SP時鐘抖動清除器

LMK04803 具有雙級聯(lián) PLL 和集成 1.9 GHz VCO 的低噪聲時鐘抖動消除器

LMK04714-Q1符合JESD204B/C標(biāo)準(zhǔn)的汽車級、超低噪聲、雙環(huán)路時鐘抖動清除器數(shù)據(jù)表

LMK04832-SEP符合JESD204B/C標(biāo)準(zhǔn)的航天級、超低噪聲、雙環(huán)路時鐘抖動清除器數(shù)據(jù)表

LMK04368-EP符合JESD204B/C標(biāo)準(zhǔn)的超低噪聲、雙環(huán)路時鐘抖動清除器數(shù)據(jù)表

LMK04832-SP符合JESD204B標(biāo)準(zhǔn)的航天級、超低噪聲、雙環(huán)路時鐘抖動清除器數(shù)據(jù)表

帶雙環(huán)路PLL且符合JESD204B標(biāo)準(zhǔn)的LMK04832超低噪聲時鐘抖動清除器數(shù)據(jù)表

LMK04906帶6路可編程輸出的,超低噪聲時鐘抖動清除器和乘法器數(shù)據(jù)表

具有雙環(huán)路PLL的LMK04228超低噪聲且符合JESD204B標(biāo)準(zhǔn)的時鐘抖動清除器數(shù)據(jù)表

LMK04803 低噪聲時鐘抖動清除器技術(shù)手冊

LMK04803 低噪聲時鐘抖動清除器技術(shù)手冊

評論