的速度。我們將首先使用C語言進行代碼實現,然后在Vivado HLS中綜合實現,并最終在FPGA板(pynq-z2)上進行硬件實現,同時于jupyter notebook中使用python來進行功能驗證。

2025-07-10 11:09:34 2197

2197

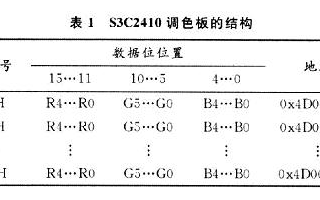

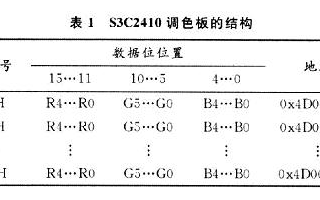

ARM9核的S3C2410芯片可通過內置的LCD控制器來實現對LCD顯示的控制。以TFT LCD為例,S3C2410芯片的LCD控制器可以對TFT LCD提供1位、2位、4位、8位調色板彩色顯示和16位、24位真彩色顯示,并支持多種不同的屏幕尺寸。

2020-10-04 17:45:00 3152

3152

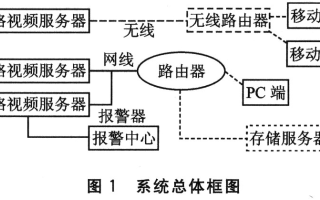

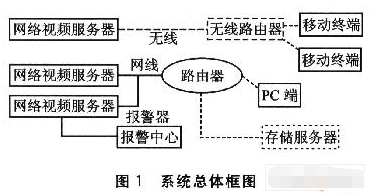

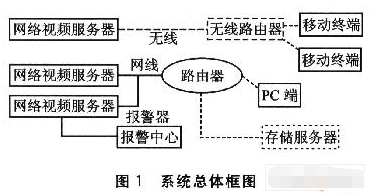

硬件部分以三星公司的ARM9芯片S3C2410和韓國的專用視頻芯片AT2042為核心。S3C2410主要實現系統控制功能,例如對AT2042的配置,接收視頻流數據并利用USB存儲設備進行存儲;配置

2020-10-19 10:06:27 4537

4537

FPGA EP3C40F484C8的模塊(以下稱:FPGA卡)。DSP卡是以TI的DSP TMS320C6455作為主芯片,可用于高速數據、視頻信號檢測,分析等應用;FPGA卡處理芯片為

2014-06-30 10:34:25

代理EP2S90F1508I4國宇航芯代理EP2S90F1508C3國宇航芯代理EP2SGX90EF1152C3國宇航芯代理EP2SGX90EF1152I4國宇航芯代理EP2S130F780C5N國宇航

2019-09-05 11:36:09

IC FPGA 902 I/O 1508FBGA

2023-03-27 10:23:14

對明文進行分組加密變換。SM4加密算法由32次迭代運算和一次反序變換R組成。

設輸入明文為(X0,X 1,X 2,X 3),共128位,設密文輸出為(Y0,Y 1,Y 2,Y 3),輪密鑰為rki

2025-10-30 08:10:23

本人學生,在實驗室打算做EMD算法的硬件實現,看了一些論文,感覺主要是單獨用FPGA實現,或者用DSP+FPGA實現(DSP做EMD算法,FPGA做數據流控制),請問大家用哪種架構做硬件實現EMD算法比較好?

2018-04-25 21:04:33

Table,LUT)和基于伽羅瓦域(Galois Field,GF)兩種方式。基于LUT實現S盒,AES加解密需要2塊LUT,SM4加解密需要1塊LUT,合計3塊LUT。然而,兩種算法的S盒在GF下具有

2025-10-23 07:26:23

SHA2-512、SHA3、SM3和SM4。

SVE2-AES、SVE2-SHA3和SVE2-SM擴展添加了A64指令,以加速SHA3、SM3、SM4和AES加密和解密。

2023-08-17 06:25:22

的要求和FPGA芯片設計的靈活性結合起來,采用Alter公司的CycloneⅡ系列FPGA芯片EP2C35F672C8,用VHDL語言編程,最后分別使用Quartus Ⅱ和Matlab軟件開發工具驗證實現

2010-05-28 13:38:38

、HR-30TH-2F-Ex、HR-30S-1F-ExHR-30S-2F、HT-100F、HT-100R、HTM-930ST、HM-12SHTM-930HR-30S-3F HLG-100F

2019-04-01 11:54:07

一、國密芯片RJMU401數據加密傳輸、身份認證及數據完整性保證1、 傳輸信道中的數據都采用SM4分組加密算法,保證數據傳輸時數據的機密性;2、 使用散列算法SM3保證數據的完整性,以防止數據在傳輸

2019-01-02 14:55:24

你好。 bspartan 3a dsp fpga上的哪個芯片可以讓我實現i2c?感謝您的幫助。以上來自于谷歌翻譯以下為原文Hi. Which chip on the bspartan 3a dsp

2019-05-24 10:54:12

`采用32位CPU內核芯片支持國際算法DES,AES,SHA,RSA1024/2048等主流算法支持國密算法SM1,SM2,SM3,SM4,SM7,SSF33算法支持SM2RSA密鑰對生成支持多級

2018-07-20 17:03:39

、WDT、TRNG、DES/3DES、AES128/192/256、SM1、SM4、SSF33、RSA、SM2/ECC、SM3/SHA1/256/384/512、CRC16。 可替代英飛凌、NXP的加密芯片。QQ:2770494629

2018-07-05 14:31:23

國家密碼管理局推出的SM系列密碼算法是為了從根本上擺脫我國對國外密碼技術的依賴,實現從密碼算法層面掌控核心的信息安全技術。隨著國密算法推廣的延伸,金融領域引入SM2、SM3、SM4等算法逐步替換原有

2021-07-23 08:57:37

所示:

非對稱加密算法:SM2算法可用于電子認證服務;SM9算法可用于各種互聯網新興應用。

對稱加密算法:SM1算法未公布,以IP核的形式存在于芯片中,可用于電子政務、電子商務及國民經濟等領域;SM

2025-10-24 08:25:18

本帖最后由 gk320830 于 2015-3-8 21:23 編輯

開始科創,老師給了我們一個題基于FPGA的FFT算法硬件實現。但是什么都不會,想找些論文看看,求相關的論文

2012-05-24 22:14:40

碼力分享基于FPGA的可變祖沖之(ZUC)算法的設計與實現1:概述基于FPGA的可變祖沖之(ZUC)算法的設計與實現軟件:ISE語言:Verilog HDL,C語言 2:功能通過加入可配置模塊(如S

2015-10-14 21:56:52

VGA顯示屏上,前面我們把硬件平臺已經搭建完成了,后面我們將利用這個硬件基礎平臺上來實現基于FPGA的一系列圖像處理基礎算法。椒鹽噪聲(salt &pepper noise)是數字圖像的一

2017-08-28 11:34:10

)環境下進行的,編程代碼采用VHDL語言進行編寫,硬件芯片平臺選擇ALTERA公司的Strat ixⅡ系列EP2S90 FPGA芯片。系統設計端口定義如下:ad_clk:數據AD采樣時鐘RST:系統復位

2015-02-05 15:34:43

是處理數字信號如圖形、語音及圖像等領域的重要變換工具。快速傅里葉變換(FFT)是DFT的快速算法。FFT算法的硬件實現一般有3種形式:1)使用通用DSP來實現;2)用專用DSP來實現;3)通過FPGA來

2009-06-14 00:19:55

最近項目中需要通過C語言實現SM2、SM4國密算法,這里我基于GMSSL來進行實現,本人已在這5種環境下全部實現,并已使用在生產環境中。1、GMSSL編譯GMSSL編譯在不同環境下都不一樣,這里我

2021-07-22 06:28:06

TMS320C6455的模塊(以下稱:DSP卡)和基于Altera FPGA EP3C40F484C8的模塊(以下稱:FPGA卡)。DSP卡是以TI的DSP TMS320C6455作為主芯片,可用于高速數據

2012-06-13 11:50:44

ALTERA的高端FPGA芯片Stratix II EP2S系列EP2S60,板卡使用FPGA用于獲取雙通道數據采集,實現1路的Base CameraLink輸入,一路Base CameraLink

2012-06-13 11:39:49

ALTERA的高端FPGA芯片Stratix II EP2S系列EP2S60,板卡使用FPGA用于獲取雙通道數據采集,實現1路的Base CameraLink輸入,一路Base CameraLink

2012-06-13 12:01:23

EP3C40F484C8的模塊(以下稱:FPGA卡)。DSP卡是以TI的DSP TMS320C6455作為主芯片,可用于高速數據、視頻信號檢測,分析等應用;FPGA卡處理芯片為EP3C40F484C

2012-06-13 11:52:30

CycloneⅡ EP2C35F672C6芯片上進行驗證。圖3為改進的16級流水線結構的CORDIC算法實現復乘模塊的頂層結構圖,address為ROM的地址,Xi_re、Xi_im為輸入序列的實部和虛

2011-07-11 21:32:29

Compiler)將算法編譯轉化為可綜合的 Verilog 文本,進而通過 FPGA 在硬件上實現算法。

1.C to Hardware 技術簡介

AltiumDesigner

2025-10-30 07:02:09

=64 點的基-4DIT信號流其輸入數據序列是按自然順序排列的,輸出結果需經過整序。64點數據只需進行3次迭代運算,每次迭代運算含有N/4=16個蝶形單元。2 FFT算法的硬件實現2.1 流水線方式

2019-06-17 09:01:35

主要內容包括:1. 為什么很多人覺得學習FPGA很困難,以及HDL學習的一些誤區;2. 軟件和硬件在算法實現上的區別;3. 通過具體例子詳細講解了從算法的行為級建模向RTL級建模的轉換思想和底層電路

2015-09-18 15:44:39

本設計中采用了ALTERA公司的 EP1C3T144芯片進行設計,實際測試表明系統的各項設計要求均得到滿足并且系統工作良好,該設計采用了SOPC技術和FPGA,幾乎將整個系統下載于同一芯片中,實現了

2021-04-30 06:56:14

我正在做我的遺傳算法項目,有沒有辦法在斯巴達3AN fpga中實現遺傳算法,如果沒有建議我一些方法來克服這種沖突。謝謝以上來自于谷歌翻譯以下為原文I am doing my project

2019-04-03 13:16:55

本帖最后由 eehome 于 2013-1-5 10:04 編輯

指紋識別算法的研究及基于FPGA的硬件實現

2012-05-23 20:14:46

,可設置成多重復合設備,最大限度地滿足用戶的設計需求。2? 算法全面:集成多種通信接口和多種信息安全算法(SM1、SM2、SM3、SM4、3DES、RSA 等),可實現高度整合的單芯片解決方案。? 支持

2013-04-27 17:17:45

用FPGA硬件實現。 現在我沒有FPGA硬件實現的經驗,不知道如何用FPGA硬件實現小波算法。 懇請賜教!謝謝!

2012-11-20 21:35:16

就已經出現,隨著FPGA芯片價格的不斷降低,其在工業領域的應用正在飛速發展,采用FPGA來實現SVPWM調制算法也將層出不窮2. 系統任務分析及實現SVPWM調制算法相對比較復雜,在完成系統控制任務

2022-01-20 09:34:26

)--->EP3C5F256AG6KF256(AG10KF256)--->EP4CE6F17AG10KF256--->EP3C10F256AG10KF256--->EP4CE10F17&nb

2021-11-23 13:38:18

我們是AGM的長期授權代理商,可以為用戶提供最具競爭力的價格與技術支持服務。PIN to PIN Altera-FPGA:AG16KF256--->EP3C16F256

2021-11-23 14:05:50

基FPGA Cyclone II_EP2C5 EP2C8的頻率計

基FPGA_Cyclone_II_EP2C5/EP2C8的頻率計

功能描述:按4*4鍵盤上的1,2,3...號按鍵可依次測出 25000000Hz ,12500000Hz ....的分

2008-11-30 12:17:01 87

87 基于S3C44B0X微處理器的JFFS2件系統的實現

2009-03-28 09:50:21 16

16 摘要:本文研究了S A R雷達原始數據B A V Q壓縮算法的硬件實現。采用 A D S P 2 1 0 6 0 ( S H A R C ) 芯片結合 A l t e r a公司的F L E X l O K l 0 L C 8 4 - 3芯片組成最簡的系統,采用

2009-05-07 10:41:47 14

14 Audio Compression-3(A C-3)算法廣泛應用于電影、DVD.DTV等消費電子領域。本文設計并實現了一種AC-3軟件解碼器,并成功地在通用DSP (TMS320C6701)上優化實現T AC-3實時解碼算法。

2009-05-08 16:46:03 20

20 本文基于Altera的FPGA(StatixⅡ-EP2S30F484C3)架構,實現了碼率為1/2,幀長為1008bits的規則(3,6)LDPC碼譯碼器。所采用的最小-和算法相對于傳統的和-積算法在不損失譯碼性能的前提下,

2009-06-06 14:12:20 31

31 提出用FPGA 來實現指紋識別算法, 代替了PC 機、通用MCU 或者DSP。算法由硬件來實現, 提高了運算速度。同時具體說明了指紋識別系統的基本原理、系統總體結構、FPGA 模塊劃分, 以及指

2009-07-22 15:17:27 0

0 EP4CE10F17C8N,Cyclone IV FPGA設備,INTEL/ALTERAEP4CE10F17C8N,Cyclone IV FPGA設備,INTEL

2023-02-20 17:00:57

EP4CE6F17C8N ,Cyclone IV FPGA設備,INTEL/ALTERAEP4CE6F17C8N ,Cyclone IV FPGA設備,INTEL

2023-02-20 17:05:47

介紹了AES中,SubBytes算法在FPGA的具體實現.構造SubBytes的S-Box轉換表可以直接查找ROM表來實現.通過分析SubBytes算法得到一種可行性硬件邏輯電路,從而實現SubBytes變換的功能.

2010-11-09 16:42:48 25

25 提出一種基于DCT域的數字水印算法,并用FPGA硬件實現其中關鍵部分DCT變換。采用VHDL語言有效設計和實現DCT變換,分析與仿真結果表明:與軟件實現相比,用FPGA實現水印算法具有高

2010-12-28 10:22:14 20

20 摘要:介紹3-DES算法的概要;以Xilinx公司SPARTANII結構的XC2S100為例,闡述用FPGA高速實現3-DES算法的設計要點及關鍵部分的設計。引 言

2006-03-13 19:36:42 1016

1016

摘要:給出S3C2410上觸摸屏的實現原理、硬件結構和軟件程序;對軟件進行優化,改進軟件濾波的實現方法。其算法使用C語言實現,可移植到任何操作系統的觸摸屏

2006-04-07 00:32:37 1689

1689

摘要:介紹3-DES算法的概要;以Xilinx公司SPARTANII結構的XC2S100為例,闡述用FPGA高速實現3-DES算法的設計要點及關鍵部分的設計。

關鍵詞:3-DES

2009-06-20 14:22:00 1600

1600

AES算法中S-box和列混合單元的優化及FPGA技術實現

由于其較高的保密級別,AES算法被用來替代DES和3-DES,以適應更為嚴苛的數

2010-04-23 09:34:22 3473

3473

提出了二維模糊CMAC網絡的一種基于FPGA的硬件實現方法。首先,分析了模糊CMAC網絡的結構與算法,并以Matlab仿真為依據,得到模糊CMAC網絡的FPGA實現所需的參數;在此基礎上,對模糊CMAC網絡進行硬件模塊劃分,基于VHDL實現了各硬件模塊的功能描述,并對模塊

2011-03-15 17:19:56 29

29 基于S3C2440的Ethercat實現,EtherCAT 是開放的實時以太網絡通訊協議,EtherCAT為系統的實時性能和拓撲的靈活性樹立了新的標準,同時,它還符合甚至降低了現場總線的使用成本。

2011-12-15 09:59:33 5304

5304

基于FPGA的SM3算法優化設計與實現的論文

2015-10-29 17:16:51 5

5 基于S3C2440和μC%2fOS的FAT文件系統的設計與實現

2016-01-04 17:03:55 5

5 基于EP1C3的FPGA程序ledverilog,好東西,喜歡的朋友可以下載來學習。

2016-01-20 15:22:36 5

5 基于EP1C3的FPGA程序之seg7_verilog

2016-01-20 15:22:50 11

11 基于EP1C3的FPGA程序ledverilog

2016-11-18 16:05:02 1

1 基于EP1C3的FPGA程序之seg7_verilog

2016-11-18 16:05:02 0

0 ep3c資料

2016-12-20 22:24:19 6

6 利用FPGA實現信號處理算法是一個難度頗高的應用,不僅涉及到對信號處理算法、FPGA芯片和開發工具的學習,還意味著要改變傳統利用軟件在DSP上實現算法的習慣,從面向硬件實現的算法設計、硬件實現、結構優化和算法驗證等多個方面進行深入學習。

2016-12-26 17:26:41 12

12 開發板EP1C3T144_FPGA_develop_board_manual

2017-03-20 11:38:00 32

32 算法進行深入研究,面向Xilinx K7 410T FPGA 芯片設計SHA-1算法實現結構,完成SHA-1算法編程,進行測試和后續應用。該算法在FPGA 上實現,可以實現3.2G bit/s的吞吐率

2017-10-30 16:25:54 4

4 描述語言實現,最終下載到FPGA芯片Stratix EP1S25F780C5中。 關鍵詞: 狀態機 流水線 3DFS FPGA 隨著網絡的快速發展,信息安全越來越引起人們的關注。加密技術作為信息安全的利器,正發揮著重大的作用。通過在硬件設備(如由器、交換機等)中添加解

2017-11-06 11:10:09 7

7 的能量分析新型攻擊方法,該新型攻擊方法每次攻擊時選擇不同的攻擊目標和其相關的中間變量,根據該中間變量的漢明距離模型或者漢明重量模型實施能量分析攻擊,經過對SM3密碼算法的前4輪多次實施能量分析攻擊,將攻擊出的所有結果聯立方程組,對

2018-02-11 09:57:53 1

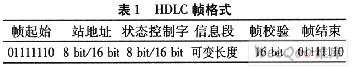

1 它還具有設計開發周期短、設計制造成本低、可實時在線檢驗等優點,因此被廣泛用于特殊芯片設計中。本設計中采用Altera公司的EP2C70F672C8芯片來實現HDLC協議控制器。

2018-12-30 11:00:00 4456

4456

本文檔的主要內容詳細介紹的是FPGA EP1C3開發板原理圖的詳細資料免費下載。

2018-09-26 16:35:00 63

63 本文提出了一種實現信號采集方案,介紹了由ARM 處理器S3C2410 和EP2C8 FPGA 組成的高速信號采集系統的系統設計,并著重介紹前端硬件的設計,并就ARM 處理器和FPGA 的互聯設計進行探討。利用FPGA 硬件控制A/D 轉換,達到了較好的效果,實現了信號的采集與存儲。

2018-11-02 15:46:01 12

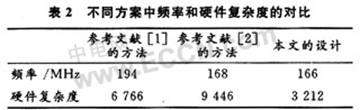

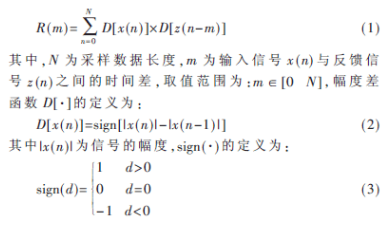

12 基于FPGA芯片Stratix II EP2S60F672C4設計實現了數字基帶預失真系統中的環路延遲估計模塊。該模塊運用了一種環路延遲估計新方法,易于FPGA實現。同時,在信號失真的情況下也能給

2018-12-19 11:04:26 2192

2192

1、FPGA使用EP1C3T144C8,硬件電路充分考慮了可升級性,該板子同樣適用于EP1C6T144

2019-12-12 07:10:00 3502

3502

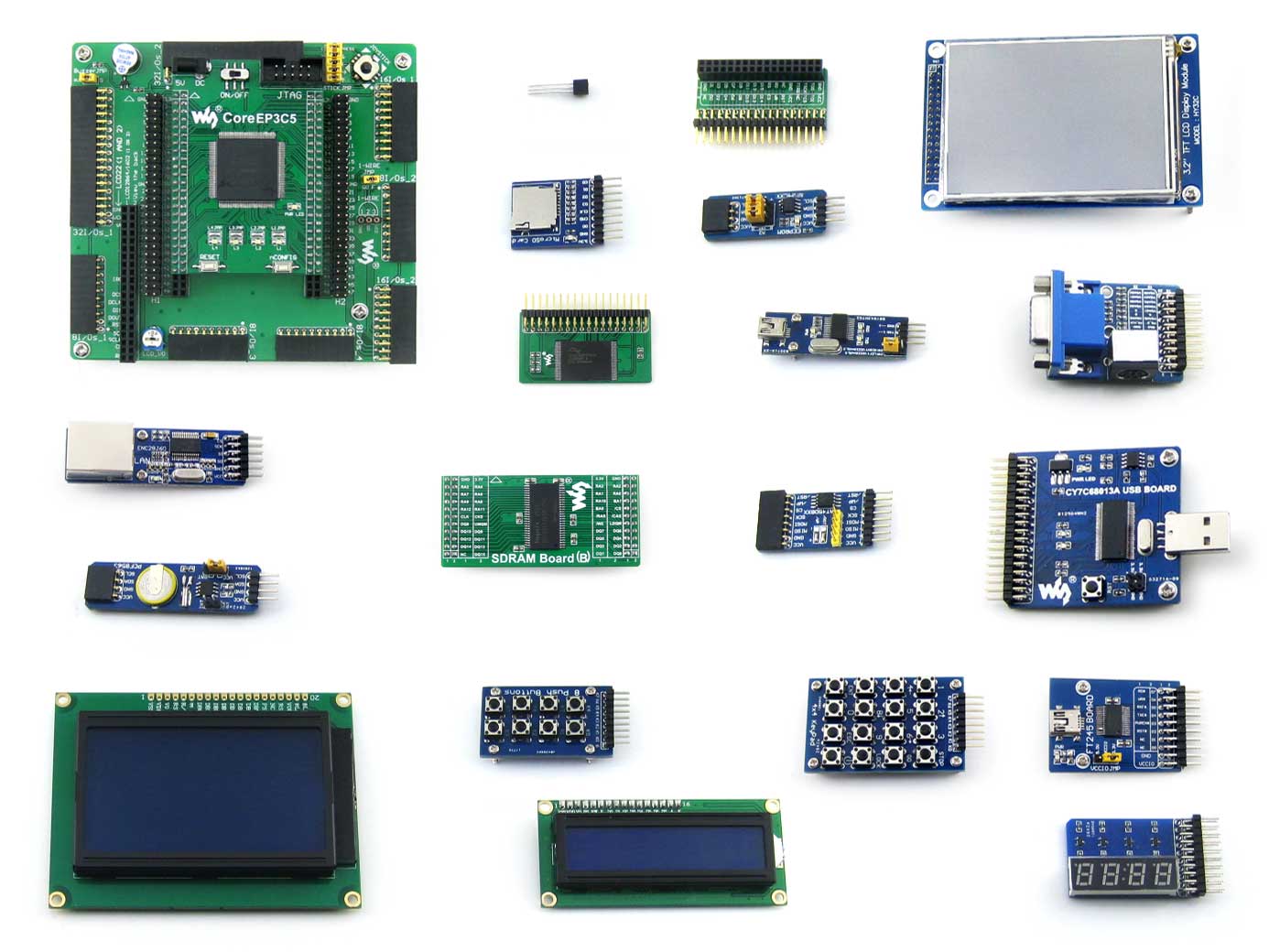

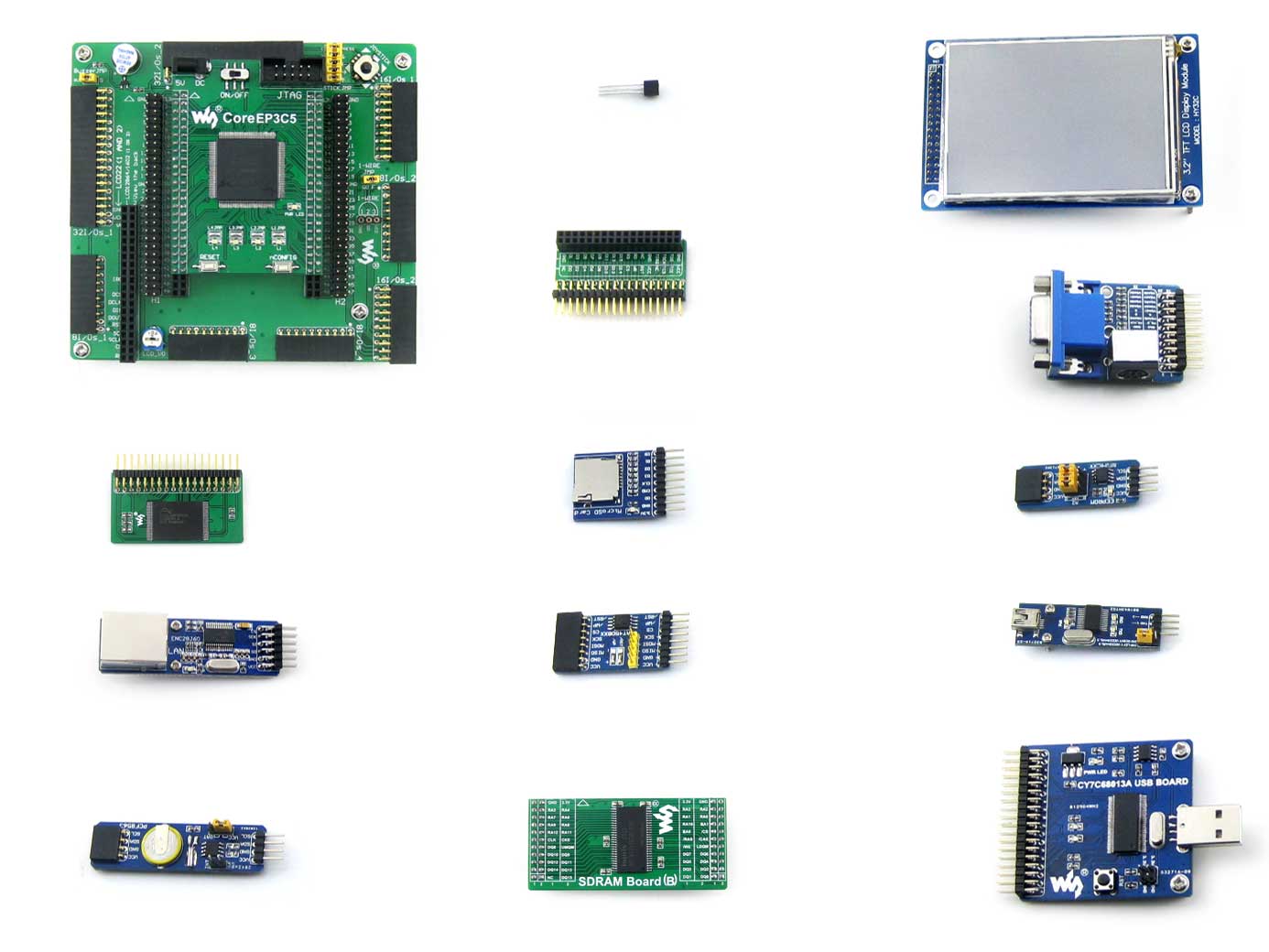

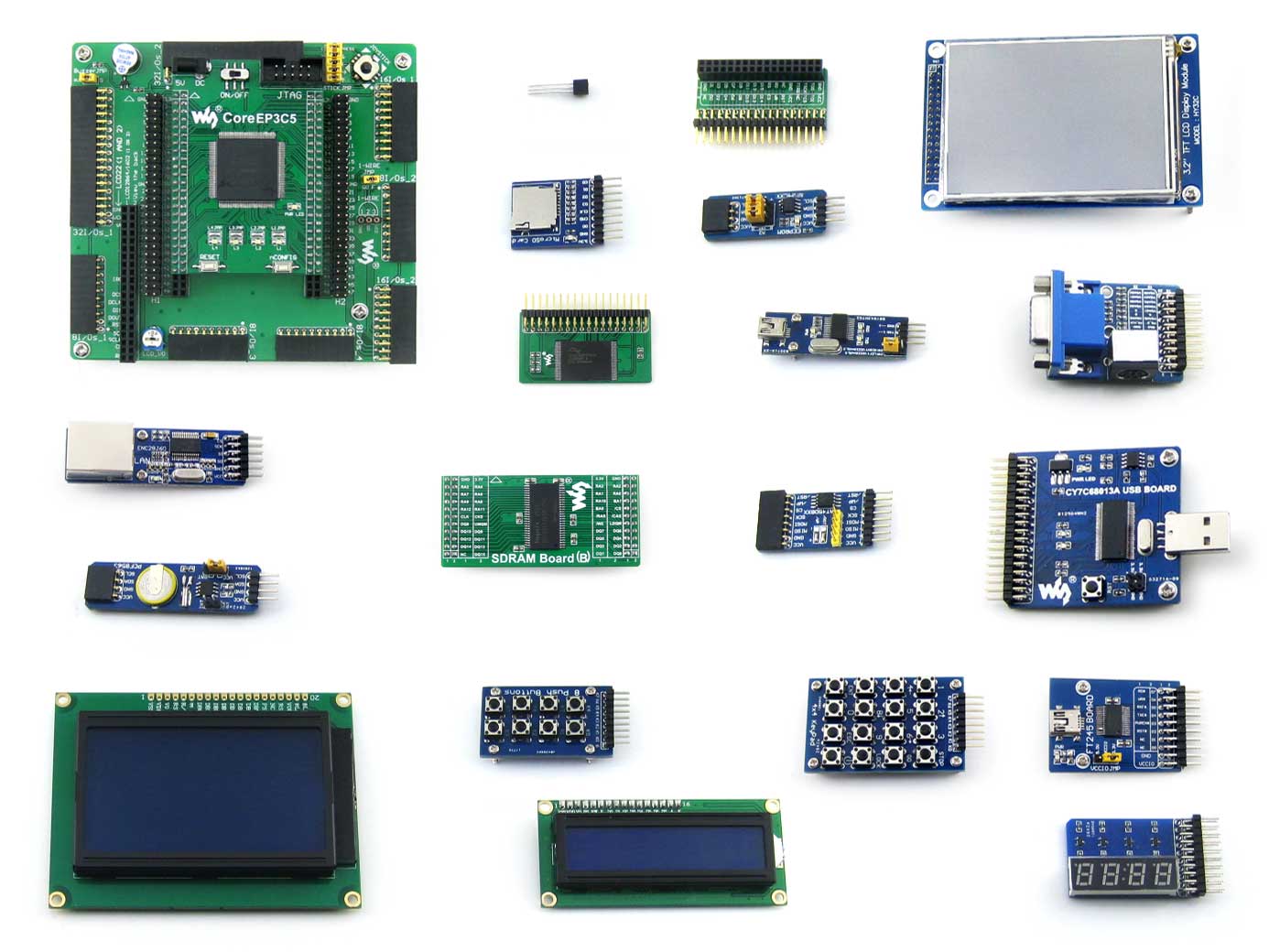

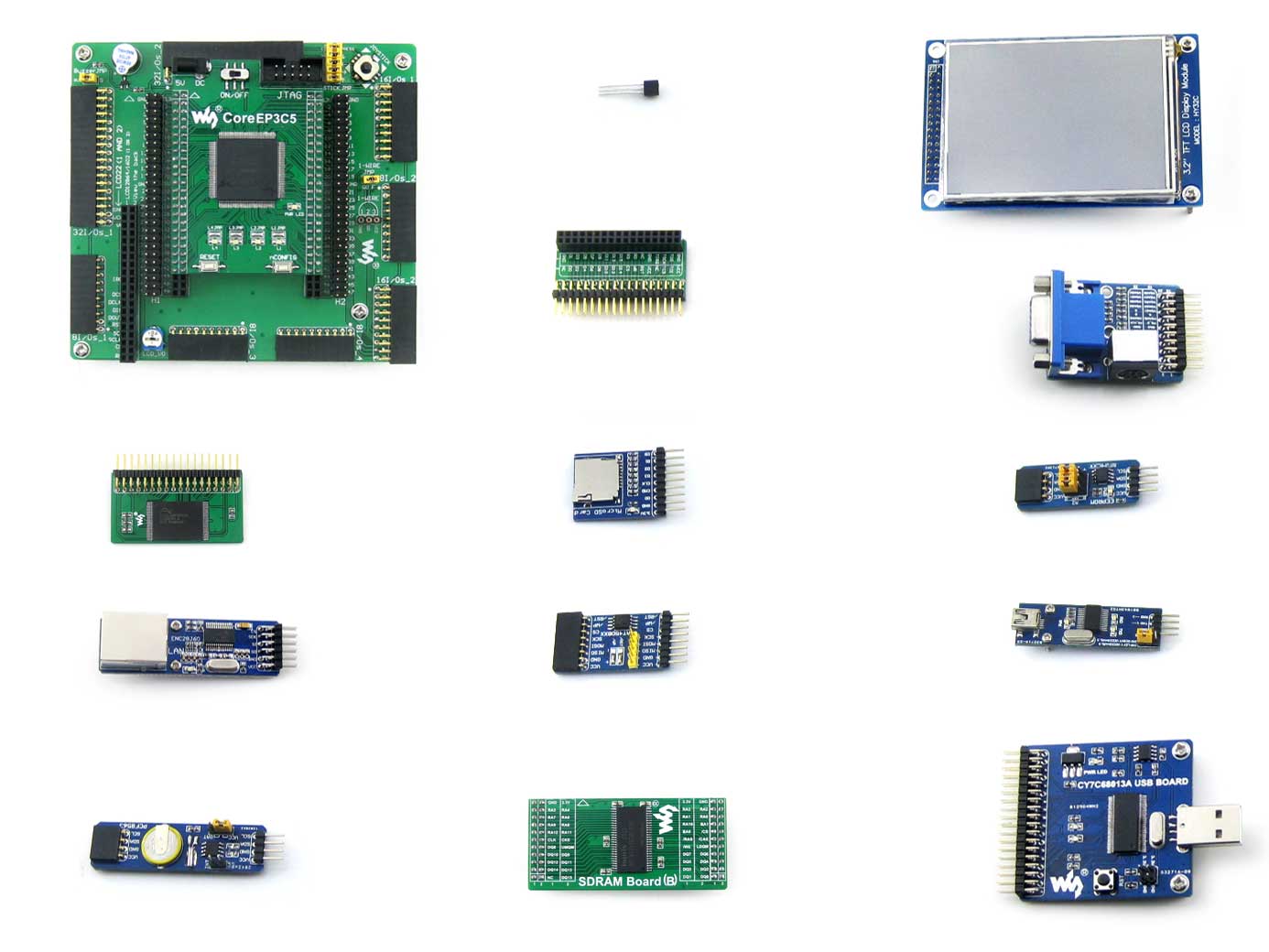

,包括實用新型專利及外觀專利,仿造必追究其法律責任! FPGA開發板OpenEP3C5-C是一塊以Cyclone III EP3C5為主控芯片的開發板,它帶有豐富的擴展接口,支持各類外圍模塊的接入

2019-12-23 11:23:08 2483

2483

FPGA開發板OpenEP3C5-C是一塊以Cyclone III EP3C5為主控芯片的開發板,它帶有豐富的擴展接口,支持各類外圍模塊的接入。

2019-12-23 11:30:13 1776

1776

的軟件部署方法(2)針對MPSOC FPGA平臺的YOLOV-V3算法和相關接口的硬件實現和部署流程。 主要指標 (1)FPGA硬件計算平臺為 RJIBI FACE系列板卡套件 (2)深度學習訓練框架

2020-05-19 10:22:58 15991

15991 高、資源敏感而計算時延要求并不高,這時我們需要一種保證計算正確且資源開銷最低的FPGA實現方法,本文給出了實現乘除法、開方運算的FPGA串行實現算法,并與LPM宏函數進行了性價比比較。結果表明,本文給出的各算法計算準確,資源量遠小于調用LPM宏函數。

2020-07-29 17:48:57 1835

1835

硬件部分以三星公司的ARM9芯片S3C2410和韓國的專用視頻芯片AT2042為核心。S3C2410主要實現系統控制功能,例如對AT2042的配置,接收視頻流數據并利用USB存儲設備進行存儲;配置

2020-08-12 09:39:21 3297

3297

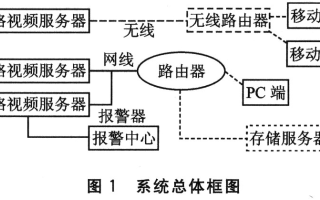

系統框圖如圖1所示。FPGA控制單元采用 A1tera公司Cyclone II系列的EP2C5F256C6,主要由4個部分組成——主控模塊、CMOS傳感器接口、RAM控制器以及EZ—USB接口控制器

2020-08-24 16:53:28 1793

1793

由于AES算法的硬件實現較為復雜,在此提出一種優化算法中S—box和列混合單元的方法。其中S—box通過組合和有限域映射的方法進行優化,列混合單元使用算式重組的方法進行優化。這些優化設計通過組合邏輯

2021-01-25 14:27:14 20

20 ,通過Quartus II 7.1的綜合與仿真,以及在EP2S60F1020C4 FPGA目標器件上的實現結果表明,該方法能夠有效地減少硬件資源的使用且滿足高速實時性的要求。

2021-03-23 15:44:54 31

31 本文是本系列第五篇,本文書接上文,來討論如何具體地針對 SM3 算法的特點,優化計算架構,如通過 CSA 加法器來優化加法關鍵路徑等方法...

2022-02-07 11:40:04 0

0 本文是本系列第三篇,我們將通過分析一個 SM3 的開源硬件實現,來進一步了解算法的實現流程和硬件實現思路首發知乎作者:李凡

2022-02-07 11:40:34 1

1 本文是本系列第二篇,我們將通過分析一個 SM3 的開源軟件實現,來進一步了解算法的實現流程和軟件實現思路首發知乎:[鏈接]

2022-02-07 11:43:05 2

2 本文是本系列第一篇,筆者最近在研究基于FPGA的算法加速,本系列將以 PPT 結合文字的方式,以實現相對簡單的 SM3 雜湊算法為例,介紹一...

2022-02-07 11:43:35 1

1 極海APM32F407系列MCU,結合當前環境要求,設計出了支持國密算法(SM2,SM3,SM4)的IP, 符合國家密碼管理局認定和公布的密碼算法標準及其應用規范,并憑借顯著的性能優勢,已應用至新能源、工業控制、醫療設備等眾多領域。

2022-03-25 11:25:38 3653

3653 gitee-SM3-PHP.zip

2022-05-07 10:57:36 1

1 目的:實現上位機與FPGAuart交互

開發環境:quatus prime 18.1,芯片 altera :EP4CE15F23C8。

實驗現象: 1.使用uart:bps=9600(參數可調整

2023-05-08 10:28:33 2

2 數據填充:SM3算法要求將輸入數據填充為512比特的整數倍。填充方法是在數據末尾添加一個1和一些0,使得填充后的長度為512比特的整數倍。

2023-05-22 14:49:05 5437

5437 FPGA算法是指在FPGA(現場可編程門陣列)上實現的算法。FPGA是一種可重構的硬件設備,可以通過配置和編程實現各種不同的功能和算法,而不需要進行硬件電路的修改。

FPGA算法可以包括

2023-08-16 14:31:23 3882

3882

電子發燒友網站提供《SM320C6414-EP/SM320C6415-EP/SM320C6416-EP定點數字信號處理器數據表.pdf》資料免費下載

2024-08-02 13:10:34 0

0 電子發燒友網站提供《SM320C6711-EP,SM320C6711B-EP,SM320C6711C-EP,SM320C6711D-EP浮點數字信號處理器數據.pdf》資料免費下載

2024-08-03 10:07:12 0

0 電子發燒友網站提供《SM320F2808-EP,SM320F2806-EP,SM320F2801-EP數字信號處理器數據表.pdf》資料免費下載

2024-08-08 11:40:40 0

0 :?FPGA芯片采用了altera的Cyclon IV E系列的“EP4CE10F17C8”,軟件環境-Quartus-Ⅱ,采用的AD芯片為—AD-TLC549。 通過FPGA實現以下時序

2024-12-17 15:27:00 1613

1613

電子發燒友網為你提供AIPULNION(AIPULNION)FW2-24S15C3相關產品參數、數據手冊,更有FW2-24S15C3的引腳圖、接線圖、封裝手冊、中文資料、英文資料,FW2-24S15C3真值表,FW2-24S15C3管腳等資料,希望可以幫助到廣大的電子工程師們。

2025-03-20 18:30:00

harmony-utils之SM3,SM3工具類 harmony-utils 簡介與說明 harmony-utils 一款功能豐富且極易上手的HarmonyOS工具庫,借助眾多實用工具類,致力于助力

2025-06-28 18:37:25 783

783 隨著國家信息安全戰略的推進,國密算法在各類安全系統中的應用日益廣泛。GMSSL作為支持國密標準的重要工具庫,為開發者提供了SM2(非對稱加密)、SM3(哈希算法)和SM4(對稱加密)的完整實現。本文

2025-12-12 18:20:30 271

271

電子發燒友App

電子發燒友App

評論