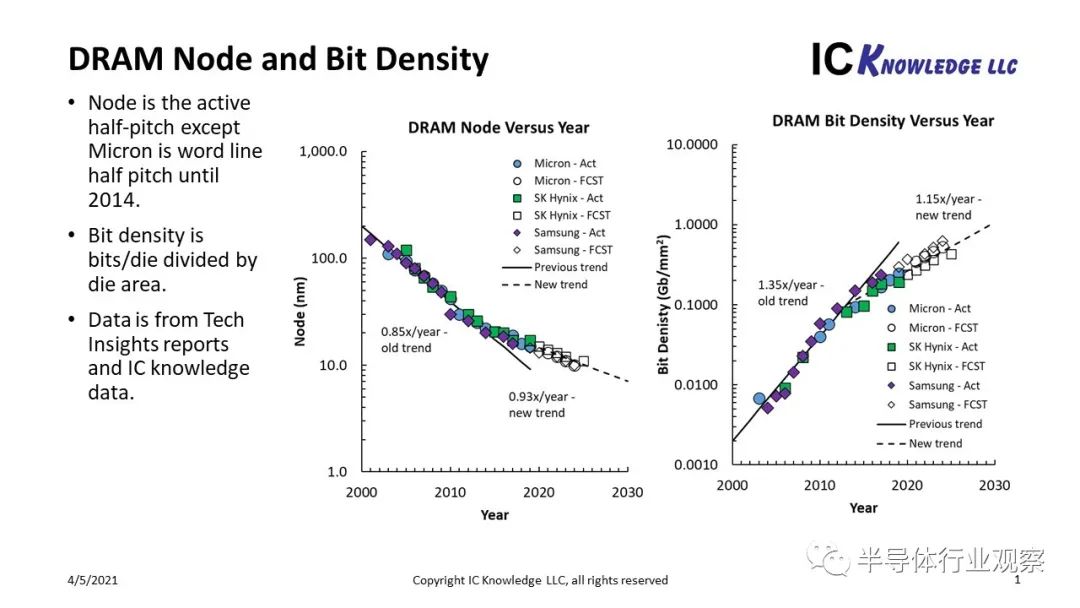

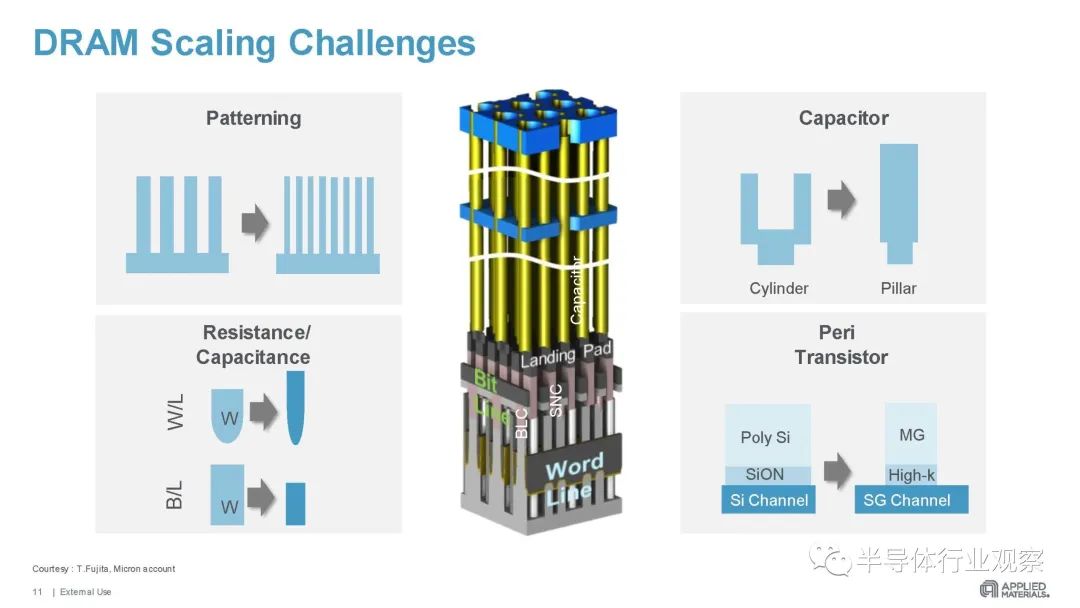

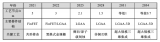

DRAM制造商正在進入下一階段的擴展,但是隨著存儲技術接近其物理極限,他們面臨著一些挑戰。 DRAM用于系統中的主存儲器,當今最先進的設備基于大約18nm至15nm的工藝。DRAM的物理極限約為

2019-11-25 11:33:18 6943

6943 據IHS公司的DRAM市場報告,隨著 DRAM 價格降到了極低水平,如果廠商不轉向效率更高的3x/2x納米制程,可能面臨重大虧損,三星電子等領先的內存供應商已經采用了上述制程。 三星第三季

2011-08-25 09:05:57 1422

1422

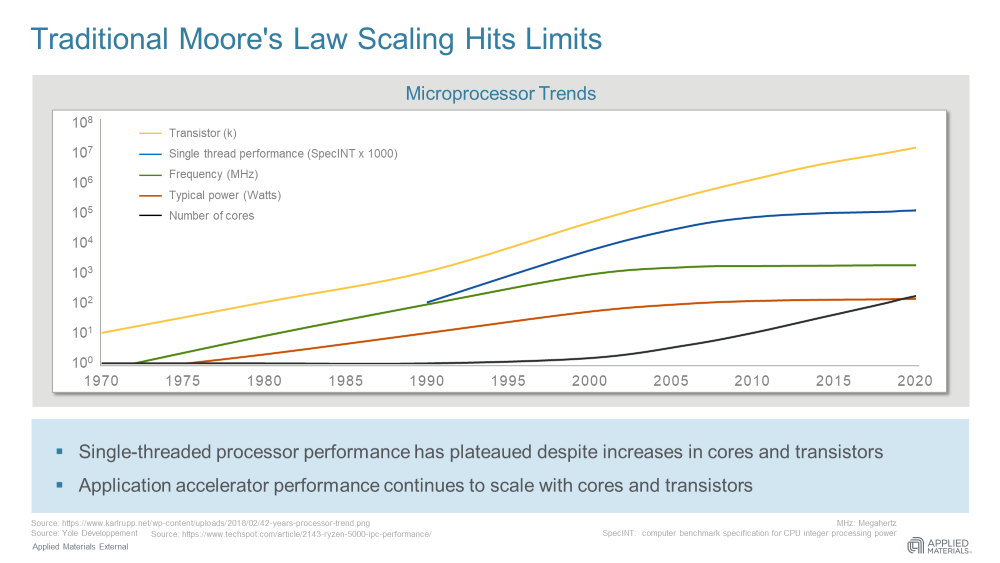

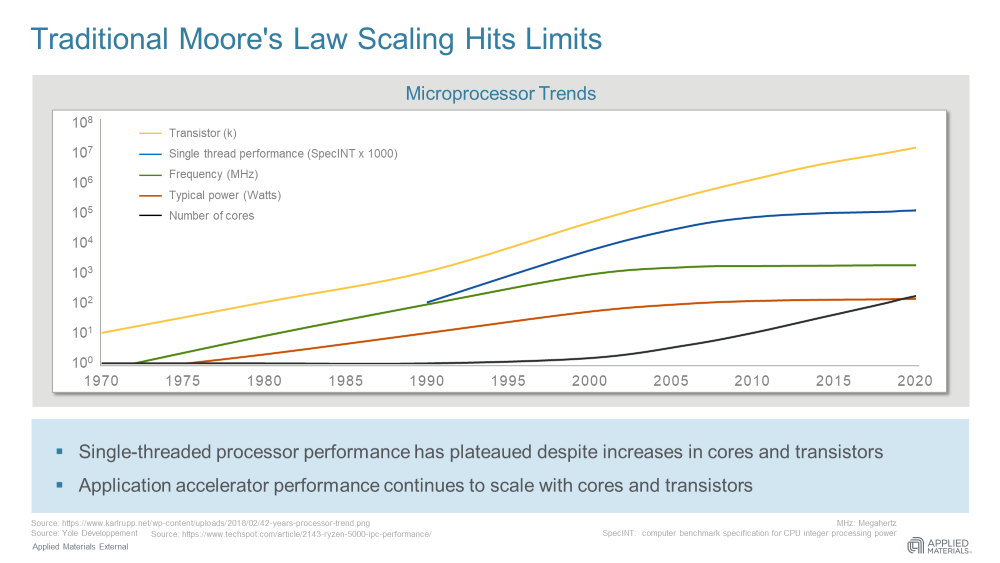

電子發燒友早八點訊:根據致力于規劃新版半導體發展藍圖的工程師所提供的白皮書,傳統的半導體工藝微縮預計將在2024年以前告終。值得慶幸的是,各種新型的組件、芯片堆棧和系統創新,可望持續使運算性能、功耗和成本受益。

2017-03-28 08:17:03 1462

1462

摘 要:針對半導體工藝與制造裝備的發展趨勢進行了綜述和展望。首先從支撐電子信息技術發展的角度,分析半導體工藝與制造裝備的總體發展趨勢,重點介紹集成電路工藝設備、分立器件工藝設備等細分領域的技術發展態勢和主要技術挑戰。

2023-05-23 15:23:47 2583

2583

本文概述了集成電路制造中的劃片工藝,介紹了劃片工藝的種類、步驟和面臨的挑戰。

2025-03-12 16:57:58 2798

2798

3D閃存有著更大容量、更低成本和更高性能的優勢,本文介紹了3D閃存的制造工藝與挑戰。

2025-04-08 14:38:39 2049

2049

美光宣布使用新型1α制造工藝生產的DRAM開始批量出貨,這是目前世界上最先進的DRAM制造技術。1α制造工藝最初會用于8Gb和16Gb的DDR4和LPDDR4內存生產上,隨著時間的推移,未來將用

2021-01-27 15:37:31 3660

3660 本文旨在對4G LTE和LTE-Advanced設備在制造和測試過程中會遇到的一些挑戰進行分析。這些挑戰既有技術方面的,也有經濟方面的。了解哪些缺陷需要檢測有助于我們在實際的生產環境中采用更好的測試

2019-07-18 06:22:43

小弟想知道8寸晶圓盒的制造工藝和檢驗規范,還有不知道在大陸有誰在生產?

2010-08-04 14:02:12

NIST相機是由哪些部分組成的?NIST相機有什么作用?制造NIST相機面臨的主要挑戰是什么?如何去解決?

2021-07-09 06:58:12

本文討論 IC制造商用于克服精度挑戰的一些技術,并讓讀者更好地理解封裝前和封裝后用于獲得最佳性能的各種方法,甚至是使用最小體積的封裝。

2021-04-06 07:49:54

PCB制造工藝中底片變形原因(1)溫濕度控制失靈 (2)曝光機溫升過高 解決方法: (1)通常情況下溫度控制在22±2℃,濕度在55%±5%RH。 (2)采用冷光源或有冷卻裝置的曝機及不斷更換備份底片

2011-10-19 16:20:01

PCB制造工藝流程是怎樣的?

2021-11-04 06:44:39

`<p><font face="Verdana"><strong>PCB制造

2009-10-21 09:42:26

一、PCB制造基本工藝及目前的制造水平

PCB設計最好不要超越目前廠家批量生產時所能達到的技術水平,否則無法加工或成本過高。

1.1層壓多層板工藝

層壓多層板工藝是目前廣泛

2023-04-25 17:00:25

高速模擬IO、甚至一些射頻電路集成在一起,只要它不會太復雜。 由于工藝技術的不兼容性,RF集成通常被認為是一種基本上尚未解決的SoC挑戰。在數字裸片上集成RF電路會限制良品率或導致高昂的測試成本,從而

2019-07-05 08:04:37

XX nm制造工藝是什么概念?為什么說7nm是物理極限?

2021-10-20 07:15:43

everspin生態系統和制造工藝創新

2021-01-01 07:55:49

`《半導體制造工藝》學習筆記`

2012-08-20 19:40:32

`書籍:《炬豐科技-半導體工藝》文章:GaN 納米線制造和單光子發射器器件應用的蝕刻工藝編號:JFSJ-21-045作者:炬豐科技網址:http://www.wetsemi.com

2021-07-08 13:11:24

`書籍:《炬豐科技-半導體工藝》文章:IC制造工藝編號:JFSJ-21-046作者:炬豐科技網址:http://www.wetsemi.com/index.html摘要:集成電路的制造主要包括以下工藝

2021-07-08 13:13:06

今天閱讀了最感興趣的部分——芯片制造過程章節,可以用下圖概括:

芯片的制造工序可分為前道工序和后道工序。前道工序占整個芯片制造80%的工作量,由數百道工藝組成,可見芯片制造過程的復雜程度,這么多

2024-12-30 18:15:45

三星電子近日在國際學會“IEDM 2015”上就20nm工藝的DRAM開發發表了演講。演講中稱,三星此次試制出了20nm工藝的DRAM,并表示可以“采用同樣的方法,達到10nm工藝”。 國際電子器件

2015-12-14 13:45:01

什么是數碼功放?淺談數碼功放

2021-06-07 06:06:15

PCB的制造技術受到廣泛關注。剛柔結合PCB的制造工藝:Rigid-Flex PCB,即RFC,是將剛性PCB與柔性PCB結合在一起的印刷電路板,它可以通過PTH形成層間傳導。剛柔性PCB的簡單制造

2019-08-20 16:25:23

。例如實現半導體制造設備、晶圓加工流程的自動化,目的是大幅度減少工藝中的操作者,因為人是凈化間中的主要沾污源。由于芯片快速向超大規模集成電路發展,芯片設計方法變化、特征尺寸減小。這些變化向工藝制造提出挑戰

2020-09-02 18:02:47

今日分享晶圓制造過程中的工藝及運用到的半導體設備。晶圓制造過程中有幾大重要的步驟:氧化、沉積、光刻、刻蝕、離子注入/擴散等。這幾個主要步驟都需要若干種半導體設備,滿足不同的需要。設備中應用較為廣泛

2018-10-15 15:11:22

雙面FPC制造工藝FPC開料-雙面FPC制造工藝除部分材料以外,柔性印制板所用的材料基本都是卷狀的。由于并不是所有的工序都一定要用卷帶工藝進行加工,有些工序必須裁成片狀才能加工,如雙面柔性印制板

2019-01-14 03:42:28

本帖最后由 王棟春 于 2021-1-9 22:25 編輯

變壓器制造技術叢書 絕緣材料與絕緣件制造工藝 資料來自網絡資源分享

2021-01-09 22:23:35

變壓器鐵心制造工藝:變壓器鐵心是變壓器的心臟,它的制造質量直接影響到變壓器的技術性能、經濟指標和運行的安全可靠程序,因此它的制造技術和質量控制十分重要。變壓器鐵心制造工藝此書共分六章:第一章?變壓器

2008-12-13 01:31:45

請教大神在PCB制造中預防沉銀工藝缺陷的措施有哪些?

2021-04-25 09:39:15

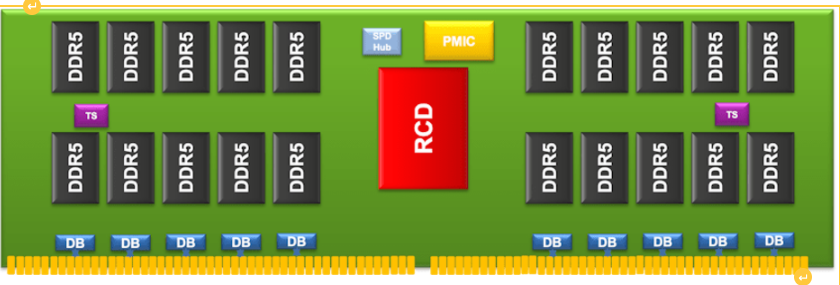

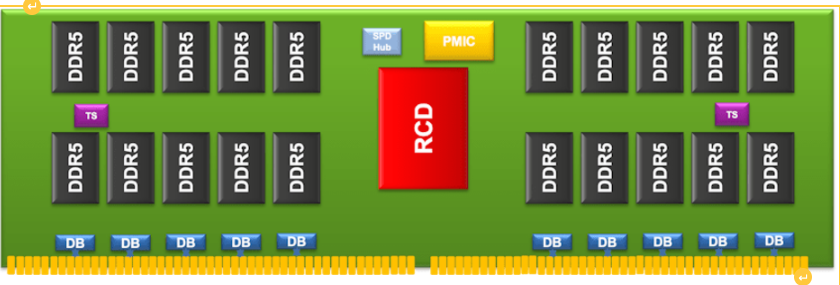

本文探討了幾個設計考量和方法用以緩解GDDR6 DRAM實施所帶來的挑戰。特別指出了在整個接口通道保持信號完整性的重要性。必須特別重視GDDR6存儲器接口設計的每個階段,才能夠成功解決信號完整性

2021-01-01 06:29:34

如何解決PCB制造中的HDI工藝內層漲縮對位問題呢?

2023-04-06 15:45:50

雙極晶體管性能特點是什么如何采用BiCom3工藝制造出一款功能豐富的電壓反饋放大器?

2021-04-20 06:56:40

嵌入式系統制造商面臨的IP安全性的挑戰防止發生未經授權的固件訪問隱藏模擬與數字資源及其互聯方式

2021-03-02 06:49:38

`?隨著摩爾定律,半導體工藝從1微米(um)、0.5微米(um)、0.13微米(um)不斷微縮到奈米(nm)等級,如此先進工藝的電路修補,考驗FIB實驗室的技術發展及應用能力。特別當工藝來到16奈米

2020-05-14 16:26:18

的制造工藝,也討論了如何慎重地選擇測試軟件和硬件。三個最重要的最佳實踐包括:? 可制造性設計和調試? 編寫可擴展且可復用的測試代碼? 復制開發過程中各個階段的物理制造環境為了了解從產品設計到產品測試

2019-05-28 07:30:54

3D NAND的制程轉換及新產能布建,在DRAM的投資則全數集中在1X奈米的制程微縮,并無任何新產能。也因此,雖然第二季是傳統淡季,但因DRAM制程由20奈米微縮到1X奈米時遇到瓶頸,市場供給仍有吃緊

2017-06-13 15:03:01

IC尺寸微縮仍面臨挑戰。為了使芯片微縮,總是利用光刻技術來推動。然而近期Sematech在一次演講中列舉了可維持摩爾定律的其他一些技術。1. 零低k界面:在目前Intel的45nm設計中,采用硅襯底

2014-01-04 09:52:44

機械制造工藝學緒論 第一章 概述 第一節 機械制造工藝學的研究對象第二節 基本概念和定義第二章 工藝規程的制訂第一節 毛坯的選擇第二節 工件的裝夾第三節 定位基準的選擇第四節 工藝路線的擬定第五節

2008-06-17 11:41:30

芯片制造-半導體工藝制程實用教程學習筆記[/hide]

2009-11-18 11:44:51

芯片制造全工藝流程詳情

2020-12-28 06:20:25

表面安裝pcb設計工藝淺談

2012-08-20 20:13:21

芯片制造工藝流程

2019-04-26 14:36:59

霍爾IC芯片的制造工藝霍爾IC傳感器是一種磁性傳感器,通過感應磁場的變化,輸出不同種類的電信號。霍爾IC芯片主要有三種制造工藝,分別為 Bipolar、CMOS 和 BiCMOS 工藝,不同工藝的產品具有不同的電參數與磁參數特性。霍爾微電子柯芳(***)現為您分別介紹三種不同工藝產品的特點。

2016-10-26 16:48:22

熱處理工藝正面臨來自高k和其它材料、超淺接合、應變硅、SOI,以及不斷微縮生產更高效率和更加復雜的器件所帶來的挑戰。盡管我們在技術開發中盡量避免使用新材料,但是當現

2009-12-21 11:41:45 13

13 綠色制造帶來多種挑戰 破解工藝成本難題

電子產品生產禁用的有害物質導致企業成本上升、加工難度加大以及產品質量下降,這對電子元件

2009-11-12 17:11:24 1350

1350 三星加速制程微縮 DRAM進入40納米世代

三星電子(Samsung Electronics)加速制程微縮,積極導入40納米制程,第4季已開始小幅試產DDR3,預計2010年下半40納米將成為主流制程

2009-11-18 09:20:55 645

645 臺積電(TSMC)表示在接下來十年以FinFET技術持續進行半導體制程微縮的途徑是清晰可見的,可直達 7nm節點;但在 7nm節點以下,半導體制程微縮的最大挑戰來自于經濟,并非技術。

2011-11-01 09:34:33 1679

1679 半導體產業正在面臨一項挑戰,即每兩年微縮晶片特徵尺寸的週期已然結束,我們正在跨入一個情勢高度不明的階段。業界目前面臨的幾項關鍵挑戰都顯示,晶片微縮的路程愈來愈艱困

2012-03-23 08:45:58 994

994

晶圓制造總的工藝流程 芯片的制造過程可概分為晶圓處理工序(Wafer Fabrication)、晶圓針測工序(Wafer Probe)、構裝工序(Packaging)、測試工序(Initial Test and Final Test)等幾個步驟。

2018-04-16 11:27:00 15246

15246 在集成電路制造工藝升級的過程中,High-K和FinFET的出現對摩爾定律的延續發生了重要的作用,并一再打破了過去專家對行業的預測。近年來,隨著工藝的進一步演進,業界又開始產生了對晶體管能否繼續縮進產生了疑惑。

2018-03-12 11:00:24 7093

7093 Sanjay Mehrotra曾表示,在EUV光刻工藝上,他認為EUV光刻機在DRAM芯片制造上不是必須的,至少在1α及1β工藝之前不會用到它。

早前ASML提到

2018-08-20 17:41:49 1479

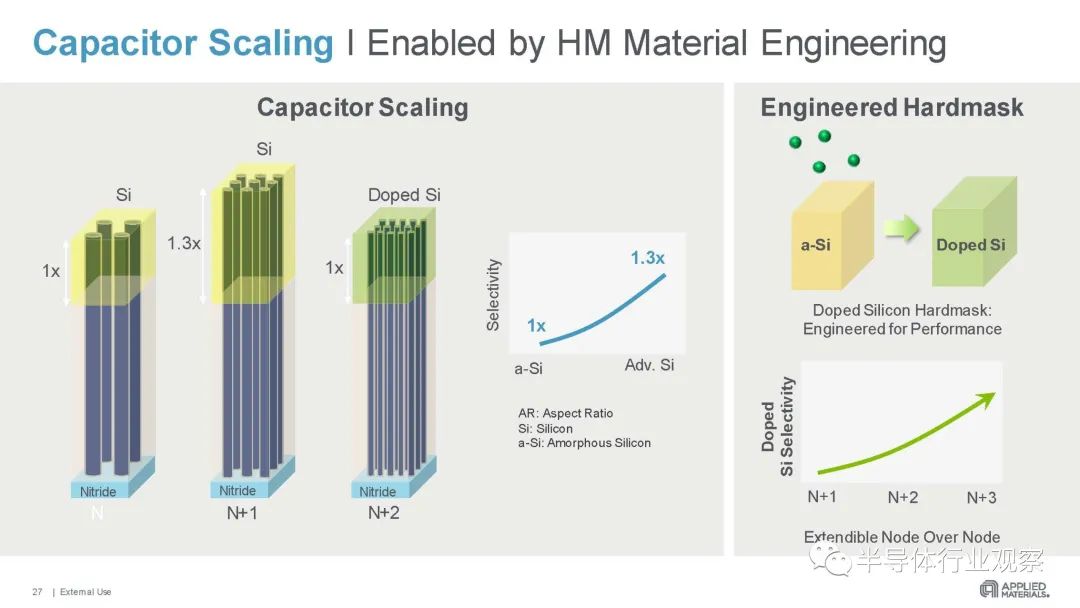

1479 就算3D NAND的每位元成本與平面NAND相比較還不夠低,NAND快閃存儲已經成功地由平面轉為3D,而DRAM還是維持2D架構;在此同時,DRAM制程的微縮也變得越來越困難,主要是因為儲存電容的深寬比(aspect ratio)隨著元件制程微縮而呈倍數增加。

2018-10-28 10:17:13 5623

5623 過去的一年,包括AR、VR這些智能穿戴的應用,對高分辨率的微型顯示帶來了一些需求,催生了新型顯示技術的發展。隨著LED芯片微縮化的發展,MiniLED、MicroLED成為行業熱點,并給LED產業發展帶來了新的機遇和挑戰。

2019-01-23 10:06:16 8008

8008 DRAM制造商采用EUVL工具很可能與邏輯生產商(臺積電,三星代工(邏輯芯片的合約制造商,而不是DRAM制造商)的采用類似):最初的EUV設備將僅用于幾層,隨著工藝節點的增加,層數逐漸增加。ASML估計,對于DRAM,一個EUV層每月需要每100,000個晶圓啟動1.5到2個EUV系統。

2019-08-27 10:36:13 4037

4037 半導體存儲器已經得到了廣泛的應用,其中DRAM和SRAM是兩種常見形態的存儲器。DRAM的特點是需要定時刷新,才可以保存數據,SRAM只要存入數據了,不刷新也不會丟掉數據。DRAM和SRAM各有各的優勢及不足,本文探討的DRAM和NAND當前面臨的技術挑戰及發展前景。

2020-07-22 14:04:19 2373

2373 那么,這些新興存儲技術為什么會如此受期待呢?主要原因在于:隨著半導體制造技術持續朝更小的技術節點邁進,傳統的DRAM和NAND Flash面臨越來越嚴峻的微縮挑戰,DRAM 已接近微縮極限,而NAND Flash則朝3D方向轉型。

2020-08-17 15:05:17 2723

2723 那么,這些新興存儲技術為什么會如此受期待呢?主要原因在于:隨著半導體制造技術持續朝更小的技術節點邁進,傳統的DRAM和NANDFlash面臨越來越嚴峻的微縮挑戰,DRAM已接近微縮極限,而NANDFlash則朝3D方向轉型。

2020-09-11 11:46:06 1597

1597 了更高深寬比圖形刻蝕工藝上的挑戰,同時將更多的階梯連接出來也更加困難。人們通過獨特的整合和圖案設計方案來解決工藝微縮帶來的挑戰,但又引入了設計規則方面的難題。

2020-12-25 11:23:00 4

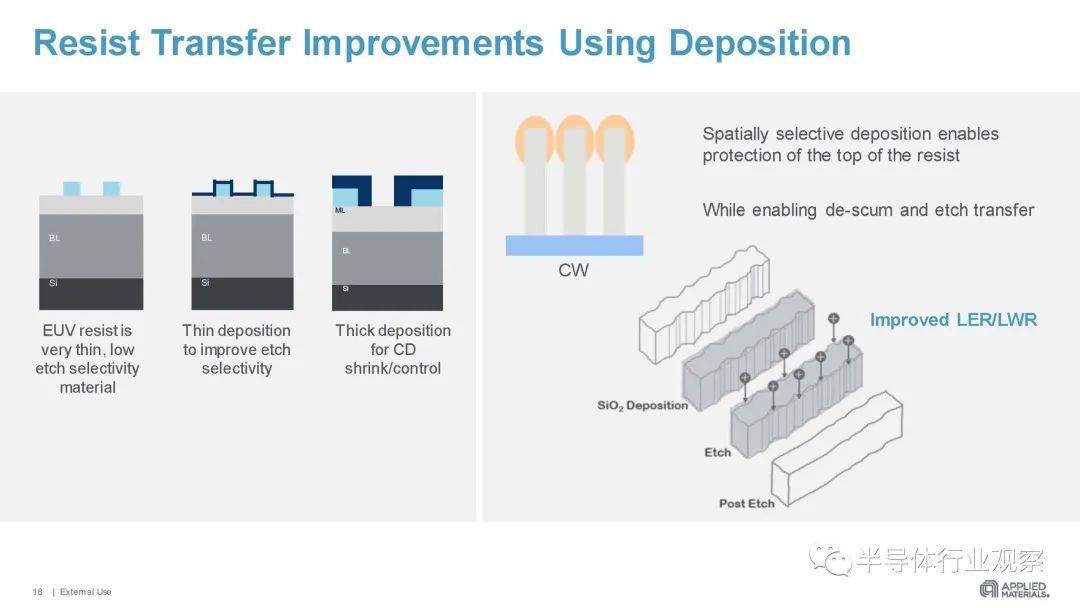

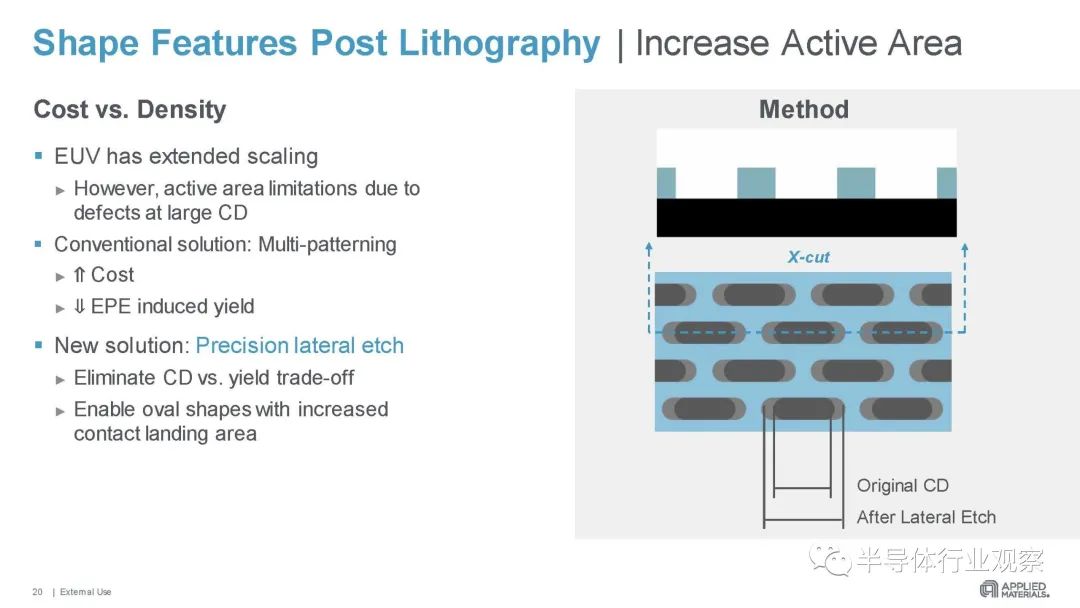

4 近期筆者在清洗業務研討會上發表了演講。我不是一名清洗工藝專家,在演講中介紹更多的是制造工藝的發展趨勢及其對清洗的影響。我將在這篇文章中分享并進一步討論那次演講的內容,主要圍繞DRAM、邏輯器件和NAND這三大尖端產品。

2020-12-26 01:23:08 974

974 美光本周二公布其用于DRAM的1α新工藝,該技術有望將DRAM位密度提升40%,功耗降低15%。 1α工藝最初被用于生產DDR4和LPDDR4內存,未來或將但覆蓋美光所有類型的DRAM。

2021-01-29 15:03:44 2841

2841 阻抗損耗的設計制造挑戰說明。

2021-05-19 15:12:56 5

5 MICRON最近宣布,我們正在發貨使用全球最先進的DRAM工藝制造的存儲芯片。這個過程被神秘地稱為“1α”(1-alpha)。這是什么意思,有多神奇?

2021-09-15 17:00:52 2714

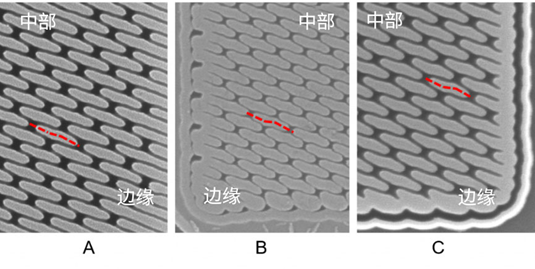

2714 (AA) 尺寸和形狀則是影響良率和性能的重要因素。在本研究中,我們將為大家呈現,如何利用SEMulator3D研究先進DRAM工藝中存在的AA形狀扭曲和與之相關的微負載效應與制造變量。

2022-08-01 10:22:26 1686

1686

SK海力士全球首次在移動端DRAM采用了“HKMG(High-K Metal Gate)”*工藝,成功研發出了LPDDR5X(Low Power Double Data Rate 5X),并于近期

2022-11-11 10:41:26 2191

2191

以往,具備低漏電、高性能特性的先進制程工藝多用于邏輯芯片,特別是PC、服務器和智能手機用CPU,如今,這些工藝開始在以DRAM為代表的存儲器中應用,再加上EUV等先進設備和工藝的“互通”,邏輯芯片和存儲器的制程節點和制造工藝越來越相近。

2022-11-17 11:10:08 3685

3685 深寬比圖形刻蝕工藝上的挑戰,同時將更多的階梯連接出來也更加困難。人們通過獨特的整合和圖案設計方案來解決工藝微縮帶來的挑戰,但又引入了設計規則方面的難題。

2023-01-06 15:27:02 1781

1781 為了保持數據,DRAM使用電容存儲,所以必須隔一段時間刷新(refresh)一次,如果存儲單元沒有被刷新,存儲的信息就會丟失。

2023-01-09 14:18:43 16207

16207 槽(Deep Tench)式存儲單元和堆疊(Slack)式電容存儲單元。 70nm 技術節點后,堆疊式電容存儲單元逐漸成為業界主流。為了使系統向更高速、高密度、低功耗不斷優化,DRAM存儲單元也在不斷微縮(如14nm 工藝節點)。

2023-02-08 10:14:57 12490

12490 隨著晶體管尺寸的不斷微縮,晶圓制造工藝日益復雜,對半導體濕法清洗技術的要求也越來越高。

2023-08-01 10:01:56 6690

6690

內存芯片在驅動ic市場和ic技術發展方面發揮了重要作用。市場上兩個主要的內存產品分別是DRAM和NAND。

2023-09-01 09:43:09 10429

10429

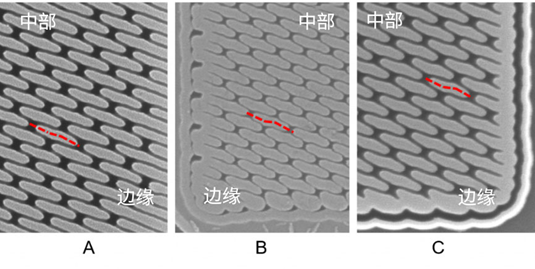

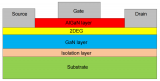

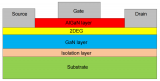

在下面的圖中較為詳細的顯示了堆疊式DRAM單元STI和阱區形成工藝。下圖(a)為AA層版圖,虛線表示橫截面位置。

2023-09-04 09:32:37 6531

6531

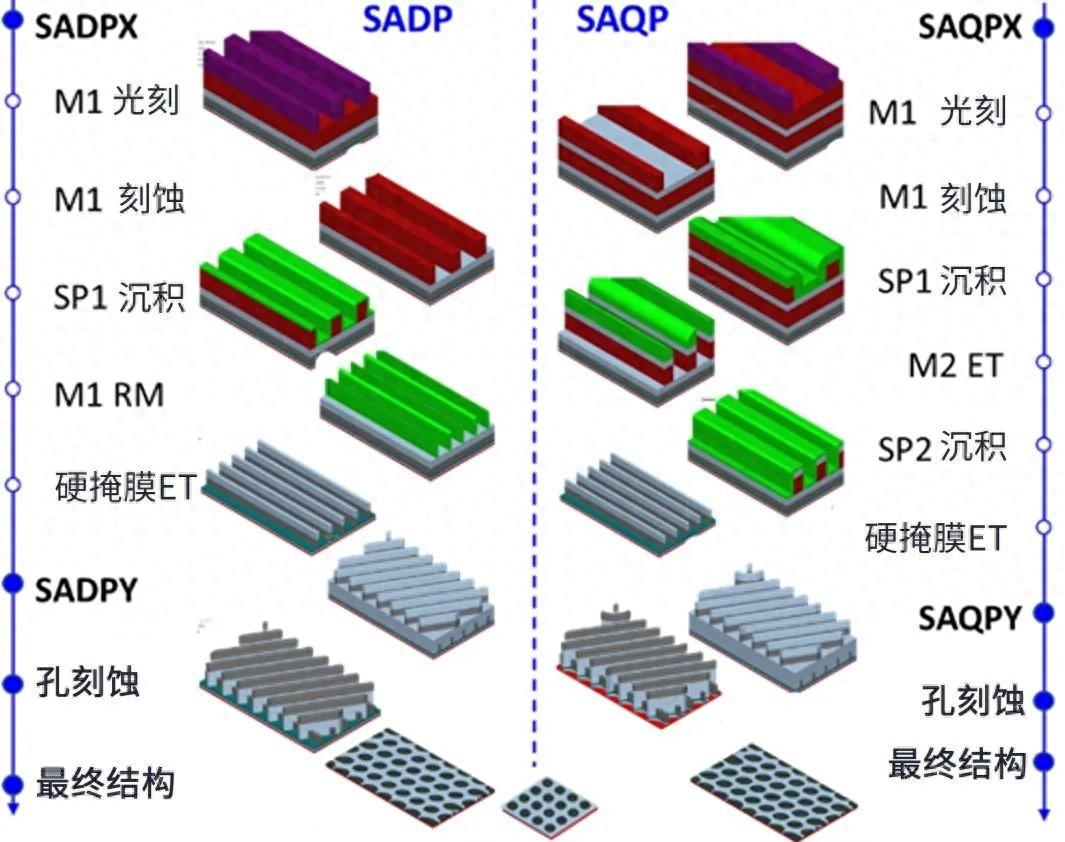

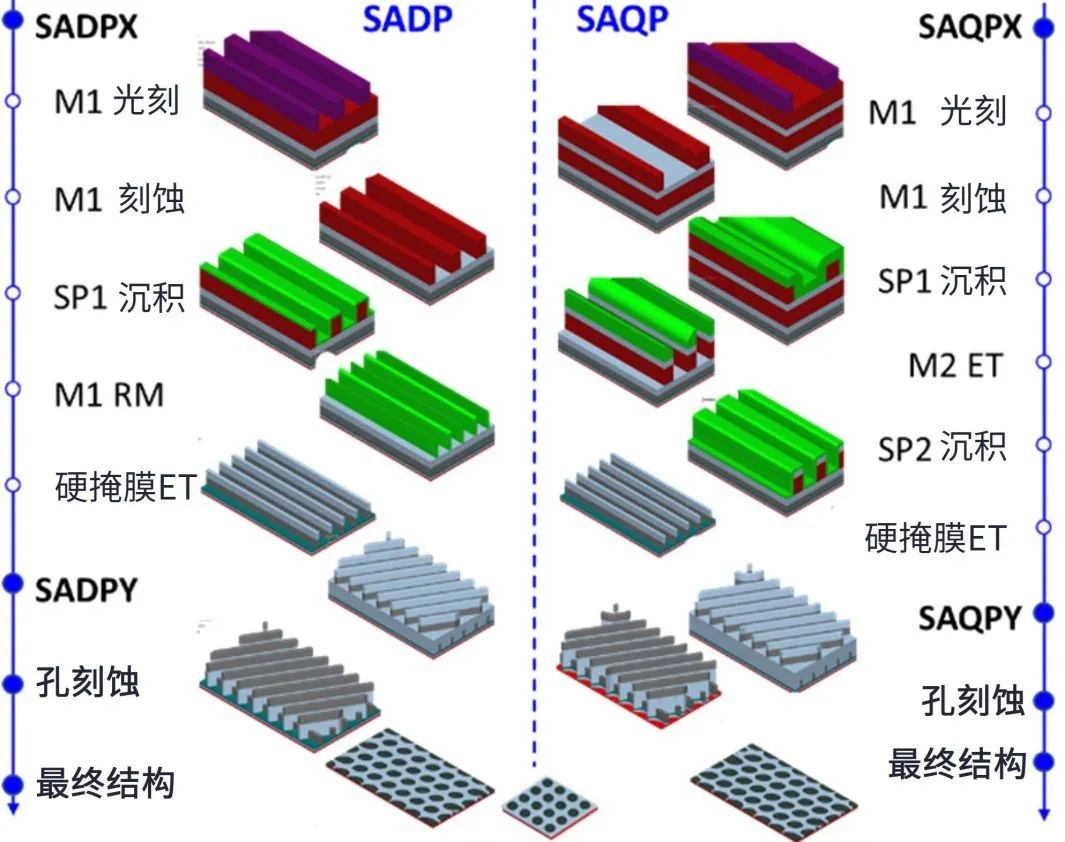

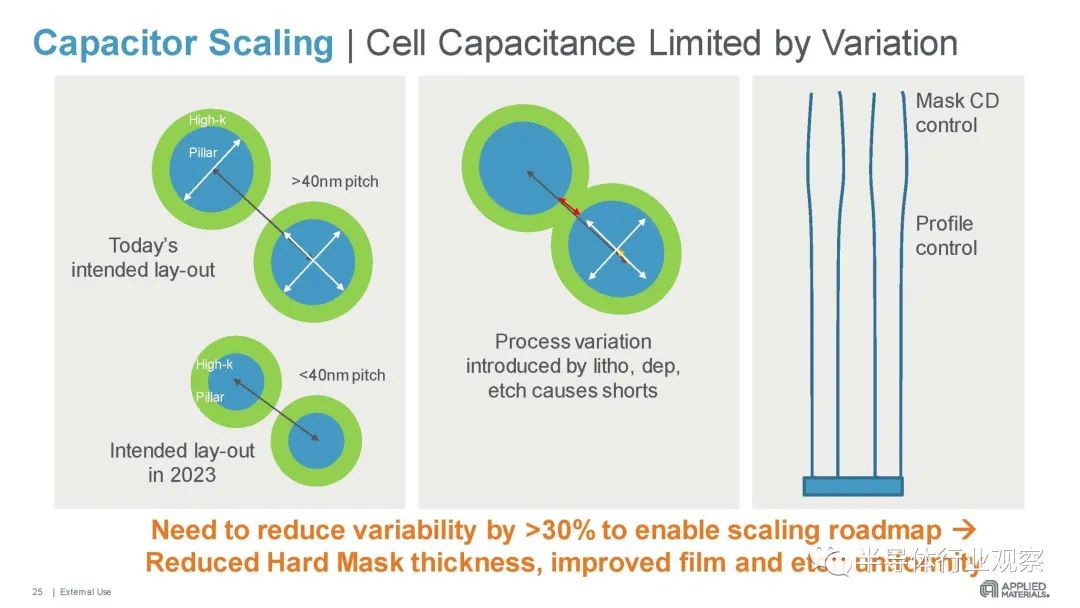

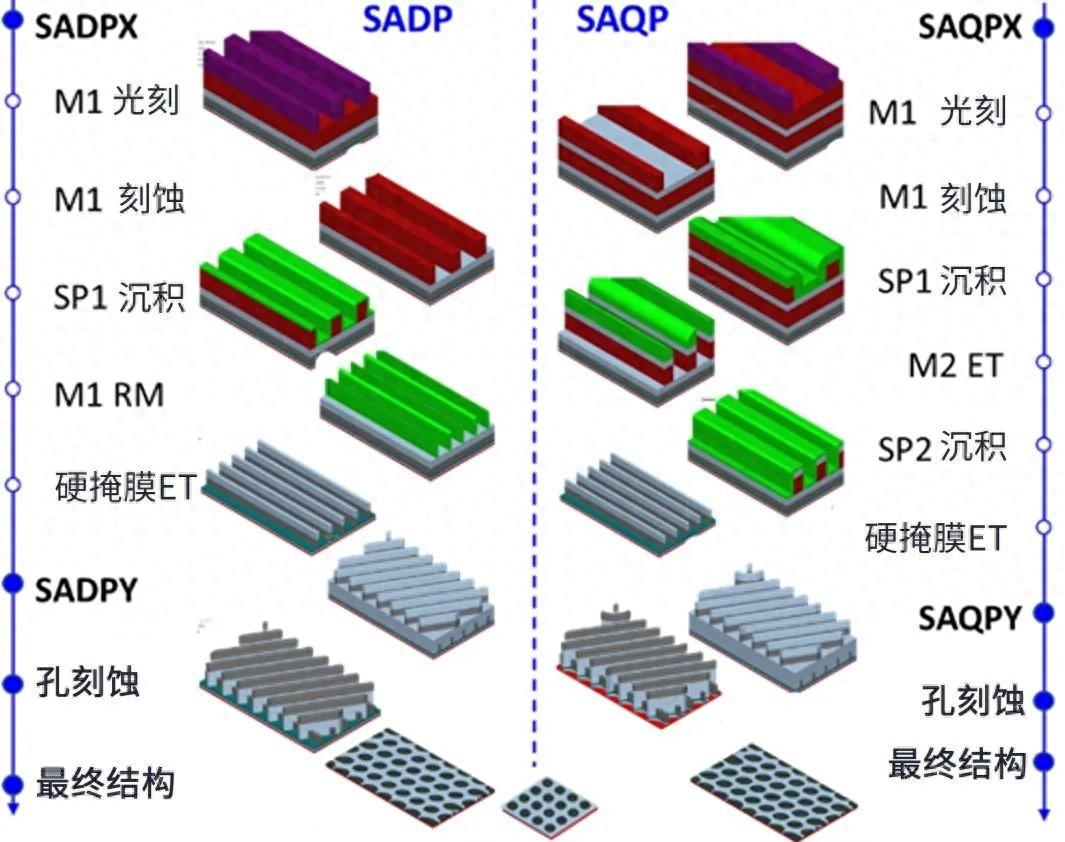

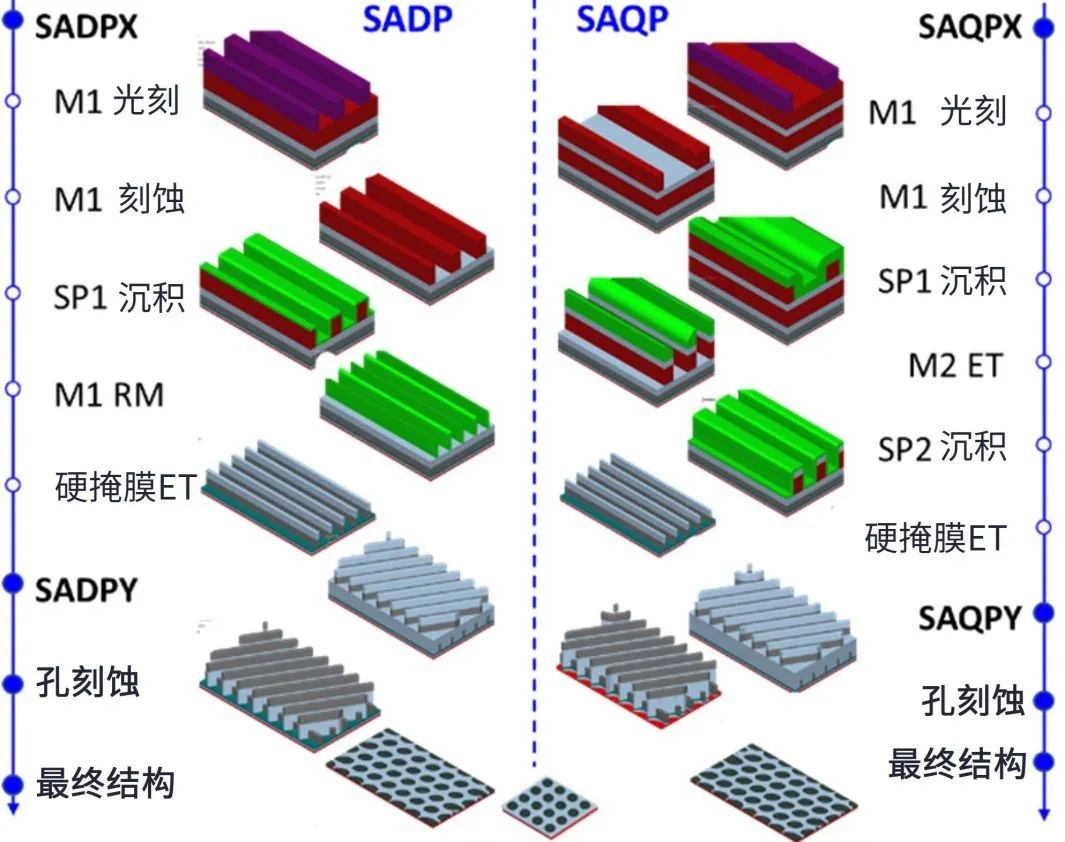

持續的器件微縮導致特征尺寸變小,工藝步驟差異變大,工藝窗口也變得越來越窄[1]。半導體研發階段的關鍵任務之一就是尋找工藝窗口較大的優秀集成方案。如果晶圓測試數據不足,評估不同集成方案的工藝窗口會變得困難。為克服這一不足,我們將舉例說明如何借助虛擬制造評估 DRAM 電容器圖形化工藝的工藝窗口。

2023-11-16 16:55:04 1194

1194

芯片制造商正在使用更多的DRAM。在某些情況下,DRAM——尤其是高帶寬存儲器(HBM)——正在取代一些SRAM。DRAM在耐用性方面有著良好的記錄,也有成熟的工藝,而且比SRAM便宜得多

2023-11-22 16:36:08 1834

1834

以工藝窗口建模探索路徑:使用虛擬制造評估先進DRAM電容器圖形化的工藝窗口

2023-11-23 09:04:42 1249

1249

應對傳統摩爾定律微縮挑戰需要芯片布線和集成的新方法

2023-12-05 15:32:50 1093

1093

近期的演示會上,美光詳細闡述了其針對納米印刷與DRAM制造之間的具體工作模式。他們提出,DRAM工藝的每一個節點以及浸入式光刻的精度要求使得物理流程變得愈發復雜。

2024-03-05 16:18:24 1316

1316 旋轉花鍵的制造工藝是一門精細的技術,涉及多個步驟和精細的操作,以確保最終產品的質量和性能,下面簡單介紹下旋轉花鍵的制造工藝。

2024-03-16 17:39:17 1110

1110

關于各個細分領域,有觀點指出,PC DRAM買家將在第二季度加大DDR5的采購量,由于存儲芯片生產商正大規模轉向更高級別的制造工藝,其收益得到顯著改善。但是,機構預期PC DRAM第二季度合約價環比漲幅為3%——8%,而其中DDR5的漲幅則將略有收縮。

2024-03-26 15:58:46 819

819 在機遇與挑戰并存的AI時代,三星如何在DRAM領域開拓創新?

2024-05-09 18:46:35 924

924

電機作為現代工業中不可或缺的動力設備,其制造工藝的優劣直接影響到電機的性能、質量和可靠性。電機的制造工藝涵蓋了多個環節,包括機加工、鐵芯制造、繞組制造、轉子制造以及電機裝配等。本文將詳細探討電機的制造工藝,以期為電機的設計、制造和質量控制提供有益的參考。

2024-06-14 11:49:22 5548

5548 )工藝成本的不斷攀升,自1c DRAM商業化以來,傳統制造工藝的經濟性正受到嚴峻挑戰。因此,公司決定嘗試4F2結構DRAM,旨在通過技術創新來縮減成本。

2024-08-14 17:06:43 1670

1670 近日,據韓媒最新報道,三星電子在面對其12nm級DRAM內存產品的良率和性能雙重困境時,已于2024年底作出了重要決策。為了改善現狀,三星決定在優化現有1b nm工藝的基礎上,全面重新設計新版1b

2025-01-22 14:04:07 1411

1411 FOPLP 技術目前仍面臨諸多挑戰,包括:芯片偏移、面板翹曲、RDL工藝能力、配套設備和材料、市場應用等方面。

2025-07-21 10:19:20 1280

1280

制造氮化鎵(GaN)高電子遷移率晶體管(HEMTs)具有一定難度,這主要歸因于材料本身以及制造工藝中的多項挑戰。

2025-07-25 16:30:44 4490

4490

電子發燒友App

電子發燒友App

評論