Block實現(xiàn)32位單精度浮點的卷積運算,而針對定點及低精度的浮點運算,則需要對硬浮點DSP Block進行相應(yīng)的替換即可。

2018-07-23 09:09:45 8401

8401

大部分運算可以通過擴位和近似的方式轉(zhuǎn)換為定點運算。但有些算法在設(shè)計在設(shè)計的過程中就涉及大量的浮點運算,在轉(zhuǎn)換為定點運算時比較麻煩,會帶來龐大的工作量。

2022-09-08 15:41:56 3509

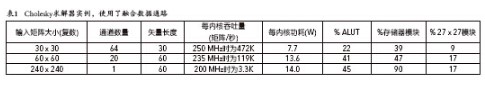

3509 語言編寫的浮點矩陣相乘處理單元[1],其關(guān)鍵技術(shù)是乘累加單元的設(shè)計,這樣設(shè)計的硬件,其性能依賴于設(shè)計者的編程水平。此外,F(xiàn)PGA廠商也推出了一定規(guī)模的浮點矩陣運算IP核[2],雖然此IP核應(yīng)用了本廠家的器件,并經(jīng)過專業(yè)調(diào)試和硬件實測,性能穩(wěn)定且優(yōu)于手寫代碼,但仍可對其進行改進,以進一步提高運算速度。

2019-08-22 06:41:38

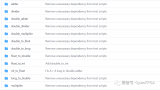

Altera_IP核,僅供參考

2016-08-24 16:57:15

浮點運算單元的設(shè)計和優(yōu)化可以從以下幾個方面入手:

1.浮點寄存器設(shè)計:為了實現(xiàn)浮點運算指令子集(RV32F或者RV32D),需要添加一組專用的浮點寄存器組,總共需要32個通用浮點寄存器。其中

2025-10-22 07:04:49

詳解浮點運算的定點編程

2021-04-02 06:59:52

嗨,我在我的應(yīng)用程序中使用PIC32 MX250F256H控制器。我面臨著浮點運算的一些問題。浮點F=0in主體(){f=(浮點)(47.171143947.0);}我應(yīng)該得到f=0.1711439

2018-10-08 15:55:49

fpga),現(xiàn)在需要完成一個cpu/fpga協(xié)同工作的任務(wù),使用pcie總線通信。具體任務(wù)很簡單:cpu通過pcie傳兩個32位浮點數(shù)給fpga,fpga相乘然后把結(jié)果返回。乘法模塊使用quartus提供

2014-12-21 21:32:14

摘要:

本文主要描述浮點數(shù)是如何實現(xiàn)開平方運算的。

簡介

事實上,浮點數(shù)的開平方運算結(jié)構(gòu)與定點數(shù)甚至整數(shù)的開平方運算結(jié)構(gòu)是十分相似的,我們可以在對定點數(shù)求平方根運算結(jié)構(gòu)的基礎(chǔ)上,針對階碼域進行

2025-10-24 08:42:22

使用c6678進行浮點除法運算的時間測試的時候(使用clock),發(fā)現(xiàn)(使用c6678evm板)運行時間很長,運算時間達到七百多個時鐘周期。請問是什么原因?c6678本身的浮點除法能達到什么樣的運算速度呢?

2018-06-21 13:49:31

在《ARM微控制器基礎(chǔ)與實戰(zhàn)》的 2.6.3 節(jié)有說到"浮點數(shù)寄存器(F0-F7...)",2104是否具有這些寄存器如果 EasyArm 不支持浮點運算,而我的程序需要用到浮點運算,請問可以實現(xiàn)嗎

2022-11-07 15:24:11

求用verilog實現(xiàn)浮點數(shù)運算的資料,謝謝

2016-12-17 21:15:52

FPGA 如何進行浮點運算

2015-09-26 09:31:37

最近出現(xiàn)的 FPGA設(shè)計工具和 IP有效減少了計算占用的資源,大大簡化了浮點數(shù)據(jù)通路的實現(xiàn)。而且,與數(shù)字信號處理器不同, FPGA能夠支持浮點和定點混合工作的 DSP數(shù)據(jù)通路,實現(xiàn)的性能超過

2019-08-13 06:42:48

TI的各位工程師及各位飄過的仁兄好:

?????? 話說我用138中的6748內(nèi)核做浮點運算,測得一次32位的浮點運算竟用了100多個clock,兩百多微妙啊……甚是吃驚,坊間傳聞6748一個

2018-06-21 06:36:58

Vivado浮點數(shù)IP核的握手信號

我們的設(shè)計方案中,F(xiàn)PU計算單元將收到的三條數(shù)據(jù)和使能信號同步發(fā)給20多個模塊,同時只有一個模塊被時鐘使能,進行計算,但結(jié)果都會保留,發(fā)給數(shù)選。計算單元還需接受

2025-10-24 07:01:36

HI論壇,在我的方式三相交流感應(yīng)電機控制,我遇到的文件“GS00 4”。它提到了一點“分數(shù)乘法”,這是在匯編指令“MPY”中完成的。dsPIC的核心不支持浮點運算,但DSC部分支持浮點運算,對嗎?為什么XC16不定期使用這個芯片中可用的浮點命令?對我來說,壓倒性的參數(shù)對我來說并不重要。

2020-04-02 10:06:31

labview怎樣實現(xiàn)矩陣相乘A是nxm矩陣,B是mxp矩陣,如何實現(xiàn)C=AB;

2012-12-12 21:02:32

RISC-V浮點運算單元(floating-point unit,簡稱FPU)是一種專門用于執(zhí)行浮點運算的硬件加速器,其作用是提高浮點運算速度,在科學(xué)計算、圖像處理和機器學(xué)習等應(yīng)用領(lǐng)域有著廣泛

2025-10-21 14:46:51

stm32f103浮點運算(支持單精度和雙精度)本章主要講解實數(shù)浮點FTT,支持單精度和雙精度。目錄31.1 初學(xué)者重要提示31.2 實數(shù)浮點FFT說明31.3 單精度函數(shù)

2021-08-10 06:22:04

Verilog可以通過使用IEEE標準的浮點數(shù)表示來實現(xiàn)浮點運算。下面是一個基本的Verilog模塊示例,展示了如何進行加法、乘法和除法等常見的浮點運算操作:

module

2024-03-25 21:49:34

兩單精度浮點數(shù)相乘是先轉(zhuǎn)換成二進制再相乘還是直接相乘,求教思路或程序

2016-10-23 23:36:36

處理系統(tǒng)中最重要的部件之一。FPGA是當前數(shù)字電路研究開發(fā)的一種重要實現(xiàn)形式,它與全定制ASIC電路相比,具有開發(fā)周期短、成本低等優(yōu)點。但多數(shù)FPGA不支持浮點運算,這使FPGA在數(shù)值計算、數(shù)據(jù)分析和信號

2019-07-05 06:21:42

引言

想要實現(xiàn)浮點運算功能,如果自己寫Verilog代碼,需要花費較多的時間和精力。好在Simulink HDL Coder工具箱提供了自動代碼生成技術(shù)。下圖展示了HDL Coder如何生成浮點運算

2025-10-22 06:48:48

總結(jié): 1.使用浮點運算的小數(shù)點后面必須加(f),不然就默認成了雙精度浮點類型,計算速度變得很慢。(和編譯器無關(guān),測試使用最新KEIL)。2018 / 12

2021-08-11 08:01:55

在定點DSP系統(tǒng)中可否實現(xiàn)浮點運算?當然可以,因為DSP都可以用C,只要是可以使用c語言的場合都可以實現(xiàn)浮點運算。

2009-04-07 09:06:17

浮點運算作為數(shù)字信號處理中最常見的運算之一,各大EDA軟件都帶有免費的浮點運算IP核。通過對IP核的生成和例化來實現(xiàn)浮點運算,把FPGA設(shè)計者從繁重的代碼編寫中解脫了出來,同時可以對IP核進行功能

2019-10-12 06:19:54

在定點DSP系統(tǒng)中可否實現(xiàn)浮點運算?

2019-09-25 05:55:21

在定點DSP系統(tǒng)中可否實現(xiàn)浮點運算?

2019-09-26 05:55:42

通過上文介紹,我們大致理清了浮點運算中操作數(shù)的獲取,接下來要進行的工作就是面對整數(shù)或浮點寄存器如何做判斷以及如何實現(xiàn)具體的運算操作,待我們繼續(xù)分析后,在后續(xù)的文章中進行相應(yīng)介紹。

2025-10-24 07:10:06

對浮點數(shù)的運算怎么轉(zhuǎn)換成整數(shù)運算

2023-10-12 06:31:49

運算作為數(shù)字信號處理中最常見的運算之一,各大EDA軟件都帶有免費的浮點運算IP核。通過對IP核的生成和例化來實現(xiàn)浮點運算,把FPGA設(shè)計者從繁重的代碼編寫中解脫了出來,同時可以對IP核進行功能剪裁

2019-08-29 06:50:37

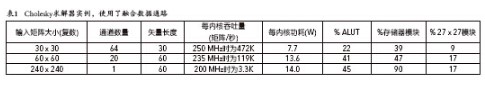

本文介紹了一種基于FPGA的復(fù)數(shù)浮點協(xié)方差矩陣實現(xiàn)方案。

2021-04-29 06:01:31

近來,Altera公司推出業(yè)界首款浮點FPGA,它集成了硬核IEEE754兼容浮點運算功能,提高了DSP性能、設(shè)計人員的效能和邏輯效率。據(jù)悉,硬核浮點DSP模塊集成在

2019-07-03 07:56:05

操作數(shù)。

總結(jié)

通過上文介紹,我們大致理清了浮點運算中操作數(shù)的獲取,接下來要進行的工作就是面對整數(shù)或浮點寄存器如何做判斷以及如何實現(xiàn)具體的運算操作,待我們繼續(xù)分析后,在后續(xù)的文章中進行相應(yīng)介紹。

2025-10-24 13:39:13

編譯選項選擇6700+。定點浮點結(jié)合可以在-mv編譯選項選擇6748。現(xiàn)在我想寫一段程序,這段程序先用浮點運算計算一個公式,算完之后再用定點運算計算這個公式,請問我該怎么實現(xiàn)呢?有什么相關(guān)的指令嗎?

2018-08-02 08:54:38

請問Altera RAM IP核怎么使用?

2022-01-18 06:59:33

我們的藍牙芯片有浮點運算單元嗎

2022-10-09 07:52:55

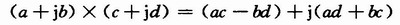

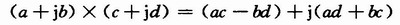

⊕ sb,得到結(jié)果的符號位

階碼相加減

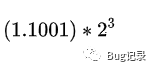

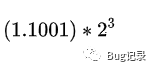

按照定點整數(shù)的加減法運算方法對兩個浮點數(shù)的階碼進行加減運算,因為規(guī)格化數(shù)的價碼e滿足1≤e≤254,而ec有可能超出1~254范圍,所以當1≤ec≤254,相乘結(jié)果

2025-10-24 07:11:26

浮點運算方法:

2008-01-16 09:22:37 29

29

DSP的浮點運算方法

2008-01-16 09:25:05 4

4 定點dsp浮點運算的多媒體視頻教程:

2008-01-24 09:14:21 50

50

介紹了用VHDL 語言在硬件芯片上實現(xiàn)浮點加/ 減法、浮點乘法運算的方法,并以Altera

公司的FLEX10K系列產(chǎn)品為硬件平臺,以Maxplus II 為軟件工具,實現(xiàn)了6 點實序列浮點加/ 減法

2009-07-28 14:06:13 85

85 在陣列信號處理中需要大量的矩陣運算,而其中最基本的就是矩陣相乘運算。本文就矩陣相乘的行劃分并行實現(xiàn)進行了改進,將A矩陣的一行和整個B矩陣傳輸?shù)矫總€工作進程,其中第一個

2010-07-27 16:30:27 9

9 對TMS320C3X中浮點數(shù)除法的實現(xiàn)方法進行了詳細討論,并給出匯編子程序。浮點數(shù)除法首先利用牛頓迭代法求出除數(shù)的倒數(shù),然后再與被除數(shù)相乘,從而得出結(jié)果。該設(shè)計思想已經(jīng)應(yīng)

2010-08-05 16:34:51 17

17 什么叫浮點運算

當我們用不同的電腦計算圓周率時,會發(fā)現(xiàn)一臺電腦的計算較另一臺來講結(jié)果更加精確。或者我們在進行槍戰(zhàn)游戲的時候,當一粒子彈擊

2008-01-16 09:30:01 4359

4359 功能:浮點度數(shù)轉(zhuǎn)換成浮點弧度數(shù)

入口條件:浮點度數(shù)在[R0]中。出口信息:轉(zhuǎn)換成的浮點弧度數(shù)仍在[R0]中。影響資源:PSW、A、B、R

2009-01-19 22:46:38 1144

1144 高速流水線浮點加法器的FPGA實現(xiàn)

0 引言現(xiàn)代信號處理技術(shù)通常都需要進行大量高速浮點運算。由于浮點數(shù)系統(tǒng)操作比較復(fù)雜,需要專用硬件來完成相關(guān)的操

2010-02-04 10:50:23 2778

2778

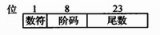

浮點DSP,浮點DSP是什么意思

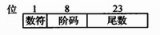

浮點DSP可以完成整數(shù)和實數(shù)運算,它的數(shù)據(jù)格式分為階碼和尾數(shù)(有一位可以設(shè)為符號位)。通常浮點DSP的

2010-03-26 14:57:01 2493

2493 浮點運算與浮點運算器

浮點加減法的運算步驟 設(shè)兩個浮點數(shù) X=Mx※2Ex Y=My※2Ey 實現(xiàn)X±Y要用如下5步完成: ①對階操作:小階

2010-04-15 13:42:32 7293

7293 O 引言

協(xié)方差矩陣的計算是信號處理領(lǐng)域的典型運算,是實現(xiàn)多級嵌套維納濾波器、空間譜估

2010-10-08 17:41:14 3350

3350

在Cortex-M3內(nèi)核上實現(xiàn)浮點型運算,可以達到所要求的精度,運算速度較快,具有較高的實時性。本文提出的浮點型運算的處理方法在基于Cortex-M3內(nèi)核的處理器上有著較高的應(yīng)用價值。希望對從事這方面的人員有所幫助。

2011-03-11 11:04:02 13127

13127

在科學(xué)計算中,需要大量的矩陣運算,而矩陣運算中乘法運算是其他運算的基礎(chǔ),如能提高嵌入式系統(tǒng)中浮點矩陣乘法運算的速度,則可加快其他類型的矩陣運算速度。 目前實現(xiàn)浮點矩

2011-09-07 11:31:53 3268

3268

Altera公司日前演示了使用FPGA的浮點DSP新設(shè)計流程,這是業(yè)界第一款基于模型的浮點設(shè)計工具,支持在FPGA中實現(xiàn)復(fù)數(shù)浮點DSP算法。伯克萊設(shè)計技術(shù)公司 (Berkeley Design Technology, Inc, BDTI) 進行

2011-09-15 08:48:58 1115

1115 Altera公司日前演示了使用FPGA的浮點DSP新設(shè)計流程,這是業(yè)界第一款基于模型的浮點設(shè)計工具,支持在FPGA中實現(xiàn)復(fù)數(shù)浮點DSP算法。

2011-09-15 09:07:10 830

830 矩陣相乘的速度在陣列信號處理中具有重要意義,并行處理是提高系統(tǒng)運算能力最有效的方法。本文根據(jù)矩陣相乘的特點,提凡了矩陣相乘的并行算法。同時經(jīng)分析攜姆出了矩陣相乘的

2011-10-12 16:27:41 74

74 STM32F4的浮點 DSP 運算效率不高

2015-12-07 17:55:14 0

0 作者:Steve Leibson, 賽靈思戰(zhàn)略營銷與業(yè)務(wù)規(guī)劃總監(jiān) Zynq使Intel四核CPU浮點運算性能提高1.7倍 Topic Embedded的產(chǎn)品總監(jiān)Inge Rutten最近

2017-02-09 06:15:08 1645

1645 Float Point Unit,浮點運算單元是專用于浮點運算的協(xié)處理器,在計算領(lǐng)域,例如三角函數(shù)以及時域頻域變換通常會用到浮點運算。

2017-09-16 11:28:47 6

6 14.10 浮點運算 大多數(shù)的ARM處理器硬件上并不支持浮點運算。但ARM上提供了以下幾個選項來實現(xiàn)浮點運算。 浮點累加協(xié)處理器FPA(Floating-Point Accelerator):ARM

2017-10-17 16:48:39 1

1 引 言 DSP結(jié)構(gòu)可以分為定點和浮點型兩種。其中,定點型DSP可以實現(xiàn)整數(shù)、小數(shù)和特定的指數(shù)運算,它具有運算速度快、占用資源少、成本低等特點;靈活地使用定點型DSP進行浮點運算能夠提高運算的效率

2017-11-02 11:26:42 2

2 浮點具有更大的數(shù)據(jù)動態(tài)范圍,從而在很多算法中只需要一種數(shù)據(jù)類型的優(yōu)勢。本文介紹如何使用Vivado HLS實現(xiàn)浮點復(fù)數(shù)矩陣分解。使用HLS可以快速,高效地實現(xiàn)各種矩陣分解算法,極大地提高生產(chǎn)效率, 降低開發(fā)者的算法FPGA實現(xiàn)難度。

2017-11-18 12:00:11 1290

1290

浮點算法不遵循整數(shù)算法規(guī)則,但利用 FPGA 或者基于 FPGA 的嵌入式處理器不難設(shè)計出精確的浮點系統(tǒng)。工程人員一看到浮點運算就會頭疼,因為浮點運算用軟件實現(xiàn)速度慢,用硬件實現(xiàn)則占用資源多。理解

2017-11-22 16:51:08 2072

2072 異常會造成程序錯誤,實現(xiàn)完全沒有異常的浮點計算軟件也很艱難,因此,實現(xiàn)有效的異常處理方法很重要.但現(xiàn)有的異常處理并不針對浮點運算,并且研究重點都集中在整數(shù)溢出錯誤上,而浮點類型運算降低了整數(shù)溢出存在

2018-01-19 15:50:14 1

1 2014年4月23號,北京Altera公司 (Nasdaq: ALTR) 今天宣布在FPGA浮點DSP性能方面實現(xiàn)了變革。Altera是第一家在FPGA中集成硬核IEEE 754兼容浮點運算功能

2018-02-11 13:34:00 7749

7749 在載人航天飛船的終端儀器儀表設(shè)計中,處理算法中的浮點非線性運算常采用庫函數(shù)實現(xiàn),但軟件實現(xiàn)非線性函數(shù)執(zhí)行速度慢,限制了浮點算法的應(yīng)用。為此,針對航天領(lǐng)域處理器不支持非線性函數(shù)運算的情況以及浮點

2018-02-26 14:58:34 0

0 為什么 CPU 的浮點運算能力比 GPU 差,為什么不提高 CPU 的浮點運算能力?

2018-03-16 15:12:02 16274

16274 浮點加法是數(shù)字信號處理中的一種非常頻繁且非常重要的操作,在現(xiàn)代數(shù)字信號處理應(yīng)用中,浮點加法運算幾乎占到全部浮點操作的一半以上。浮點乘法器是高性能DSP(數(shù)字信號處理器)的重要部件,是實時處理的核心

2018-04-10 10:47:21 8

8 浮點運算是計算機運算的重要方式,較之定點運算有著計數(shù)范圍寬有效精度高的特點。在各種工程計算和科學(xué)計算中有著廣泛應(yīng)用。目前浮點運算大多采用DSP芯片實現(xiàn),具有算法簡單,精度高的優(yōu)點。但同時由于浮點運算

2018-04-10 14:25:53 17

17 以往FPGA在進行浮點運算時,為符合IEEE 754標準,每次運算都需要去歸一化和歸一化步驟,導(dǎo)致了極大的性能瓶頸。因為這些歸一化和去歸一化步驟一般通過FPGA中的大規(guī)模桶形移位寄存器實現(xiàn),需要大量

2020-01-14 16:19:55 4101

4101

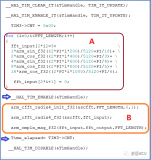

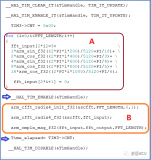

這里通過調(diào)用DSP庫里的FFT相關(guān)函數(shù)實現(xiàn)1024點的FFT運算,樣點數(shù)據(jù)及運算結(jié)果均為浮點數(shù)。 上圖中A區(qū)代碼是做樣點數(shù)據(jù)準備,B區(qū)代碼完成FFT運算。我們來一起看看基本的配置以及不啟用硬件浮點單元和啟用硬件浮點單元執(zhí)行B區(qū)代碼的時間上的差別。 程序里要調(diào)用

2021-01-02 18:09:00 9859

9859

該問題由某客戶提出,發(fā)生在 STM32F407IGT6 器件上。據(jù)其工程師講述:由于在其產(chǎn)品中,需要使用STM32進行大量的浮點數(shù)以及浮點DSP運算,所以針對STM32的浮點數(shù)運算能力及 DSP

2021-04-28 15:17:02 10

10 編者按:在計算領(lǐng)域,例如三角函數(shù)以及時域頻域變換通常會用到浮點運算。當CPU執(zhí)行一個需要浮點數(shù)運算的程序時,有三種方式可以執(zhí)行:軟件仿真器(浮點運算函數(shù)庫)、附加浮點運算器和集成浮點運算單元。在控制

2021-12-04 13:36:05 19

19 使用插值算法實現(xiàn)圖像縮放是數(shù)字圖像處理算法中經(jīng)常遇到的問題。我們經(jīng)常會將某種尺寸的圖像轉(zhuǎn)換為其他尺寸的圖像,如放大或者縮小圖像。由于在縮放的過程中會遇到浮點數(shù),如何在FPGA中正確的處理浮點數(shù)運算是在FPGA中實現(xiàn)圖像縮放的關(guān)鍵。

2022-03-18 11:03:41 5929

5929 我們使用的處理器一般情況下,要么直接支持硬件的 浮點運算 ,比如某些帶有FPU的器件,要么就只支持定點運算,此時對 浮點 數(shù)的處理需要通過編譯器來完成。在支持硬件浮點處理的器件上,對 浮點運算

2022-12-09 12:25:09 3815

3815 定點數(shù)硬件實現(xiàn)簡單,但表示的范圍有限,且部分的小數(shù)運算IP核只支持浮點數(shù)運算,因此這里還需要提到浮點數(shù)的相關(guān)內(nèi)容。

2023-06-16 15:41:53 2083

2083

,浮點加法器是現(xiàn)代信號處理系統(tǒng)中最重要的部件之一。FPGA是當前數(shù)字電路研究開發(fā)的一種重要實現(xiàn)形式,它與全定制ASIC電路相比,具有開發(fā)周期短、成本低等優(yōu)點。 但多數(shù)FPGA不支持浮點運算,這使FPGA在數(shù)值計算、數(shù)據(jù)分析和信號處理等方

2023-09-22 10:40:03 2116

2116

引言 LMS(最小均方)算法因其收斂速度快及算法實現(xiàn)簡單等特點在自適應(yīng)濾波器、自適應(yīng)天線陣技術(shù)等領(lǐng)域得到了十分廣泛的應(yīng)用。為了發(fā)揮算法的最佳性能,必須采用具有大動態(tài)范圍及運算精度的浮點運算,而浮點

2023-12-21 16:40:01 1590

1590 支持硬件浮點運算單元(FPU),可以提供快速和高效的浮點運算性能。本文將詳細介紹 STM32F407 的浮點運算速度。 浮點運算是很多應(yīng)用中常用的一種運算類型,特別是對于需要進行較復(fù)雜計算的任務(wù),如圖像處理、信號處理和物理模擬等。傳統(tǒng)的處理器對于浮點運算的支持有限,需要通過軟件庫實現(xiàn)

2024-01-04 10:58:34 5181

5181 浮點運算器(英文:floating point unit,簡稱FPU)是計算機系統(tǒng)的一部分,它是專門用來進行浮點數(shù)運算的(CPU中也叫ALU)。

2024-04-26 11:27:35 6617

6617

由于定點的四則運算比較簡單,如加減法只要注意符號擴展,小數(shù)點對齊等問題即可。在本文中,運用在前一節(jié)中描述的自定義浮點格式FPGA中數(shù)的表示方法(下),完成浮點四則運算的實現(xiàn)過程 1.自定義浮點格式加

2024-11-16 11:19:23 2139

2139

由于定點的四則運算比較簡單,如加減法只要注意符號擴展,小數(shù)點對齊等問題即可。在本文中,運用在前一節(jié)中描述的自定義浮點格式FPGA中數(shù)的表示方法(下),完成浮點四則運算的實現(xiàn)過程 1.自定義浮點格式加

2024-11-16 12:51:57 1323

1323

電子發(fā)燒友App

電子發(fā)燒友App

評論