Block實(shí)現(xiàn)32位單精度浮點(diǎn)的卷積運(yùn)算,而針對(duì)定點(diǎn)及低精度的浮點(diǎn)運(yùn)算,則需要對(duì)硬浮點(diǎn)DSP Block進(jìn)行相應(yīng)的替換即可。

2018-07-23 09:09:45 8401

8401

大部分運(yùn)算可以通過(guò)擴(kuò)位和近似的方式轉(zhuǎn)換為定點(diǎn)運(yùn)算。但有些算法在設(shè)計(jì)在設(shè)計(jì)的過(guò)程中就涉及大量的浮點(diǎn)運(yùn)算,在轉(zhuǎn)換為定點(diǎn)運(yùn)算時(shí)比較麻煩,會(huì)帶來(lái)龐大的工作量。

2022-09-08 15:41:56 3509

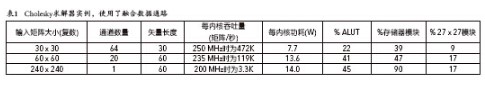

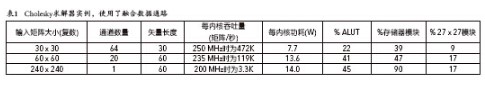

3509 語(yǔ)言編寫的浮點(diǎn)矩陣相乘處理單元[1],其關(guān)鍵技術(shù)是乘累加單元的設(shè)計(jì),這樣設(shè)計(jì)的硬件,其性能依賴于設(shè)計(jì)者的編程水平。此外,F(xiàn)PGA廠商也推出了一定規(guī)模的浮點(diǎn)矩陣運(yùn)算IP核[2],雖然此IP核應(yīng)用了本廠家的器件,并經(jīng)過(guò)專業(yè)調(diào)試和硬件實(shí)測(cè),性能穩(wěn)定且優(yōu)于手寫代碼,但仍可對(duì)其進(jìn)行改進(jìn),以進(jìn)一步提高運(yùn)算速度。

2019-08-22 06:41:38

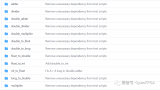

Altera_IP核,僅供參考

2016-08-24 16:57:15

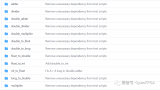

浮點(diǎn)運(yùn)算單元的設(shè)計(jì)和優(yōu)化可以從以下幾個(gè)方面入手:

1.浮點(diǎn)寄存器設(shè)計(jì):為了實(shí)現(xiàn)浮點(diǎn)運(yùn)算指令子集(RV32F或者RV32D),需要添加一組專用的浮點(diǎn)寄存器組,總共需要32個(gè)通用浮點(diǎn)寄存器。其中

2025-10-22 07:04:49

詳解浮點(diǎn)運(yùn)算的定點(diǎn)編程

2021-04-02 06:59:52

嗨,我在我的應(yīng)用程序中使用PIC32 MX250F256H控制器。我面臨著浮點(diǎn)運(yùn)算的一些問(wèn)題。浮點(diǎn)F=0in主體(){f=(浮點(diǎn))(47.171143947.0);}我應(yīng)該得到f=0.1711439

2018-10-08 15:55:49

fpga),現(xiàn)在需要完成一個(gè)cpu/fpga協(xié)同工作的任務(wù),使用pcie總線通信。具體任務(wù)很簡(jiǎn)單:cpu通過(guò)pcie傳兩個(gè)32位浮點(diǎn)數(shù)給fpga,fpga相乘然后把結(jié)果返回。乘法模塊使用quartus提供

2014-12-21 21:32:14

摘要:

本文主要描述浮點(diǎn)數(shù)是如何實(shí)現(xiàn)開(kāi)平方運(yùn)算的。

簡(jiǎn)介

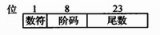

事實(shí)上,浮點(diǎn)數(shù)的開(kāi)平方運(yùn)算結(jié)構(gòu)與定點(diǎn)數(shù)甚至整數(shù)的開(kāi)平方運(yùn)算結(jié)構(gòu)是十分相似的,我們可以在對(duì)定點(diǎn)數(shù)求平方根運(yùn)算結(jié)構(gòu)的基礎(chǔ)上,針對(duì)階碼域進(jìn)行

2025-10-24 08:42:22

使用c6678進(jìn)行浮點(diǎn)除法運(yùn)算的時(shí)間測(cè)試的時(shí)候(使用clock),發(fā)現(xiàn)(使用c6678evm板)運(yùn)行時(shí)間很長(zhǎng),運(yùn)算時(shí)間達(dá)到七百多個(gè)時(shí)鐘周期。請(qǐng)問(wèn)是什么原因?c6678本身的浮點(diǎn)除法能達(dá)到什么樣的運(yùn)算速度呢?

2018-06-21 13:49:31

在《ARM微控制器基礎(chǔ)與實(shí)戰(zhàn)》的 2.6.3 節(jié)有說(shuō)到"浮點(diǎn)數(shù)寄存器(F0-F7...)",2104是否具有這些寄存器如果 EasyArm 不支持浮點(diǎn)運(yùn)算,而我的程序需要用到浮點(diǎn)運(yùn)算,請(qǐng)問(wèn)可以實(shí)現(xiàn)嗎

2022-11-07 15:24:11

求用verilog實(shí)現(xiàn)浮點(diǎn)數(shù)運(yùn)算的資料,謝謝

2016-12-17 21:15:52

FPGA 如何進(jìn)行浮點(diǎn)運(yùn)算

2015-09-26 09:31:37

最近出現(xiàn)的 FPGA設(shè)計(jì)工具和 IP有效減少了計(jì)算占用的資源,大大簡(jiǎn)化了浮點(diǎn)數(shù)據(jù)通路的實(shí)現(xiàn)。而且,與數(shù)字信號(hào)處理器不同, FPGA能夠支持浮點(diǎn)和定點(diǎn)混合工作的 DSP數(shù)據(jù)通路,實(shí)現(xiàn)的性能超過(guò)

2019-08-13 06:42:48

TI的各位工程師及各位飄過(guò)的仁兄好:

?????? 話說(shuō)我用138中的6748內(nèi)核做浮點(diǎn)運(yùn)算,測(cè)得一次32位的浮點(diǎn)運(yùn)算竟用了100多個(gè)clock,兩百多微妙啊……甚是吃驚,坊間傳聞6748一個(gè)

2018-06-21 06:36:58

Vivado浮點(diǎn)數(shù)IP核的握手信號(hào)

我們的設(shè)計(jì)方案中,F(xiàn)PU計(jì)算單元將收到的三條數(shù)據(jù)和使能信號(hào)同步發(fā)給20多個(gè)模塊,同時(shí)只有一個(gè)模塊被時(shí)鐘使能,進(jìn)行計(jì)算,但結(jié)果都會(huì)保留,發(fā)給數(shù)選。計(jì)算單元還需接受

2025-10-24 07:01:36

HI論壇,在我的方式三相交流感應(yīng)電機(jī)控制,我遇到的文件“GS00 4”。它提到了一點(diǎn)“分?jǐn)?shù)乘法”,這是在匯編指令“MPY”中完成的。dsPIC的核心不支持浮點(diǎn)運(yùn)算,但DSC部分支持浮點(diǎn)運(yùn)算,對(duì)嗎?為什么XC16不定期使用這個(gè)芯片中可用的浮點(diǎn)命令?對(duì)我來(lái)說(shuō),壓倒性的參數(shù)對(duì)我來(lái)說(shuō)并不重要。

2020-04-02 10:06:31

labview怎樣實(shí)現(xiàn)矩陣相乘A是nxm矩陣,B是mxp矩陣,如何實(shí)現(xiàn)C=AB;

2012-12-12 21:02:32

RISC-V浮點(diǎn)運(yùn)算單元(floating-point unit,簡(jiǎn)稱FPU)是一種專門用于執(zhí)行浮點(diǎn)運(yùn)算的硬件加速器,其作用是提高浮點(diǎn)運(yùn)算速度,在科學(xué)計(jì)算、圖像處理和機(jī)器學(xué)習(xí)等應(yīng)用領(lǐng)域有著廣泛

2025-10-21 14:46:51

stm32f103浮點(diǎn)運(yùn)算(支持單精度和雙精度)本章主要講解實(shí)數(shù)浮點(diǎn)FTT,支持單精度和雙精度。目錄31.1 初學(xué)者重要提示31.2 實(shí)數(shù)浮點(diǎn)FFT說(shuō)明31.3 單精度函數(shù)

2021-08-10 06:22:04

Verilog可以通過(guò)使用IEEE標(biāo)準(zhǔn)的浮點(diǎn)數(shù)表示來(lái)實(shí)現(xiàn)浮點(diǎn)運(yùn)算。下面是一個(gè)基本的Verilog模塊示例,展示了如何進(jìn)行加法、乘法和除法等常見(jiàn)的浮點(diǎn)運(yùn)算操作:

module

2024-03-25 21:49:34

兩單精度浮點(diǎn)數(shù)相乘是先轉(zhuǎn)換成二進(jìn)制再相乘還是直接相乘,求教思路或程序

2016-10-23 23:36:36

處理系統(tǒng)中最重要的部件之一。FPGA是當(dāng)前數(shù)字電路研究開(kāi)發(fā)的一種重要實(shí)現(xiàn)形式,它與全定制ASIC電路相比,具有開(kāi)發(fā)周期短、成本低等優(yōu)點(diǎn)。但多數(shù)FPGA不支持浮點(diǎn)運(yùn)算,這使FPGA在數(shù)值計(jì)算、數(shù)據(jù)分析和信號(hào)

2019-07-05 06:21:42

引言

想要實(shí)現(xiàn)浮點(diǎn)運(yùn)算功能,如果自己寫Verilog代碼,需要花費(fèi)較多的時(shí)間和精力。好在Simulink HDL Coder工具箱提供了自動(dòng)代碼生成技術(shù)。下圖展示了HDL Coder如何生成浮點(diǎn)運(yùn)算

2025-10-22 06:48:48

總結(jié): 1.使用浮點(diǎn)運(yùn)算的小數(shù)點(diǎn)后面必須加(f),不然就默認(rèn)成了雙精度浮點(diǎn)類型,計(jì)算速度變得很慢。(和編譯器無(wú)關(guān),測(cè)試使用最新KEIL)。2018 / 12

2021-08-11 08:01:55

在定點(diǎn)DSP系統(tǒng)中可否實(shí)現(xiàn)浮點(diǎn)運(yùn)算?當(dāng)然可以,因?yàn)镈SP都可以用C,只要是可以使用c語(yǔ)言的場(chǎng)合都可以實(shí)現(xiàn)浮點(diǎn)運(yùn)算。

2009-04-07 09:06:17

浮點(diǎn)運(yùn)算作為數(shù)字信號(hào)處理中最常見(jiàn)的運(yùn)算之一,各大EDA軟件都帶有免費(fèi)的浮點(diǎn)運(yùn)算IP核。通過(guò)對(duì)IP核的生成和例化來(lái)實(shí)現(xiàn)浮點(diǎn)運(yùn)算,把FPGA設(shè)計(jì)者從繁重的代碼編寫中解脫了出來(lái),同時(shí)可以對(duì)IP核進(jìn)行功能

2019-10-12 06:19:54

在定點(diǎn)DSP系統(tǒng)中可否實(shí)現(xiàn)浮點(diǎn)運(yùn)算?

2019-09-25 05:55:21

在定點(diǎn)DSP系統(tǒng)中可否實(shí)現(xiàn)浮點(diǎn)運(yùn)算?

2019-09-26 05:55:42

通過(guò)上文介紹,我們大致理清了浮點(diǎn)運(yùn)算中操作數(shù)的獲取,接下來(lái)要進(jìn)行的工作就是面對(duì)整數(shù)或浮點(diǎn)寄存器如何做判斷以及如何實(shí)現(xiàn)具體的運(yùn)算操作,待我們繼續(xù)分析后,在后續(xù)的文章中進(jìn)行相應(yīng)介紹。

2025-10-24 07:10:06

對(duì)浮點(diǎn)數(shù)的運(yùn)算怎么轉(zhuǎn)換成整數(shù)運(yùn)算

2023-10-12 06:31:49

運(yùn)算作為數(shù)字信號(hào)處理中最常見(jiàn)的運(yùn)算之一,各大EDA軟件都帶有免費(fèi)的浮點(diǎn)運(yùn)算IP核。通過(guò)對(duì)IP核的生成和例化來(lái)實(shí)現(xiàn)浮點(diǎn)運(yùn)算,把FPGA設(shè)計(jì)者從繁重的代碼編寫中解脫了出來(lái),同時(shí)可以對(duì)IP核進(jìn)行功能剪裁

2019-08-29 06:50:37

本文介紹了一種基于FPGA的復(fù)數(shù)浮點(diǎn)協(xié)方差矩陣實(shí)現(xiàn)方案。

2021-04-29 06:01:31

近來(lái),Altera公司推出業(yè)界首款浮點(diǎn)FPGA,它集成了硬核IEEE754兼容浮點(diǎn)運(yùn)算功能,提高了DSP性能、設(shè)計(jì)人員的效能和邏輯效率。據(jù)悉,硬核浮點(diǎn)DSP模塊集成在

2019-07-03 07:56:05

操作數(shù)。

總結(jié)

通過(guò)上文介紹,我們大致理清了浮點(diǎn)運(yùn)算中操作數(shù)的獲取,接下來(lái)要進(jìn)行的工作就是面對(duì)整數(shù)或浮點(diǎn)寄存器如何做判斷以及如何實(shí)現(xiàn)具體的運(yùn)算操作,待我們繼續(xù)分析后,在后續(xù)的文章中進(jìn)行相應(yīng)介紹。

2025-10-24 13:39:13

編譯選項(xiàng)選擇6700+。定點(diǎn)浮點(diǎn)結(jié)合可以在-mv編譯選項(xiàng)選擇6748。現(xiàn)在我想寫一段程序,這段程序先用浮點(diǎn)運(yùn)算計(jì)算一個(gè)公式,算完之后再用定點(diǎn)運(yùn)算計(jì)算這個(gè)公式,請(qǐng)問(wèn)我該怎么實(shí)現(xiàn)呢?有什么相關(guān)的指令嗎?

2018-08-02 08:54:38

請(qǐng)問(wèn)Altera RAM IP核怎么使用?

2022-01-18 06:59:33

我們的藍(lán)牙芯片有浮點(diǎn)運(yùn)算單元嗎

2022-10-09 07:52:55

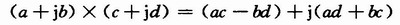

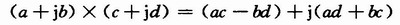

⊕ sb,得到結(jié)果的符號(hào)位

階碼相加減

按照定點(diǎn)整數(shù)的加減法運(yùn)算方法對(duì)兩個(gè)浮點(diǎn)數(shù)的階碼進(jìn)行加減運(yùn)算,因?yàn)橐?guī)格化數(shù)的價(jià)碼e滿足1≤e≤254,而ec有可能超出1~254范圍,所以當(dāng)1≤ec≤254,相乘結(jié)果

2025-10-24 07:11:26

浮點(diǎn)運(yùn)算方法:

2008-01-16 09:22:37 29

29

DSP的浮點(diǎn)運(yùn)算方法

2008-01-16 09:25:05 4

4 定點(diǎn)dsp浮點(diǎn)運(yùn)算的多媒體視頻教程:

2008-01-24 09:14:21 50

50

介紹了用VHDL 語(yǔ)言在硬件芯片上實(shí)現(xiàn)浮點(diǎn)加/ 減法、浮點(diǎn)乘法運(yùn)算的方法,并以Altera

公司的FLEX10K系列產(chǎn)品為硬件平臺(tái),以Maxplus II 為軟件工具,實(shí)現(xiàn)了6 點(diǎn)實(shí)序列浮點(diǎn)加/ 減法

2009-07-28 14:06:13 85

85 在陣列信號(hào)處理中需要大量的矩陣運(yùn)算,而其中最基本的就是矩陣相乘運(yùn)算。本文就矩陣相乘的行劃分并行實(shí)現(xiàn)進(jìn)行了改進(jìn),將A矩陣的一行和整個(gè)B矩陣傳輸?shù)矫總€(gè)工作進(jìn)程,其中第一個(gè)

2010-07-27 16:30:27 9

9 對(duì)TMS320C3X中浮點(diǎn)數(shù)除法的實(shí)現(xiàn)方法進(jìn)行了詳細(xì)討論,并給出匯編子程序。浮點(diǎn)數(shù)除法首先利用牛頓迭代法求出除數(shù)的倒數(shù),然后再與被除數(shù)相乘,從而得出結(jié)果。該設(shè)計(jì)思想已經(jīng)應(yīng)

2010-08-05 16:34:51 17

17 什么叫浮點(diǎn)運(yùn)算

當(dāng)我們用不同的電腦計(jì)算圓周率時(shí),會(huì)發(fā)現(xiàn)一臺(tái)電腦的計(jì)算較另一臺(tái)來(lái)講結(jié)果更加精確。或者我們?cè)谶M(jìn)行槍戰(zhàn)游戲的時(shí)候,當(dāng)一粒子彈擊

2008-01-16 09:30:01 4359

4359 功能:浮點(diǎn)度數(shù)轉(zhuǎn)換成浮點(diǎn)弧度數(shù)

入口條件:浮點(diǎn)度數(shù)在[R0]中。出口信息:轉(zhuǎn)換成的浮點(diǎn)弧度數(shù)仍在[R0]中。影響資源:PSW、A、B、R

2009-01-19 22:46:38 1144

1144 高速流水線浮點(diǎn)加法器的FPGA實(shí)現(xiàn)

0 引言現(xiàn)代信號(hào)處理技術(shù)通常都需要進(jìn)行大量高速浮點(diǎn)運(yùn)算。由于浮點(diǎn)數(shù)系統(tǒng)操作比較復(fù)雜,需要專用硬件來(lái)完成相關(guān)的操

2010-02-04 10:50:23 2778

2778

浮點(diǎn)DSP,浮點(diǎn)DSP是什么意思

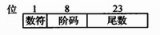

浮點(diǎn)DSP可以完成整數(shù)和實(shí)數(shù)運(yùn)算,它的數(shù)據(jù)格式分為階碼和尾數(shù)(有一位可以設(shè)為符號(hào)位)。通常浮點(diǎn)DSP的

2010-03-26 14:57:01 2493

2493 浮點(diǎn)運(yùn)算與浮點(diǎn)運(yùn)算器

浮點(diǎn)加減法的運(yùn)算步驟 設(shè)兩個(gè)浮點(diǎn)數(shù) X=Mx※2Ex Y=My※2Ey 實(shí)現(xiàn)X±Y要用如下5步完成: ①對(duì)階操作:小階

2010-04-15 13:42:32 7293

7293 O 引言

協(xié)方差矩陣的計(jì)算是信號(hào)處理領(lǐng)域的典型運(yùn)算,是實(shí)現(xiàn)多級(jí)嵌套維納濾波器、空間譜估

2010-10-08 17:41:14 3350

3350

在Cortex-M3內(nèi)核上實(shí)現(xiàn)浮點(diǎn)型運(yùn)算,可以達(dá)到所要求的精度,運(yùn)算速度較快,具有較高的實(shí)時(shí)性。本文提出的浮點(diǎn)型運(yùn)算的處理方法在基于Cortex-M3內(nèi)核的處理器上有著較高的應(yīng)用價(jià)值。希望對(duì)從事這方面的人員有所幫助。

2011-03-11 11:04:02 13127

13127

在科學(xué)計(jì)算中,需要大量的矩陣運(yùn)算,而矩陣運(yùn)算中乘法運(yùn)算是其他運(yùn)算的基礎(chǔ),如能提高嵌入式系統(tǒng)中浮點(diǎn)矩陣乘法運(yùn)算的速度,則可加快其他類型的矩陣運(yùn)算速度。 目前實(shí)現(xiàn)浮點(diǎn)矩

2011-09-07 11:31:53 3268

3268

Altera公司日前演示了使用FPGA的浮點(diǎn)DSP新設(shè)計(jì)流程,這是業(yè)界第一款基于模型的浮點(diǎn)設(shè)計(jì)工具,支持在FPGA中實(shí)現(xiàn)復(fù)數(shù)浮點(diǎn)DSP算法。伯克萊設(shè)計(jì)技術(shù)公司 (Berkeley Design Technology, Inc, BDTI) 進(jìn)行

2011-09-15 08:48:58 1115

1115 Altera公司日前演示了使用FPGA的浮點(diǎn)DSP新設(shè)計(jì)流程,這是業(yè)界第一款基于模型的浮點(diǎn)設(shè)計(jì)工具,支持在FPGA中實(shí)現(xiàn)復(fù)數(shù)浮點(diǎn)DSP算法。

2011-09-15 09:07:10 830

830 矩陣相乘的速度在陣列信號(hào)處理中具有重要意義,并行處理是提高系統(tǒng)運(yùn)算能力最有效的方法。本文根據(jù)矩陣相乘的特點(diǎn),提凡了矩陣相乘的并行算法。同時(shí)經(jīng)分析攜姆出了矩陣相乘的

2011-10-12 16:27:41 74

74 STM32F4的浮點(diǎn) DSP 運(yùn)算效率不高

2015-12-07 17:55:14 0

0 作者:Steve Leibson, 賽靈思戰(zhàn)略營(yíng)銷與業(yè)務(wù)規(guī)劃總監(jiān) Zynq使Intel四核CPU浮點(diǎn)運(yùn)算性能提高1.7倍 Topic Embedded的產(chǎn)品總監(jiān)Inge Rutten最近

2017-02-09 06:15:08 1645

1645 Float Point Unit,浮點(diǎn)運(yùn)算單元是專用于浮點(diǎn)運(yùn)算的協(xié)處理器,在計(jì)算領(lǐng)域,例如三角函數(shù)以及時(shí)域頻域變換通常會(huì)用到浮點(diǎn)運(yùn)算。

2017-09-16 11:28:47 6

6 14.10 浮點(diǎn)運(yùn)算 大多數(shù)的ARM處理器硬件上并不支持浮點(diǎn)運(yùn)算。但ARM上提供了以下幾個(gè)選項(xiàng)來(lái)實(shí)現(xiàn)浮點(diǎn)運(yùn)算。 浮點(diǎn)累加協(xié)處理器FPA(Floating-Point Accelerator):ARM

2017-10-17 16:48:39 1

1 引 言 DSP結(jié)構(gòu)可以分為定點(diǎn)和浮點(diǎn)型兩種。其中,定點(diǎn)型DSP可以實(shí)現(xiàn)整數(shù)、小數(shù)和特定的指數(shù)運(yùn)算,它具有運(yùn)算速度快、占用資源少、成本低等特點(diǎn);靈活地使用定點(diǎn)型DSP進(jìn)行浮點(diǎn)運(yùn)算能夠提高運(yùn)算的效率

2017-11-02 11:26:42 2

2 浮點(diǎn)具有更大的數(shù)據(jù)動(dòng)態(tài)范圍,從而在很多算法中只需要一種數(shù)據(jù)類型的優(yōu)勢(shì)。本文介紹如何使用Vivado HLS實(shí)現(xiàn)浮點(diǎn)復(fù)數(shù)矩陣分解。使用HLS可以快速,高效地實(shí)現(xiàn)各種矩陣分解算法,極大地提高生產(chǎn)效率, 降低開(kāi)發(fā)者的算法FPGA實(shí)現(xiàn)難度。

2017-11-18 12:00:11 1290

1290

浮點(diǎn)算法不遵循整數(shù)算法規(guī)則,但利用 FPGA 或者基于 FPGA 的嵌入式處理器不難設(shè)計(jì)出精確的浮點(diǎn)系統(tǒng)。工程人員一看到浮點(diǎn)運(yùn)算就會(huì)頭疼,因?yàn)?b class="flag-6" style="color: red">浮點(diǎn)運(yùn)算用軟件實(shí)現(xiàn)速度慢,用硬件實(shí)現(xiàn)則占用資源多。理解

2017-11-22 16:51:08 2072

2072 異常會(huì)造成程序錯(cuò)誤,實(shí)現(xiàn)完全沒(méi)有異常的浮點(diǎn)計(jì)算軟件也很艱難,因此,實(shí)現(xiàn)有效的異常處理方法很重要.但現(xiàn)有的異常處理并不針對(duì)浮點(diǎn)運(yùn)算,并且研究重點(diǎn)都集中在整數(shù)溢出錯(cuò)誤上,而浮點(diǎn)類型運(yùn)算降低了整數(shù)溢出存在

2018-01-19 15:50:14 1

1 2014年4月23號(hào),北京Altera公司 (Nasdaq: ALTR) 今天宣布在FPGA浮點(diǎn)DSP性能方面實(shí)現(xiàn)了變革。Altera是第一家在FPGA中集成硬核IEEE 754兼容浮點(diǎn)運(yùn)算功能

2018-02-11 13:34:00 7749

7749 在載人航天飛船的終端儀器儀表設(shè)計(jì)中,處理算法中的浮點(diǎn)非線性運(yùn)算常采用庫(kù)函數(shù)實(shí)現(xiàn),但軟件實(shí)現(xiàn)非線性函數(shù)執(zhí)行速度慢,限制了浮點(diǎn)算法的應(yīng)用。為此,針對(duì)航天領(lǐng)域處理器不支持非線性函數(shù)運(yùn)算的情況以及浮點(diǎn)

2018-02-26 14:58:34 0

0 為什么 CPU 的浮點(diǎn)運(yùn)算能力比 GPU 差,為什么不提高 CPU 的浮點(diǎn)運(yùn)算能力?

2018-03-16 15:12:02 16274

16274 浮點(diǎn)加法是數(shù)字信號(hào)處理中的一種非常頻繁且非常重要的操作,在現(xiàn)代數(shù)字信號(hào)處理應(yīng)用中,浮點(diǎn)加法運(yùn)算幾乎占到全部浮點(diǎn)操作的一半以上。浮點(diǎn)乘法器是高性能DSP(數(shù)字信號(hào)處理器)的重要部件,是實(shí)時(shí)處理的核心

2018-04-10 10:47:21 8

8 浮點(diǎn)運(yùn)算是計(jì)算機(jī)運(yùn)算的重要方式,較之定點(diǎn)運(yùn)算有著計(jì)數(shù)范圍寬有效精度高的特點(diǎn)。在各種工程計(jì)算和科學(xué)計(jì)算中有著廣泛應(yīng)用。目前浮點(diǎn)運(yùn)算大多采用DSP芯片實(shí)現(xiàn),具有算法簡(jiǎn)單,精度高的優(yōu)點(diǎn)。但同時(shí)由于浮點(diǎn)運(yùn)算

2018-04-10 14:25:53 17

17 以往FPGA在進(jìn)行浮點(diǎn)運(yùn)算時(shí),為符合IEEE 754標(biāo)準(zhǔn),每次運(yùn)算都需要去歸一化和歸一化步驟,導(dǎo)致了極大的性能瓶頸。因?yàn)檫@些歸一化和去歸一化步驟一般通過(guò)FPGA中的大規(guī)模桶形移位寄存器實(shí)現(xiàn),需要大量

2020-01-14 16:19:55 4101

4101

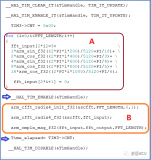

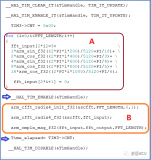

這里通過(guò)調(diào)用DSP庫(kù)里的FFT相關(guān)函數(shù)實(shí)現(xiàn)1024點(diǎn)的FFT運(yùn)算,樣點(diǎn)數(shù)據(jù)及運(yùn)算結(jié)果均為浮點(diǎn)數(shù)。 上圖中A區(qū)代碼是做樣點(diǎn)數(shù)據(jù)準(zhǔn)備,B區(qū)代碼完成FFT運(yùn)算。我們來(lái)一起看看基本的配置以及不啟用硬件浮點(diǎn)單元和啟用硬件浮點(diǎn)單元執(zhí)行B區(qū)代碼的時(shí)間上的差別。 程序里要調(diào)用

2021-01-02 18:09:00 9859

9859

該問(wèn)題由某客戶提出,發(fā)生在 STM32F407IGT6 器件上。據(jù)其工程師講述:由于在其產(chǎn)品中,需要使用STM32進(jìn)行大量的浮點(diǎn)數(shù)以及浮點(diǎn)DSP運(yùn)算,所以針對(duì)STM32的浮點(diǎn)數(shù)運(yùn)算能力及 DSP

2021-04-28 15:17:02 10

10 編者按:在計(jì)算領(lǐng)域,例如三角函數(shù)以及時(shí)域頻域變換通常會(huì)用到浮點(diǎn)運(yùn)算。當(dāng)CPU執(zhí)行一個(gè)需要浮點(diǎn)數(shù)運(yùn)算的程序時(shí),有三種方式可以執(zhí)行:軟件仿真器(浮點(diǎn)運(yùn)算函數(shù)庫(kù))、附加浮點(diǎn)運(yùn)算器和集成浮點(diǎn)運(yùn)算單元。在控制

2021-12-04 13:36:05 19

19 使用插值算法實(shí)現(xiàn)圖像縮放是數(shù)字圖像處理算法中經(jīng)常遇到的問(wèn)題。我們經(jīng)常會(huì)將某種尺寸的圖像轉(zhuǎn)換為其他尺寸的圖像,如放大或者縮小圖像。由于在縮放的過(guò)程中會(huì)遇到浮點(diǎn)數(shù),如何在FPGA中正確的處理浮點(diǎn)數(shù)運(yùn)算是在FPGA中實(shí)現(xiàn)圖像縮放的關(guān)鍵。

2022-03-18 11:03:41 5929

5929 我們使用的處理器一般情況下,要么直接支持硬件的 浮點(diǎn)運(yùn)算 ,比如某些帶有FPU的器件,要么就只支持定點(diǎn)運(yùn)算,此時(shí)對(duì) 浮點(diǎn) 數(shù)的處理需要通過(guò)編譯器來(lái)完成。在支持硬件浮點(diǎn)處理的器件上,對(duì) 浮點(diǎn)運(yùn)算

2022-12-09 12:25:09 3815

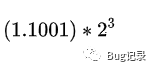

3815 定點(diǎn)數(shù)硬件實(shí)現(xiàn)簡(jiǎn)單,但表示的范圍有限,且部分的小數(shù)運(yùn)算IP核只支持浮點(diǎn)數(shù)運(yùn)算,因此這里還需要提到浮點(diǎn)數(shù)的相關(guān)內(nèi)容。

2023-06-16 15:41:53 2083

2083

,浮點(diǎn)加法器是現(xiàn)代信號(hào)處理系統(tǒng)中最重要的部件之一。FPGA是當(dāng)前數(shù)字電路研究開(kāi)發(fā)的一種重要實(shí)現(xiàn)形式,它與全定制ASIC電路相比,具有開(kāi)發(fā)周期短、成本低等優(yōu)點(diǎn)。 但多數(shù)FPGA不支持浮點(diǎn)運(yùn)算,這使FPGA在數(shù)值計(jì)算、數(shù)據(jù)分析和信號(hào)處理等方

2023-09-22 10:40:03 2116

2116

引言 LMS(最小均方)算法因其收斂速度快及算法實(shí)現(xiàn)簡(jiǎn)單等特點(diǎn)在自適應(yīng)濾波器、自適應(yīng)天線陣技術(shù)等領(lǐng)域得到了十分廣泛的應(yīng)用。為了發(fā)揮算法的最佳性能,必須采用具有大動(dòng)態(tài)范圍及運(yùn)算精度的浮點(diǎn)運(yùn)算,而浮點(diǎn)

2023-12-21 16:40:01 1590

1590 支持硬件浮點(diǎn)運(yùn)算單元(FPU),可以提供快速和高效的浮點(diǎn)運(yùn)算性能。本文將詳細(xì)介紹 STM32F407 的浮點(diǎn)運(yùn)算速度。 浮點(diǎn)運(yùn)算是很多應(yīng)用中常用的一種運(yùn)算類型,特別是對(duì)于需要進(jìn)行較復(fù)雜計(jì)算的任務(wù),如圖像處理、信號(hào)處理和物理模擬等。傳統(tǒng)的處理器對(duì)于浮點(diǎn)運(yùn)算的支持有限,需要通過(guò)軟件庫(kù)實(shí)現(xiàn)

2024-01-04 10:58:34 5181

5181 浮點(diǎn)運(yùn)算器(英文:floating point unit,簡(jiǎn)稱FPU)是計(jì)算機(jī)系統(tǒng)的一部分,它是專門用來(lái)進(jìn)行浮點(diǎn)數(shù)運(yùn)算的(CPU中也叫ALU)。

2024-04-26 11:27:35 6617

6617

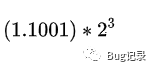

由于定點(diǎn)的四則運(yùn)算比較簡(jiǎn)單,如加減法只要注意符號(hào)擴(kuò)展,小數(shù)點(diǎn)對(duì)齊等問(wèn)題即可。在本文中,運(yùn)用在前一節(jié)中描述的自定義浮點(diǎn)格式FPGA中數(shù)的表示方法(下),完成浮點(diǎn)四則運(yùn)算的實(shí)現(xiàn)過(guò)程 1.自定義浮點(diǎn)格式加

2024-11-16 11:19:23 2139

2139

由于定點(diǎn)的四則運(yùn)算比較簡(jiǎn)單,如加減法只要注意符號(hào)擴(kuò)展,小數(shù)點(diǎn)對(duì)齊等問(wèn)題即可。在本文中,運(yùn)用在前一節(jié)中描述的自定義浮點(diǎn)格式FPGA中數(shù)的表示方法(下),完成浮點(diǎn)四則運(yùn)算的實(shí)現(xiàn)過(guò)程 1.自定義浮點(diǎn)格式加

2024-11-16 12:51:57 1323

1323

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論