點擊上方藍字關注我們

現代信號處理技術通常都需要進行大量高速浮點運算。由于浮點數系統操作比較復雜,需要專用硬件來完成相關的操作(在浮點運算中的浮點加法運算幾乎占到全部運算操作的一半以上),所以,浮點加法器是現代信號處理系統中最重要的部件之一。FPGA是當前數字電路研究開發的一種重要實現形式,它與全定制ASIC電路相比,具有開發周期短、成本低等優點。

但多數FPGA不支持浮點運算,這使FPGA在數值計算、數據分析和信號處理等方面受到了限制,由于FPGA中關于浮點數的運算只能自行設計,因此,研究浮點加法運算的FPGA實現方法很有必要。

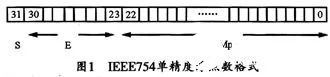

1 IEEE 754單精度浮點數標準

浮點數可以在更大的動態范圍內提供更高的精度,通常,當定點數受其精度和動態范圍所限不能勝任時,浮點數標準則能夠提供良好的解決方案。

IEEE協會制定的二進制浮點數標準的基本格式是32位寬(單精度)和64位寬(雙精度),本文采用單精度格式。圖1所示是IEEE754單精度浮點數格式。圖中,用于單精度的32位二進制數可分為三個獨立的部分,其中第0位到22位構成尾數,第23位到第30位構成指數,第31位是符號位。

實際上,上述格式的單精度浮點數的數值可表示為:

上式中,當其為正數時,S為0;當其為負數時,S為1;(-1)s表示符號。指數E是ON255的變量,E減127可使指數在2-127到2128變化。尾數采用科學計算法表示:M=1.m22m21m20……m0。m22,m21,…,m0,mi為Mp的各位,設計時應注意尾數中隱含的整數部分1。0是一個特殊的數,0的指數位和尾數位均為0,符號位可以是1,也可以是0。

2電路的流水線結構

一般情況下,結構化設計是電路設計中最重要的設計方法之一,采用結構化設計方法可以將一個復雜的電路分割為獨立的功能子模塊,然后按一定的原則將各子模塊組合成完整的電路,這幾乎是電路設計的通用模式。這種設計方法便于設計人員分工合作、實現設計和功能測試,縮短上市時間、升級和二次開發,因而具有其它方法無法比擬的優勢。

結構化設計基本上可歸結為兩種方法:流水線(pipeline)和握手原則。其中握手原則適用于各功能子模塊內部運算比較復雜、數據運算時延(latency)不確定的設計。由于數據運算時延不確定,所以,各子模塊間的時序配合必須通過握手信號的交互才能完成。握手原則設計的電路一般采用復雜的有限狀態機(FSM)作為控制單元,工程設計難度大,故在設計時應慎重使用。流水線法適用于各功能子模塊內部運算簡單整齊、數據運算時延確定的設計。由于數據運算時延比較確定,各前后級功能子模塊不需要任何交互信號就能完成時序配合,故可方便地實現數據的串行流水運算。流水線控制比較簡單,一般不需要設計專門的有限狀態機,而且工程設計容易,設計時可優先選用。

3工程的FPGA實現

3.1開發環境和器件選擇

本工程開發可在FPGA集成開發環境QuartusII 8.0 spl中完成。OuartusⅡ是世界著名PLD設計生產廠商——Altera公司的綜合性PLD開發軟件,內嵌綜合器和仿真器,并有可與第三方工具協作的靈活接口,可以完成從設計輸入到硬件配置的完整PLD設計流程,而且運行速度快,界面統一,功能集中,易學易用。

本設計中的器件選用Stratix IIEP2S15F484C3。Stratix II是Altera公司的高性能FPGA Stratix系列的第二代產品,具有非常高的內核性能,在存儲能力、架構效率、低功耗和面市及時等方面均有優勢。

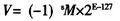

本系統的頂層框圖如圖2所示。為了顯示清楚,圖2被分成兩個部分顯示。本工程采用異步置位的同步電路設計方法,其中clk、reset、enab分別為系統時鐘、系統異步置位、系統使能信號。din_a、din_b分別為兩個輸入的單精度浮點數,data_out則是符合IEEE 754標準的兩輸入浮點數之和。

3.2浮點加法運算的實現

浮點加法運算可總結為比較、移位、相加、規范化等四個步驟,分別對應于compare、shift、sum、normalize四個模塊。

(1)compare模塊

本模塊主要完成兩輸入浮點數的比較,若din_a、din_b為兩個輸入單精度浮點數,則在一個時鐘周期內完成的運算結果如下:

◇大數指數b_exp這里的大數指絕對值的比較;

◇兩浮點數的指數差sube,正數;

◇大數尾數b_ma;

◇小數尾數s_ma,該尾數已加入隱含1;

◇和符號c_sgn,為確定輸出結果的符號;

◇加減選擇add_sub,兩輸入同符號時為0(相加)、異符號時為1(相減),sum模塊中使用實現加減選擇。

(2)shift模塊

shift模塊的作用主要是根據兩個輸入浮點數的指數差來執行小數尾數(已加入隱含1)向右移動相應的位數,以將輸入的兩個浮點數指數調整為相同的數(同大數),若b_exp、sube、b_ma、s_ma、c_sgn、add_sub為輸入信號(其含義見compare模塊),則可輸出如下運算結果(在一個時鐘周期內完成):

◇大數指數(sft_bexp),將b_exp信號用寄存器延遲一個周期,以實現時序同步;

◇小數尾數(sft_sma),已完成向右移動相應的sube位;

◇大數尾數(sft_bma),將b_ma信號用寄存器延遲一個周期,以實現時序同步;

◇和符號(sft_csgn),將c_sgn信號用寄存器延遲一個周期,以實現時序同步;

◇加減選擇(sft_addsub),將add_sub信號用寄存器延遲一個周期,以實現時序同步;

(3)sum模塊

本模塊可根據加減選擇(sft_addsub(信號完成兩輸入浮點數尾數(已加入隱含1)的加減,若sft_bexp、sft_sma、sft_bma、sft_csgn、sft_addsub為輸入信號(其含義見shift模塊),則可輸出如下運算結果(在一個時鐘周期內完成):

◇大數指數(sum_bexp),將sft_bexp信號用寄存器延遲一個周期,以實現時序同步;

◇尾數和(sum_ma),為大數尾數與移位后小數尾數的和,差(兩尾數已加入隱含1);

◇和符號(sum_csgn),將sft_csgn信號用寄存器延遲一個周期,以實現時序同步;

(4)normalize模塊

normalize模塊的作用主要是將前三個模塊的運算結果規范為IEEE 754單精度浮點數標準,若sum_bexp、sum_ma、sum_csgn為輸入信號(其含義見sum模塊),則其輸出的運算結果(在一個時鐘周期內完成)只有一個和輸出(data_out),也就是符合IEEE754浮點數標準的兩個輸入浮點數的和。

4系統綜合與仿真

由于本工程是由compare、shift、sum、normalize四個模塊組成的,而這四個模塊通過串行方式進行連接,每個模塊的操作都在一個時鐘周期內完成,因此,整個浮點數加法運算可在四個時鐘周期內完成。這使得工程不僅有確定的數據運算時延(latency),便于流水線實現,而且方便占用的時鐘周期盡可能減少,從而極大地提高了運算的實時性。

4.1工程綜合結果

經過Quartus II綜合可知,本設計使用的StratixⅡEP2S15F484C3芯片共使用了641個ALUT(高級查找表)、188個寄存器、0位內存和可達到80 MHz的時鐘頻率,因此可證明,本系統利用合理的資源實現了高速浮點數加法運算。

4.2工程仿真結果

本工程仿真可使用Quartus II 8.0內嵌式仿真工具來編寫Matlab程序,以生成大量隨機單精度浮點數(以便于提高仿真代碼覆蓋率,提高仿真的精確度),然后計算它們相加的結果,并以文本形式存放在磁盤文件中。編寫Matlab程序可產生作為仿真輸入的*.vec文件,然后通過時序仿真后生成*.tbl文件,再編寫Matlab程序提取其中有用的結果數據,并與先前磁盤文件中的結果相比較,以驗證設計的正確性。

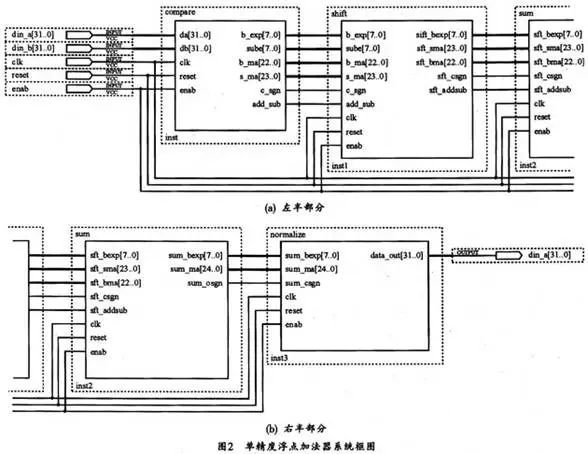

圖3所示是其仿真的波形圖。

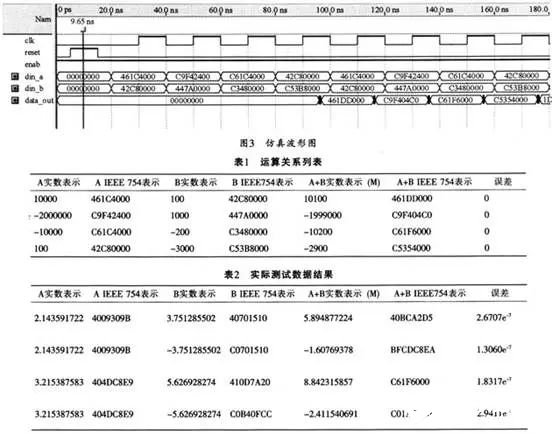

從圖3可以看出表1所列的各種運算關系。表2所列為其實際的測試數據。

表中“A+B實數表示(M)”指Matlab計算的結果;“誤差”指浮點處理器計算結果與Matlab計算結果之差。

綜上所述,本工程設計的浮點加法器所得到的運算結果與Matlab結果的誤差在10-7左右,可見其精度完全能夠符合要求。

本工程設計完全符合IP核設計的規范流程,而且完成了Verilog HDL建模、功能仿真、綜合、時序仿真等IP核設計的整個過程,電路功能正確。實際上,本系統在布局布線后,其系統的最高時鐘頻率可達80MHz。雖然使用浮點數會導致舍入誤差,但這種誤差很小,可以忽略。實踐證明,本工程利用流水線結構,方便地實現了高速、連續、大數據量浮點數的加法運算,而且設計結構合理,性能優異,可以應用在高速信號處理系統中。

有你想看的精彩 至芯科技FPGA就業培訓班——助你步入成功之路、9月23號北京中心開課、歡迎咨詢! CMOS圖像傳感器的FPGA邏輯設計解析 如何使用FPGA器件和USB通訊實現高速數據傳輸顯示系統的設計

掃碼加微信邀請您加入FPGA學習交流群

歡迎加入至芯科技FPGA微信學習交流群,這里有一群優秀的FPGA工程師、學生、老師、這里FPGA技術交流學習氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點個在看你最好看

原文標題:為什么研究浮點加法運算,對FPGA實現方法很有必要?

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1663文章

22486瀏覽量

638635

原文標題:為什么研究浮點加法運算,對FPGA實現方法很有必要?

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

74F583 4位BCD加法器:高速運算的理想之選

十進制計算機算術運算器“加法器”專利申請解析

為什么研究浮點加法運算,對FPGA實現方法很有必要?

為什么研究浮點加法運算,對FPGA實現方法很有必要?

評論