Altera公司近日發(fā)布其面向FPGA的OpenCL (開放計(jì)算語(yǔ)言)早期使用計(jì)劃(EAP),支持客戶提前了解Altera面向FPGA的OpenCL解決方案。采用這一開放標(biāo)準(zhǔn),設(shè)計(jì)團(tuán)隊(duì)可以在高級(jí)C語(yǔ)言框架中面向

2012-09-04 08:47:41 1056

1056 Altera公司今天在2013年安博會(huì)上宣布動(dòng)視元采用Altera基于FPGA的最新視頻分析成功推出首個(gè)基于FPGA的智能交通視頻分析解決方案,較之傳統(tǒng)工控機(jī)或DSP的解決方案,基于FPGA的視頻分析可極大提高偵測(cè)率和節(jié)省成本...

2013-10-29 18:13:44 1429

1429 Altera公司日前宣布在FPGA浮點(diǎn)DSP性能方面實(shí)現(xiàn)了重大突破。

2014-06-09 09:19:54 1442

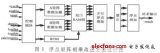

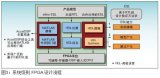

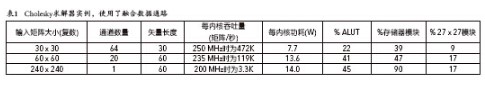

1442 卷積是一種線性運(yùn)算,其本質(zhì)是滑動(dòng)平均思想,廣泛應(yīng)用于圖像濾波。而隨著人工智能及深度學(xué)習(xí)的發(fā)展,卷積也在神經(jīng)網(wǎng)絡(luò)中發(fā)揮重要的作用,如卷積神經(jīng)網(wǎng)絡(luò)。本參考設(shè)計(jì)主要介紹如何基于INTEL 硬浮點(diǎn)的DSP

2018-07-23 09:09:45 8401

8401

語(yǔ)言編寫的浮點(diǎn)矩陣相乘處理單元[1],其關(guān)鍵技術(shù)是乘累加單元的設(shè)計(jì),這樣設(shè)計(jì)的硬件,其性能依賴于設(shè)計(jì)者的編程水平。此外,FPGA廠商也推出了一定規(guī)模的浮點(diǎn)矩陣運(yùn)算IP核[2],雖然此IP核應(yīng)用了本廠家的器件,并經(jīng)過專業(yè)調(diào)試和硬件實(shí)測(cè),性能穩(wěn)定且優(yōu)于手寫代碼,但仍可對(duì)其進(jìn)行改進(jìn),以進(jìn)一步提高運(yùn)算速度。

2019-08-22 06:41:38

描述PMP9353 參考設(shè)計(jì)是 Altera Cyclone V SoC 器件的完整電源解決方案。此設(shè)計(jì)使用多個(gè) LMZ3 系列模塊、兩個(gè) LDO 和一個(gè) DDR 終端穩(wěn)壓器提供為 SoC 芯片供電

2015-05-11 16:45:44

設(shè)計(jì)解決方案43-Altera低壓FPGA的高性能開關(guān)模式電源解決方案

2019-08-09 07:04:51

以下主題概述了Altera的外部?jī)?nèi)存接口解決方案。

Altera提供最快、最高效、延遲最低的內(nèi)存接口IP核。Altera的外部存儲(chǔ)器接口IP設(shè)計(jì)用于方便地與當(dāng)今更高速的存儲(chǔ)器設(shè)備接口。

Altera

2023-09-26 07:38:12

DSP模塊、高性能浮點(diǎn)DSP功能的FPGA,也是目前發(fā)售的唯一具有硬核PCI Express (PCIe ) Gen3 x8 IP模塊和28-Gbps收發(fā)器的FPGA。 Altera公司產(chǎn)品和企業(yè)

2012-05-14 12:38:53

現(xiàn)代工業(yè)系統(tǒng)設(shè)計(jì)人員面臨很多挑戰(zhàn),包括系統(tǒng)復(fù)雜度、標(biāo)準(zhǔn)的變化、性能需求,以及系統(tǒng)總成本等。作為一名工業(yè)系統(tǒng)設(shè)計(jì)人員,當(dāng)你使用的解決方案無(wú)法滿足設(shè)計(jì)需求時(shí),如:當(dāng)需要用MCU或者DSP解決方案同時(shí)

2013-10-11 10:43:19

,FPGA使用 ALTERA的Cyclone3 的 EP3C5E144C8N在設(shè)計(jì)的過程中遇到了很多問題,從原理圖設(shè)計(jì),方案驗(yàn)證,制板,焊接,調(diào)試解決了很多為題,收貨還是蠻多的,DSP28335和FPGA

2016-07-18 16:59:22

FPGA 如何進(jìn)行浮點(diǎn)運(yùn)算

2015-09-26 09:31:37

最近出現(xiàn)的 FPGA設(shè)計(jì)工具和 IP有效減少了計(jì)算占用的資源,大大簡(jiǎn)化了浮點(diǎn)數(shù)據(jù)通路的實(shí)現(xiàn)。而且,與數(shù)字信號(hào)處理器不同, FPGA能夠支持浮點(diǎn)和定點(diǎn)混合工作的 DSP數(shù)據(jù)通路,實(shí)現(xiàn)的性能超過

2019-08-13 06:42:48

的ARM系統(tǒng)。對(duì)于密度、功耗或者性能要求不高的系統(tǒng),這一方法是可行的,但是不一定能滿足更復(fù)雜系統(tǒng)的要求。對(duì)于不斷發(fā)展的系統(tǒng),在FPGA平臺(tái)上結(jié)合經(jīng)過優(yōu)化的硬核ARM是很好的解決方案。圖2由于FPGA

2021-07-14 08:00:00

FPGA的方案選擇 幸運(yùn)的是,需要高性能DSP功能的便攜式設(shè)備設(shè)計(jì)者還有其它選擇。最近FPGA開始達(dá)到了應(yīng)用所要求的成本競(jìng)爭(zhēng)力。優(yōu)選的FPGA方案可用來(lái)處理計(jì)算量繁重的高端DSP算法,同時(shí)還可

2011-02-17 11:21:37

本帖最后由 qzq378271387 于 2012-8-15 16:56 編輯

FPGA_DSP_解決方案

2012-08-15 16:44:32

請(qǐng)問一下各位牛人,我看spartan那個(gè)fpga里面有dsp 資源,我需要做一些浮點(diǎn)運(yùn)算,請(qǐng)問fpga里面的dsp是怎么才能使用的啊,謝謝

2019-10-15 13:37:46

近來(lái),Altera公司推出業(yè)界首款浮點(diǎn)FPGA,它集成了硬核IEEE754兼容浮點(diǎn)運(yùn)算功能,提高了DSP性能、設(shè)計(jì)人員的效能和邏輯效率。據(jù)悉,硬核浮點(diǎn)DSP模塊集成在

2019-07-03 07:56:05

ccs軟件可以在定點(diǎn)dsp平臺(tái)開發(fā)浮點(diǎn)運(yùn)算嗎

2012-10-07 21:54:47

挑戰(zhàn)海嘯模擬將物理過程模擬與大量深海數(shù)據(jù)相結(jié)合。這些計(jì)算通常在大規(guī)模并行超級(jí)計(jì)算機(jī)上完成,但具有硬件利用率低和性能差的缺陷。解決方案通過硬件浮點(diǎn) FPGA 加速模擬內(nèi)循環(huán)可實(shí)現(xiàn)高達(dá) 383

2018-07-27 15:04:13

的ADV7123模塊以PAL格式或者VGA格式顯示,該項(xiàng)目主要評(píng)估C6748的EMIF與FPGA連接時(shí)的數(shù)據(jù)吞吐量(亦或是通過uPP連接FPGA)、浮點(diǎn)運(yùn)算的速度(中值濾波、直方圖統(tǒng)計(jì)等運(yùn)算)這兩項(xiàng)因素乃制約

2015-09-17 10:39:07

處理系統(tǒng)中最重要的部件之一。FPGA是當(dāng)前數(shù)字電路研究開發(fā)的一種重要實(shí)現(xiàn)形式,它與全定制ASIC電路相比,具有開發(fā)周期短、成本低等優(yōu)點(diǎn)。但多數(shù)FPGA不支持浮點(diǎn)運(yùn)算,這使FPGA在數(shù)值計(jì)算、數(shù)據(jù)分析和信號(hào)

2019-07-05 06:21:42

SEED-HPS6678(HPS6678)是北京艾睿合眾科技有限公司新推出的新一代高端DSP+FPGA應(yīng)用方案。DSP采用TI公司首顆最高主頻為10GHz的8核浮點(diǎn)DSP芯片TMS320C6678

2019-09-24 08:29:12

(1)28nm FPGA,在成本、功耗和性能上達(dá)到均衡; (2)包括低功耗6G和10G串行收發(fā)器; (3)總功耗比6G Arria II FPGA低40%; (4)豐富的硬核IP模塊,提高

2012-09-21 13:49:05

的開發(fā)和客戶支持。他們的主要業(yè)務(wù)包括DSP、嵌入式、無(wú)線、視頻和監(jiān)測(cè)等應(yīng)用的 IP(知識(shí)產(chǎn)權(quán))開發(fā)、參考解決方案設(shè)計(jì)和整體解決方案設(shè)計(jì)。

Altera:看好中國(guó)市場(chǎng)

Altera亞太區(qū)副總裁兼董事

2023-11-08 17:19:01

在定點(diǎn)DSP系統(tǒng)中可否實(shí)現(xiàn)浮點(diǎn)運(yùn)算?當(dāng)然可以,因?yàn)?b class="flag-6" style="color: red">DSP都可以用C,只要是可以使用c語(yǔ)言的場(chǎng)合都可以實(shí)現(xiàn)浮點(diǎn)運(yùn)算。

2009-04-07 09:06:17

的ARM系統(tǒng)。對(duì)于密度、功耗或者性能要求不高的系統(tǒng),這一方法是可行的,但是不一定能滿足更復(fù)雜系統(tǒng)的要求。對(duì)于不斷發(fā)展的系統(tǒng),在FPGA平臺(tái)上結(jié)合經(jīng)過優(yōu)化的硬核ARM是很好的解決方案。圖2由于FPGA

2021-07-12 08:00:00

在定點(diǎn)DSP系統(tǒng)中可否實(shí)現(xiàn)浮點(diǎn)運(yùn)算?

2019-09-25 05:55:21

在定點(diǎn)DSP系統(tǒng)中可否實(shí)現(xiàn)浮點(diǎn)運(yùn)算?

2019-09-26 05:55:42

有什么比較好的方法可以提高浮點(diǎn)數(shù)運(yùn)算速度

2023-10-15 11:07:44

您可以顯著提高無(wú)線系統(tǒng)中信號(hào)處理功能的性能。怎樣提高呢?有效方法是利用FPGA結(jié)構(gòu)的靈活性和目前受益于并行處理的FPGA架構(gòu)中的嵌入式DSP模塊。

2019-08-15 07:51:10

有助于使成本和功耗降至最低,而且還能盡可能地加速硬件部署。FPGA 非常適用于執(zhí)行定點(diǎn)運(yùn)算,并能在邏輯或基于軟件或硬件處理器的實(shí)施方案中創(chuàng)建高度并行的數(shù)據(jù)路徑解決方案。Virtex?-5 FPGA 產(chǎn)品

2018-08-03 11:15:23

本帖最后由 eehome 于 2013-1-5 09:53 編輯

用于Xilinx和Altera_FPGA的電源管理解決方案

2012-08-13 22:31:30

分立電源解決方案怎么樣?電源模塊幫助提高DAQ性能的一些方法有什么呀?

2021-03-05 06:02:51

)、更改功率額定值、計(jì)算效率和功率損耗、進(jìn)行每個(gè)電源模塊的仿真、選擇 DC/DC 穩(wěn)壓器的型號(hào)、并認(rèn)證一款定制的解決方案。LTpowerPlanner 可針對(duì) Arria 10 開發(fā)套件的 FPGA

2018-10-29 17:01:56

”視頻分析市場(chǎng)面臨著諸如安裝成本、源視頻質(zhì)量、攝像機(jī)處理能力以及實(shí)時(shí)判決等的重大挑戰(zhàn),相比傳統(tǒng)工控機(jī)或DSP方案,FPGA的解決方案究竟有何優(yōu)勢(shì)?基于FPGA的視頻分析解決方案無(wú)論在成本、性能、市場(chǎng)定制

2013-12-16 19:15:49

非常復(fù)雜,在許多情況下單個(gè) DSP 實(shí)現(xiàn)方案根本沒有足夠的處理能力。同時(shí),系統(tǒng)架構(gòu)也不能滿足多芯片系統(tǒng)帶來(lái)的成本、復(fù)雜性和功耗要求。FPGA 已成為需要高性能 DSP 功能的系統(tǒng)的理想選擇。事實(shí)上

2018-08-15 09:46:21

擴(kuò)展,替代基本的微控制器 (MCU) 或者數(shù)字信號(hào)處理器 (DSP)。 隨著系統(tǒng)復(fù)雜度的提高,FPGA還能夠集成整個(gè)芯片系統(tǒng)(SoC),與分立的 MCU、DSP、ASSP,以及 ASIC解決方案相比

2014-11-05 14:03:37

近年來(lái)變頻控制因其節(jié)能、靜音及低顫動(dòng)而得到廣泛的關(guān)注和應(yīng)用,基于ARM/DSP 的高性能驅(qū)動(dòng)方案為中大功率三相電機(jī)提供了高性能、多控制方式的解決方案,其主要應(yīng)用于對(duì)電機(jī)控制的性能、實(shí)時(shí)性方面要求比較

2019-07-09 08:24:02

模塊(ALM)、精度可調(diào)數(shù)字信號(hào)處理(DSP)模塊、分段式鎖相環(huán)(fPLL)、硬核存儲(chǔ)器控制器等。28LP制造工藝降低設(shè)計(jì)成本Altera在28nm采用了雙管齊下的制造策略,對(duì)于需要盡可能提高帶寬的系統(tǒng)

2015-02-09 15:02:06

Altera公司用FPGA做DSP算法的工具

2006-03-25 13:46:45 39

39

DSP的浮點(diǎn)運(yùn)算方法

2008-01-16 09:25:05 4

4 定點(diǎn)dsp浮點(diǎn)運(yùn)算的多媒體視頻教程:

2008-01-24 09:14:21 50

50

介紹了用VHDL 語(yǔ)言在硬件芯片上實(shí)現(xiàn)浮點(diǎn)加/ 減法、浮點(diǎn)乘法運(yùn)算的方法,并以Altera

公司的FLEX10K系列產(chǎn)品為硬件平臺(tái),以Maxplus II 為軟件工具,實(shí)現(xiàn)了6 點(diǎn)實(shí)序列浮點(diǎn)加/ 減法

2009-07-28 14:06:13 85

85 浮點(diǎn)DSP,浮點(diǎn)DSP是什么意思

浮點(diǎn)DSP可以完成整數(shù)和實(shí)數(shù)運(yùn)算,它的數(shù)據(jù)格式分為階碼和尾數(shù)(有一位可以設(shè)為符號(hào)位)。通常浮點(diǎn)DSP的

2010-03-26 14:57:01 2493

2493 浮點(diǎn)運(yùn)算與浮點(diǎn)運(yùn)算器

浮點(diǎn)加減法的運(yùn)算步驟 設(shè)兩個(gè)浮點(diǎn)數(shù) X=Mx※2Ex Y=My※2Ey 實(shí)現(xiàn)X±Y要用如下5步完成: ①對(duì)階操作:小階

2010-04-15 13:42:32 7293

7293 Altera公司日前演示了使用FPGA的浮點(diǎn)DSP新設(shè)計(jì)流程,這是業(yè)界第一款基于模型的浮點(diǎn)設(shè)計(jì)工具,支持在FPGA中實(shí)現(xiàn)復(fù)數(shù)浮點(diǎn)DSP算法。伯克萊設(shè)計(jì)技術(shù)公司 (Berkeley Design Technology, Inc, BDTI) 進(jìn)行

2011-09-15 08:48:58 1115

1115 Altera公司日前演示了使用FPGA的浮點(diǎn)DSP新設(shè)計(jì)流程,這是業(yè)界第一款基于模型的浮點(diǎn)設(shè)計(jì)工具,支持在FPGA中實(shí)現(xiàn)復(fù)數(shù)浮點(diǎn)DSP算法。

2011-09-15 09:07:10 830

830 延續(xù)其在高清晰(HD) 視頻監(jiān)控解決方案上的領(lǐng)先優(yōu)勢(shì),Altera公司 (NASDAQ: ALTR) 發(fā)布世界上第一款基于FPGA的全HD 1080p/(每秒30幀) 30fps視頻分析解決方案,它采用Cyclone? IV FPGA。Altera的單芯片解

2011-10-19 12:25:53 1363

1363 WP409利用Xilinx FPGA打造出高端比特精度和周期精度浮點(diǎn)DSP算法實(shí)現(xiàn)方案: High-Level Implementation of Bit- and Cycle-Accurate Floating-Point DSP Algorithms with Xilinx FPGAs

2012-01-26 18:03:05 25

25 定點(diǎn)運(yùn)算DSP在應(yīng)用中已取得了極大的成功,而且仍然是DSP應(yīng)用的主體。然而,隨著對(duì)DSP處理速度與精度、存儲(chǔ)器容量、編程的靈活性和方便性要求的不斷提高、自80年代中后期以來(lái),各

2012-03-31 15:19:31 57

57 Altera和Eutecus的高性能、低成本和低功率消耗采用FPGA架構(gòu)的視訊分析解決方案,專門設(shè)計(jì)用于為視訊監(jiān)控系統(tǒng)開發(fā)人員提供靈活的平臺(tái),突出最終系統(tǒng)的優(yōu)勢(shì)。讓設(shè)計(jì)人員能快速方便的獲

2012-05-07 10:06:55 1034

1034 電子發(fā)燒友網(wǎng)訊: 2012 Altera DSP技術(shù)研討會(huì)_視頻應(yīng)用解決方案于2012年8月16日在深圳麗博林諾富特酒店二樓5號(hào)會(huì)議室盛大開幕,電子發(fā)燒友網(wǎng)亦參加了此次研討會(huì)。在這里,小編跟大家一

2012-08-16 20:31:46 2323

2323 嵌入式計(jì)算作為新一代計(jì)算系統(tǒng)的高效運(yùn)行方式,應(yīng)用于多個(gè)高性能領(lǐng)域,如陣列信號(hào)處理、核武器模擬、計(jì)算流體動(dòng)力學(xué)等。在這些科學(xué)計(jì)算中,需要大量的浮點(diǎn)矩陣運(yùn)算。而目前已

2012-10-15 16:57:40 5565

5565

電子發(fā)燒友網(wǎng)核心提示 :Altera公司昨日宣布,在業(yè)界率先在28 nm FPGA器件上成功測(cè)試了復(fù)數(shù)高性能浮點(diǎn)數(shù)字信號(hào)處理(DSP)設(shè)計(jì)。獨(dú)立技術(shù)分析公司Berkeley設(shè)計(jì)技術(shù)有限公司(BDTI)驗(yàn)證

2012-10-31 09:24:47 31

31 電子發(fā)燒友網(wǎng)核心提示 :Altera公司昨日宣布,在業(yè)界率先在28 nm FPGA器件上成功測(cè)試了復(fù)數(shù)高性能浮點(diǎn)數(shù)字信號(hào)處理(DSP)設(shè)計(jì)。獨(dú)立技術(shù)分析公司Berkeley設(shè)計(jì)技術(shù)有限公司(BDTI)驗(yàn)證

2012-10-31 09:22:47 1525

1525 開放計(jì)算語(yǔ)言(OpenCL)編程模型與Altera的并行FPGA體系結(jié)構(gòu)相結(jié)合,實(shí)現(xiàn)了功能強(qiáng)大的系統(tǒng)加速解決方案。面向OpenCL的Altera SDK為您提供了設(shè)計(jì)環(huán)境,工程師很容易在FPGA上實(shí)現(xiàn)OpenCL應(yīng)用。

2012-11-06 14:56:42 2201

2201 面臨著提高性能、降低成本、功能安全三大挑戰(zhàn),Altera 公司致力于FPGA解決方案,加強(qiáng)其在工業(yè)垂直細(xì)分市場(chǎng)中的廣泛使用。

2012-12-18 12:49:07 1114

1114 行業(yè)的基于FPGA和SoC的應(yīng)用解決方案。這些解決方案是由 28nm 的Stratix® V、Arria® V、Cyclone® V FPGA 和 Altera Cyclone

2013-08-06 12:34:04 798

798 電源解決方案,與競(jìng)爭(zhēng)電源解決方案相比,功效提高35%,電路板面積減小50%,總材料(BOM)體電容成本降低了50%。Altera電源優(yōu)化參考設(shè)計(jì)以可下載設(shè)計(jì)包的形式提供給客戶,在Altera開發(fā)

2013-10-22 16:12:15 1409

1409 2014年,12月16號(hào),北京——Altera公司(Nasdaq: ALTR)今天發(fā)布其Quartus? II軟件v14.1,擴(kuò)展支持Arria? 10 FPGA和SoC——FPGA業(yè)界唯一具有硬核浮點(diǎn)DSP模塊的器件,也是業(yè)界唯一集成了ARM處理器的20 nm SoC FPGA。

2014-12-16 13:48:53 1709

1709 STM32F4的浮點(diǎn) DSP 運(yùn)算效率不高

2015-12-07 17:55:14 0

0 DSP芯片的定點(diǎn)運(yùn)算,雖然浮點(diǎn)運(yùn)算逐漸流行,不過定點(diǎn)依然有強(qiáng)大的市場(chǎng)

2016-06-17 16:33:43 7

7 i7處理器的 PC機(jī)的浮點(diǎn)運(yùn)算性能提高1.7倍,功耗僅僅增加10%左右。Rutten寫道: “根據(jù)測(cè)試軟件,一個(gè)典型的i7 PC平臺(tái)的浮點(diǎn)數(shù)運(yùn)算性能大約是每秒75GFLOPS。通過給PC機(jī)增加一個(gè)基于FPGA的SOM,利

2017-02-09 06:15:08 1645

1645 引 言 DSP結(jié)構(gòu)可以分為定點(diǎn)和浮點(diǎn)型兩種。其中,定點(diǎn)型DSP可以實(shí)現(xiàn)整數(shù)、小數(shù)和特定的指數(shù)運(yùn)算,它具有運(yùn)算速度快、占用資源少、成本低等特點(diǎn);靈活地使用定點(diǎn)型DSP進(jìn)行浮點(diǎn)運(yùn)算能夠提高運(yùn)算的效率

2017-11-02 11:26:42 2

2 出于以下幾個(gè)原因,你可能會(huì)考慮使用FPGA來(lái)實(shí)現(xiàn)DSP解決方案。首先是為了提高性能,盡管今天的DSP處理器很快,并對(duì)許多DSP應(yīng)用來(lái)說很有用,但仍有一些應(yīng)用要求性能再進(jìn)一步提升,而FPGA提供了更高

2017-11-06 11:47:52 0

0 您可以顯著提高無(wú)線系統(tǒng)中信號(hào)處理功能的性能。怎樣提高呢?有效方法是利用FPGA結(jié)構(gòu)的靈活性和目前受益于并行處理的FPGA架構(gòu)中的嵌入式DSP模塊。

2018-07-17 11:48:00 1190

1190

各種處理平臺(tái)的GFLOP指標(biāo)在不斷提高,現(xiàn)在,TFLOP/s這一術(shù)語(yǔ)已經(jīng)使用的非常廣泛了。但是,在某些平臺(tái)上,峰值GFLOP/s,即,TFLOP/s表示的器件性能信息有限。它只表示了每秒能夠完成的理論浮點(diǎn)加法或者乘法總數(shù)。分析表明,FPGA單精度浮點(diǎn)處理能夠超過1 TFLOP/s。

2018-02-19 03:53:00 5141

5141 2014年4月8號(hào),北京Altera公司(Nasdaq: ALTR)今天宣布開始提供新款電源轉(zhuǎn)換解決方案,方便了電路板開發(fā)人員設(shè)計(jì)負(fù)載點(diǎn)電源方案,以最低的系統(tǒng)功耗實(shí)現(xiàn)FPGA最佳性能。新款電源轉(zhuǎn)換

2018-02-11 14:30:00 5545

5545 的可編程邏輯公司,前所未有的提高了DSP性能、設(shè)計(jì)人員的效能和邏輯效率。硬核浮點(diǎn)DSP模塊集成在正在發(fā)售的Altera 20 nm Arria 10 FPGA和SoC中,也集成在14 nm Stratix

2018-02-11 13:34:00 7749

7749 為什么 CPU 的浮點(diǎn)運(yùn)算能力比 GPU 差,為什么不提高 CPU 的浮點(diǎn)運(yùn)算能力?

2018-03-16 15:12:02 16274

16274 ,其速度直接影響DSP的速度,因此國(guó)內(nèi)外學(xué)者對(duì)提高浮點(diǎn)乘加單元的性能進(jìn)行了大量的研究。浮點(diǎn)運(yùn)算單元的設(shè)計(jì)主要是在速度和所占用資源之間進(jìn)行權(quán)衡。 本文以實(shí)時(shí)信號(hào)處理為應(yīng)用背景,首先介紹了單精度浮點(diǎn)格式,然后從速度和占用

2018-04-10 10:47:21 8

8 結(jié)構(gòu)復(fù)雜,采用DSP實(shí)現(xiàn)會(huì)增加系統(tǒng)負(fù)擔(dān),降低系統(tǒng)速度。在某些對(duì)速度要求較高的情況,必須采用專門的浮點(diǎn)運(yùn)算處理器。 EDA/FPGA技術(shù)不斷發(fā)展,其高速、應(yīng)用靈活、低成本的優(yōu)點(diǎn)使其廣泛應(yīng)用數(shù)字信號(hào)處理領(lǐng)域。在FPCA技術(shù)應(yīng)用的初期,

2018-04-10 14:25:53 17

17 的功能安全領(lǐng)先供應(yīng)商YOGITECH聯(lián)合開發(fā)的鎖步解決方案采用了Altera FPGA、SoC,認(rèn)證工具流程,以及YOGITECH的知識(shí)產(chǎn)權(quán)(IP)內(nèi)核。這一解決方案幫助客戶在Altera FPGA中輕松實(shí)現(xiàn)SIL3安全設(shè)計(jì),包括低成本Cyclone V FPGA和MAX 10 FPGA系列。

2018-08-31 16:46:00 1857

1857 Altera公司宣布,最新版Altera面向 OpenCL的SDK支持IBM電源系統(tǒng)服務(wù)器作為OpenCL系統(tǒng)主機(jī)。客戶現(xiàn)在可以采用Altera FPGA實(shí)現(xiàn)高性能計(jì)算解決方案,針對(duì)IBM電源系統(tǒng)

2018-09-18 16:34:00 1442

1442 設(shè)計(jì)了一種基于 TI DSP TMS320C6713B 和ALtera Cyclone 系列FPGA 的數(shù)據(jù)采集模塊,使用FPGA 做多路串行AD 器件的信號(hào)采集控制和數(shù)據(jù)緩沖,同時(shí)利用DSP

2019-03-05 16:30:29 17

17 Altera公司今天宣布,NEC將使用Altera的 28nm FPGA,進(jìn)一步提高了其長(zhǎng)期發(fā)展(LTE)基站的性能,支持無(wú)線服務(wù)供應(yīng)商高效的管理他們的網(wǎng)絡(luò)。

2019-05-14 15:34:45 1101

1101 Altera氣旋V系列FPGA的電源解決方案

2021-04-22 20:30:25 7

7 該問題由某客戶提出,發(fā)生在 STM32F407IGT6 器件上。據(jù)其工程師講述:由于在其產(chǎn)品中,需要使用STM32進(jìn)行大量的浮點(diǎn)數(shù)以及浮點(diǎn)DSP運(yùn)算,所以針對(duì)STM32的浮點(diǎn)數(shù)運(yùn)算能力及 DSP

2021-04-28 15:17:02 10

10 Altera Arria V系列FPGA的電源解決方案

2021-04-29 08:58:06 9

9 Altera Stratix V FPGA的電源解決方案

2021-04-29 09:41:47 8

8 設(shè)計(jì)解決方案43-Altera低壓FPGA的高性能開關(guān)模式電源解決方案

2021-04-30 11:55:18 7

7 有些FPGA中是不能直接對(duì)浮點(diǎn)數(shù)進(jìn)行操作的,只能采用定點(diǎn)數(shù)進(jìn)行數(shù)值運(yùn)算。對(duì)于FPGA而言,參與數(shù)學(xué)運(yùn)算的書就是16位的整型數(shù),但如果數(shù)學(xué)運(yùn)算中出現(xiàn)小數(shù)怎么辦呢?要知道,FPGA對(duì)小數(shù)是無(wú)能為力

2021-08-12 09:53:39 5486

5486 使用插值算法實(shí)現(xiàn)圖像縮放是數(shù)字圖像處理算法中經(jīng)常遇到的問題。我們經(jīng)常會(huì)將某種尺寸的圖像轉(zhuǎn)換為其他尺寸的圖像,如放大或者縮小圖像。由于在縮放的過程中會(huì)遇到浮點(diǎn)數(shù),如何在FPGA中正確的處理浮點(diǎn)數(shù)運(yùn)算是在FPGA中實(shí)現(xiàn)圖像縮放的關(guān)鍵。

2022-03-18 11:03:41 5929

5929 隨著 機(jī)器學(xué)習(xí) (Machine Learning)領(lǐng)域越來(lái)越多地使用現(xiàn)場(chǎng)可 編程 門陣列( FPGA )來(lái)進(jìn)行推理(inference)加速,而傳統(tǒng)FPGA只支持定點(diǎn)運(yùn)算的瓶頸越發(fā)凸顯

2023-03-11 13:05:07 1285

1285 ,浮點(diǎn)加法器是現(xiàn)代信號(hào)處理系統(tǒng)中最重要的部件之一。FPGA是當(dāng)前數(shù)字電路研究開發(fā)的一種重要實(shí)現(xiàn)形式,它與全定制ASIC電路相比,具有開發(fā)周期短、成本低等優(yōu)點(diǎn)。 但多數(shù)FPGA不支持浮點(diǎn)運(yùn)算,這使FPGA在數(shù)值計(jì)算、數(shù)據(jù)分析和信號(hào)處理等方

2023-09-22 10:40:03 2116

2116

電子發(fā)燒友網(wǎng)站提供《集成電源解決方案-Altera FPGA應(yīng)用介紹.pdf》資料免費(fèi)下載

2023-11-28 09:21:50 0

0 引言 LMS(最小均方)算法因其收斂速度快及算法實(shí)現(xiàn)簡(jiǎn)單等特點(diǎn)在自適應(yīng)濾波器、自適應(yīng)天線陣技術(shù)等領(lǐng)域得到了十分廣泛的應(yīng)用。為了發(fā)揮算法的最佳性能,必須采用具有大動(dòng)態(tài)范圍及運(yùn)算精度的浮點(diǎn)運(yùn)算,而浮點(diǎn)

2023-12-21 16:40:01 1590

1590 由于定點(diǎn)的四則運(yùn)算比較簡(jiǎn)單,如加減法只要注意符號(hào)擴(kuò)展,小數(shù)點(diǎn)對(duì)齊等問題即可。在本文中,運(yùn)用在前一節(jié)中描述的自定義浮點(diǎn)格式FPGA中數(shù)的表示方法(下),完成浮點(diǎn)四則運(yùn)算的實(shí)現(xiàn)過程 1.自定義浮點(diǎn)格式加

2024-11-16 11:19:23 2139

2139

由于定點(diǎn)的四則運(yùn)算比較簡(jiǎn)單,如加減法只要注意符號(hào)擴(kuò)展,小數(shù)點(diǎn)對(duì)齊等問題即可。在本文中,運(yùn)用在前一節(jié)中描述的自定義浮點(diǎn)格式FPGA中數(shù)的表示方法(下),完成浮點(diǎn)四則運(yùn)算的實(shí)現(xiàn)過程 1.自定義浮點(diǎn)格式加

2024-11-16 12:51:57 1323

1323

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論