2014年4月23號(hào),北京——Altera公司 (Nasdaq: ALTR) 今天宣布在FPGA浮點(diǎn)DSP性能方面實(shí)現(xiàn)了變革。Altera是第一家在FPGA中集成硬核IEEE 754兼容浮點(diǎn)運(yùn)算功能的可編程邏輯公司,前所未有的提高了DSP性能、設(shè)計(jì)人員的效能和邏輯效率。硬核浮點(diǎn)DSP模塊集成在正在發(fā)售的Altera 20 nm Arria 10 FPGA和SoC中,也集成在14 nm Stratix 10 FPGA和SoC中。集成硬核浮點(diǎn)DSP模塊結(jié)合先進(jìn)的高級(jí)工具流程,客戶(hù)可以使用Altera的FPGA和SoC來(lái)滿(mǎn)足越來(lái)越高的大計(jì)算量應(yīng)用需求,例如高性能計(jì)算 (HPC)、雷達(dá)、科學(xué)和醫(yī)療成像等。

含在Arria 10和Stratix 10器件中的硬核單精度浮點(diǎn)DSP模塊基于Altera創(chuàng)新的精度可調(diào)DSP體系結(jié)構(gòu)。傳統(tǒng)的方法使用定點(diǎn)乘法器和FPGA邏輯來(lái)實(shí)現(xiàn)浮點(diǎn)功能,而Altera的硬核浮點(diǎn)DSP與此不同,幾乎不使用現(xiàn)有FPGA浮點(diǎn)計(jì)算所需要的邏輯資源,從而提高了資源效率。這一革命性的技術(shù)支持Altera在Arria 10器件中實(shí)現(xiàn)1.5 TeraFLOP (每秒浮點(diǎn)運(yùn)算次數(shù))的DSP性能,而在Stratix 10器件中DSP性能則高達(dá)10 TeraFLOP。DSP設(shè)計(jì)人員可以選擇定點(diǎn)或者浮點(diǎn)模式,浮點(diǎn)模塊與現(xiàn)有設(shè)計(jì)后向兼容。

Altera 公司軟件、IP及DSP市場(chǎng)總監(jiān)Alex Grbic評(píng)論說(shuō):“在我們的器件中實(shí)現(xiàn)IEEE 754兼容浮點(diǎn)DSP模塊的確在FPGA上實(shí)現(xiàn)了變革。采用硬核浮點(diǎn)功能,Altera FPGA和SoC的性能和功耗效率比在更多的應(yīng)用上優(yōu)于微處理器和GPU。”

FPGA的每瓦性能最高

FPGA具有精細(xì)粒度的密集流水線體系結(jié)構(gòu),因此非常適合用作高性能計(jì)算加速器。器件包含了硬核浮點(diǎn)DSP模塊,因此客戶(hù)可以使用Altera FPGA來(lái)解決大數(shù)據(jù)分析、石油和天然氣行業(yè)的地震建模,以及金融仿真等世界上最復(fù)雜的HPC問(wèn)題。在這些以及很多其他大計(jì)算量應(yīng)用中,與DSP、CPU和GPU相比,F(xiàn)PGA的每瓦性能是最高的。

節(jié)省了數(shù)月的開(kāi)發(fā)時(shí)間

在Altera FPGA和SoC中集成硬核浮點(diǎn)DSP模塊能夠縮短近12個(gè)月的開(kāi)發(fā)時(shí)間。設(shè)計(jì)人員可以將其DSP設(shè)計(jì)直接轉(zhuǎn)譯成浮點(diǎn)硬件,而不是轉(zhuǎn)換為定點(diǎn)。結(jié)果,大幅度縮短了時(shí)序收斂和驗(yàn)證時(shí)間。Altera還提供多種工具流程,幫助硬件設(shè)計(jì)人員、基于模型的設(shè)計(jì)人員以及軟件編程人員在器件中輕松實(shí)現(xiàn)高性能浮點(diǎn)DSP模塊。

?DSP Builder高級(jí)模塊庫(kù)提供了基于模型的設(shè)計(jì)流程,設(shè)計(jì)人員使用業(yè)界標(biāo)準(zhǔn)MathWorks Simulink工具在幾分鐘內(nèi)就可以完成系統(tǒng)定義和仿真,直至系統(tǒng)實(shí)現(xiàn)。

?對(duì)于軟件編程人員,Altera在FPGA編程中率先使用了OpenCL,并面向FPGA提供基于C語(yǔ)言的通用高級(jí)設(shè)計(jì)流程。Arria 10 FPGA浮點(diǎn)DSP模塊結(jié)合使用方便的開(kāi)發(fā)流程,為軟件編程人員提供了硬件直接轉(zhuǎn)譯方法,幫助他們縮短了開(kāi)發(fā)和驗(yàn)證時(shí)間。

Arria 10 FPGA和SoC詳細(xì)信息

基于TSMC 20SoC工藝技術(shù),Arria 10 FPGA和SoC在單個(gè)管芯中實(shí)現(xiàn)了業(yè)界容量最大、性能最好的DSP資源。應(yīng)用專(zhuān)利冗余技術(shù),Altera開(kāi)發(fā)了含有1百15萬(wàn)邏輯單元(LE)的業(yè)界密度最大的20 nm FPGA管芯。Arria 10器件性能比最快的28 nm高端FPGA高出15%,功耗比以前的28 nm Arria系列低40%。

20 nm Arria 10器件是業(yè)界唯一具有硬核浮點(diǎn)DSP模塊的FPGA,也是在FPGA架構(gòu)中嵌入了硬核ARM? Cortex?-A9處理器系統(tǒng)的唯一20 nm SoC。器件帶寬比前一代高4倍,還具有很多其他針對(duì)高性能應(yīng)用進(jìn)行了優(yōu)化的特性。Arria 10器件特性包括:

?芯片至芯片/芯片至模塊接口速率高達(dá)28.3 Gbps的串行收發(fā)器

?支持17.4 Gbps的背板

?單個(gè)器件中含有96個(gè)收發(fā)器通道

?雙核ARM Cortex-A9處理器系統(tǒng)

?硬核浮點(diǎn)DSP模塊

?支持下一代存儲(chǔ)器,包括業(yè)界速率最高的2666 Mbps DDR4,支持高速串行存儲(chǔ)器的混合立方存儲(chǔ)器互操作功能。

供貨信息

現(xiàn)在可以提供具有硬核浮點(diǎn)DSP模塊的Altera 20 nm Arria 10 FPGA。將于2014年下半年提供面向Arria 10器件中硬核浮點(diǎn)DSP模塊的浮點(diǎn)設(shè)計(jì)流程,包括了演示和基準(zhǔn)測(cè)試。客戶(hù)現(xiàn)在可以采用Arria 10 FPGA開(kāi)始設(shè)計(jì),軟件實(shí)現(xiàn)浮點(diǎn),提供設(shè)計(jì)流程支持后,無(wú)縫移植到硬核浮點(diǎn)實(shí)現(xiàn)。

-

dsp

+關(guān)注

關(guān)注

561文章

8262瀏覽量

367683 -

Altera

+關(guān)注

關(guān)注

37文章

826瀏覽量

158975

發(fā)布評(píng)論請(qǐng)先 登錄

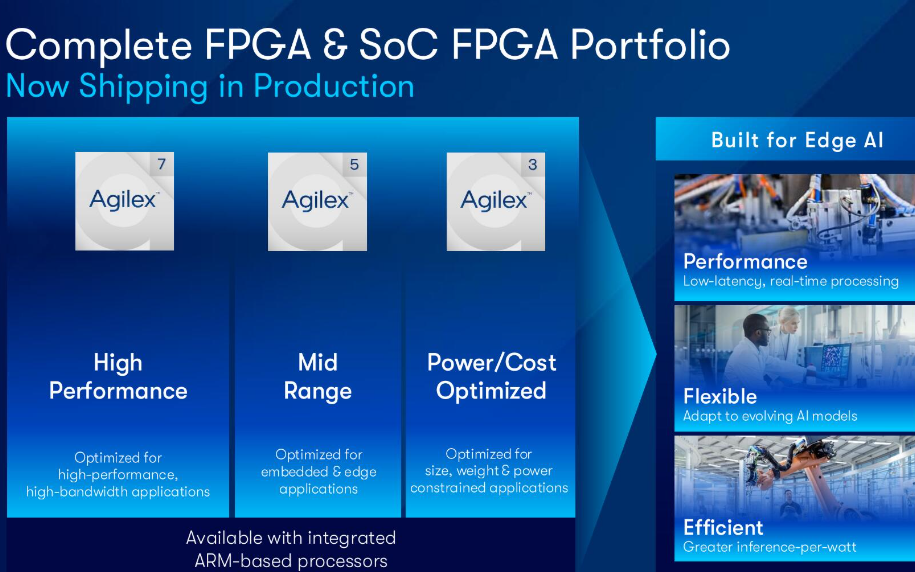

Altera Agilex FPGA與SoC實(shí)現(xiàn)更智能的AI

貿(mào)澤電子開(kāi)售:面向工業(yè)、AI、醫(yī)療、數(shù)據(jù)中心等領(lǐng)域的Altera Agilex 5 FPGA與SoC

深入剖析SMJ320C6701-SP:高性能浮點(diǎn)DSP的卓越之選

Altera攜手合作伙伴共建FPGA創(chuàng)新未來(lái)

Altera Agilex 5系列FPGA與SoC產(chǎn)品榮膺2025全球電子成就獎(jiǎng)

Altera全新推出MAX 10 FPGA封裝新選擇

Altera進(jìn)一步擴(kuò)展 Agilex? FPGA 產(chǎn)品組合,全面提升開(kāi)發(fā)體驗(yàn)

【 VPX638】青翼凌云科技基于KU115 FPGA+C6678 DSP的6U VPX雙FMC接口通用信號(hào)處理平臺(tái)

使用Altera SoC FPGA提升AI信道估計(jì)效率

DGT 互聯(lián)路錐:這項(xiàng)技術(shù)將徹底改變您的公路旅行安全

Altera Agilex 3 FPGA和SoC產(chǎn)品介紹

Altera徹底改變基于FPGA的浮點(diǎn)DSP

Altera徹底改變基于FPGA的浮點(diǎn)DSP

評(píng)論