賽靈思在其FPGA中提供了豐富的時鐘資源,大多數設計人員在他們的FPGA設計中或多或少都會用到。不過對FPGA設計新手來說,什么時候用DCM、PLL、PMCD和MMCM四大類型中的哪一種,讓他們頗為困惑。本文為您解惑......

2013-07-23 09:25:53 20763

20763

時鐘網絡反映了時鐘從時鐘引腳進入FPGA后在FPGA內部的傳播路徑。

2019-09-10 15:12:31 7150

7150

01、如何決定FPGA中需要什么樣的時鐘速率 設計中最快的時鐘將確定 FPGA 必須能處理的時鐘速率。最快時鐘速率由設計中兩個觸發器之間一個信號的傳輸時間 P 來決定,如果 P 大于時鐘周期 T,則

2020-11-23 13:08:24 4644

4644

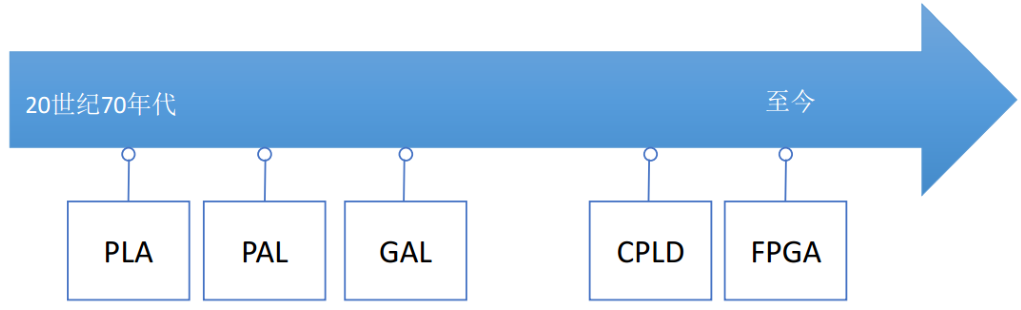

,什么時候用DCM、PLL、PMCD和MMCM四大類型中的哪一種,讓他們頗為困惑。賽靈思現有的FPGA中沒有一款同時包含這四種資源(見表1)。 這四大類中的每一種都針對特定的應用。例如,數字時鐘管理器(DCM)適用于實現延遲鎖相環(DLL)、數字頻率綜合器、數字移相器或數字

2021-02-13 17:02:00 3074

3074

當我剛開始我的FPGA設計生涯時,我對明顯更小、更不靈活的 FPGA(想想 XC4000XL / Clcyone3/4和 Spartan)和工具的非常簡單的時鐘規則之一是盡可能只使用單個時鐘。當然,這并不總是可能的,但即便如此,時鐘的數量仍然有限。

2022-09-30 08:49:26 2145

2145 在FPGA設計中,時序約束對于電路性能和可靠性非常重要。在上一篇的文章中,已經詳細介紹了FPGA時序約束的主時鐘約束。

2023-06-12 17:29:21 4234

4234 “全局時鐘和第二全局時鐘資源”是FPGA同步設計的一個重要概念。合理利用該資源可以改善設計的綜合和實現效果;如果使用不當,不但會影響設計的工作頻率和穩定性等,甚至會導致設計的綜合、實現過程出錯

2023-07-24 11:07:04 1443

1443

通過上一篇文章“時鐘管理技術”,我們了解Xilinx 7系列FPGA主要有全局時鐘、區域時鐘、時鐘管理塊(CMT)。 通過以上時鐘資源的結合,Xilinx 7系列FPGA可實現高性能和可靠的時鐘分配

2023-08-31 10:44:31 4432

4432

本文主要介紹Xilinx FPGA的GTx的參考時鐘。下面就從參考時鐘的模式、參考時鐘的選擇等方面進行介紹。

2023-09-15 09:14:26 5117

5117

有一個有趣的現象,眾多數字設計特別是與FPGA設計相關的教科書都特別強調整個設計最好采用唯一的時鐘域。

2023-12-22 09:04:46 2675

2675

生成時鐘包括自動生成時鐘(又稱為自動衍生時鐘)和用戶生成時鐘。自動生成時鐘通常由PLL或MMCM生成,也可以由具有分頻功能的時鐘緩沖器生成如7系列FPGA中的BUFR、UltraScale系列

2024-01-11 09:50:09 3808

3808

FPGA 在通信領域的應用可以說是無所不能,得益于 FPGA 內部結構的特點,它可以很容易地實現分布式的算法結構,這一點對于實現無線通信中的高速數字信號處理十分有利。

2024-01-24 13:46:33 1553

1553

)圖3.5 心臟示意圖了解了心臟之于人體內部循環系統的作用,反觀時鐘信號之于FPGA器件,其實也有著異曲同工之妙。伴隨著每一次的心跳過程,都有血液的運轉和流動;同樣的,伴隨著每一個時鐘脈沖的產生,也都有數字

2019-04-12 01:15:50

嗨,我是FPGA的新手。我想知道我是否可以有一個設計,我的FPGA的外部時鐘周期性地打開和關閉。我知道Xilinx FPGA使用數字時鐘管理器(DCM)和相位鎖(或使用觸發器延遲鎖定)。因此,我

2019-01-10 10:59:04

,什么時候用DCM、PLL、PMCD和MMCM四大類型中的哪一種,讓他們頗為困惑。賽靈思現有的FPGA中沒有一款同時包含這四種資源(見表1)。 這四大類中的每一種都針對特定的應用。例如,數字時鐘管理器

2020-04-25 07:00:00

請教一下LabVIEW的大神們,我現在希望用FPGA板卡(PXI-7852R)的多個DIO口輸出不同的精確的數字時鐘,我能用內置的40MHz衍生成最低2.5M的時鐘,利用這個時鐘可以通過單周期定時

2013-01-08 20:20:14

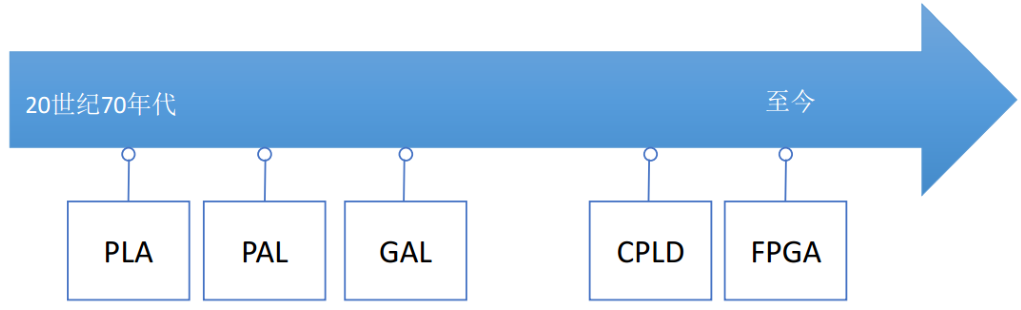

中從電子設計的外圍器件逐漸演變為數字系統的核心。伴隨著半導體工藝技術的進步,FPGA器件的設計技術取得了飛躍發展及突破。分頻器通常用來對某個給定的時鐘頻率進行分頻,以得到所需的時鐘頻率。在設計數字

2019-10-08 10:08:10

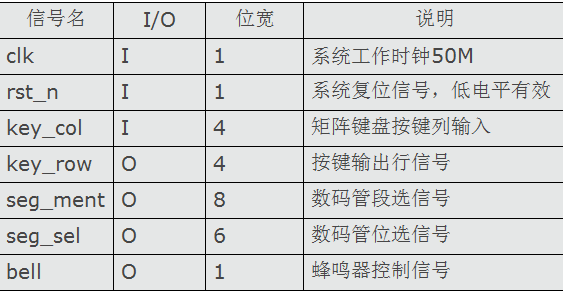

視頻過大,打包成8個壓縮包基于FPGA設計的數字時鐘.part01.rar (20 MB )基于FPGA設計的數字時鐘.part02.rar (20 MB )基于FPGA設計的數字時鐘

2019-05-14 06:35:34

更多項目/畢設下載和技術交流請加FPGA交流群:97925396視頻過大,打包成8個壓縮包

2018-11-23 10:31:30

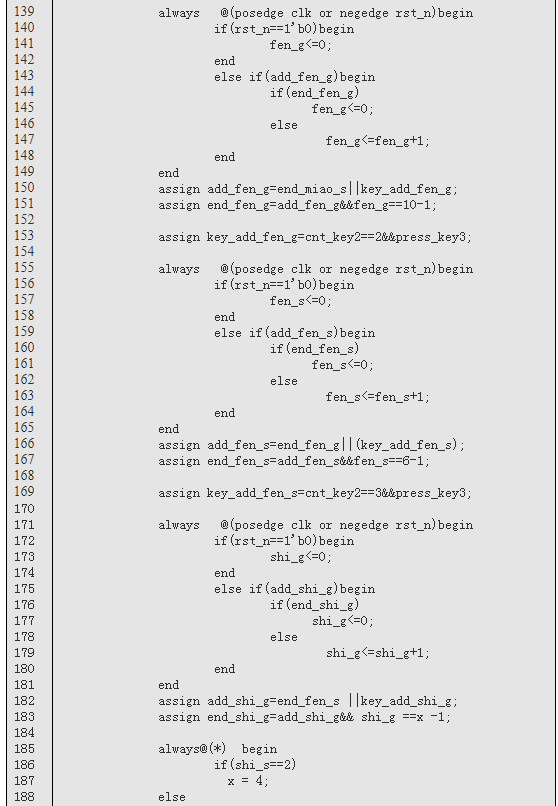

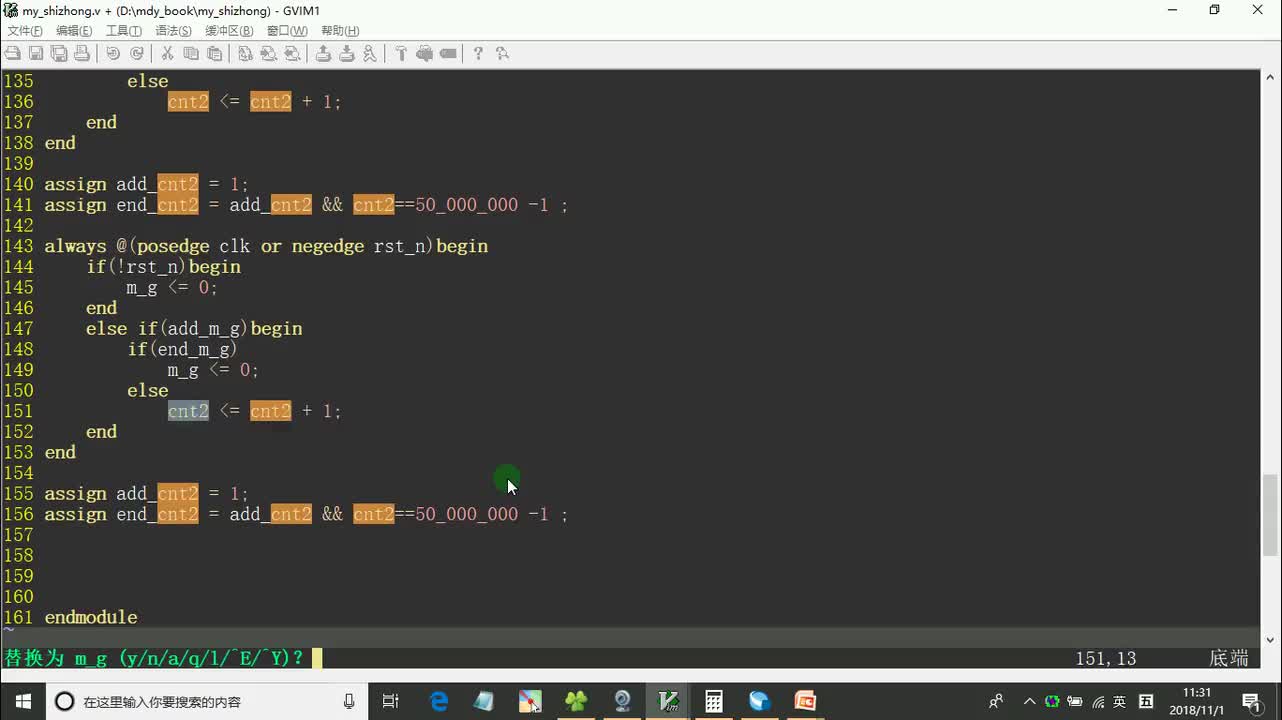

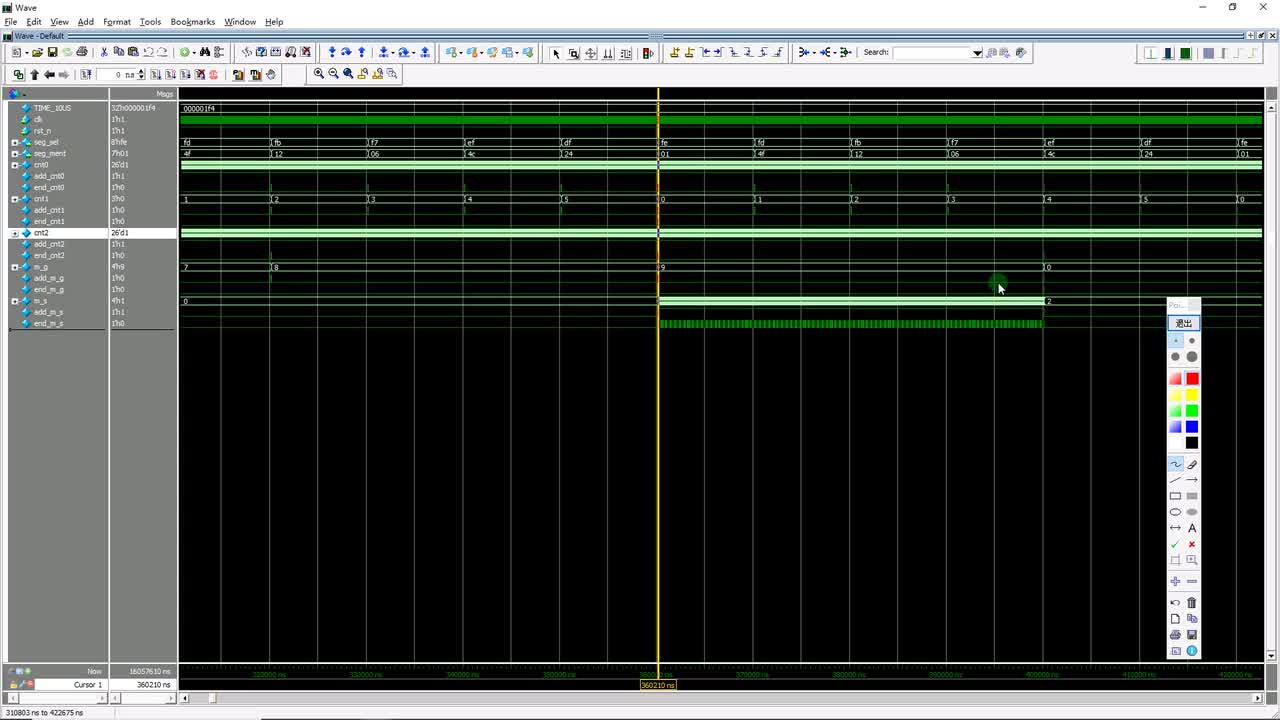

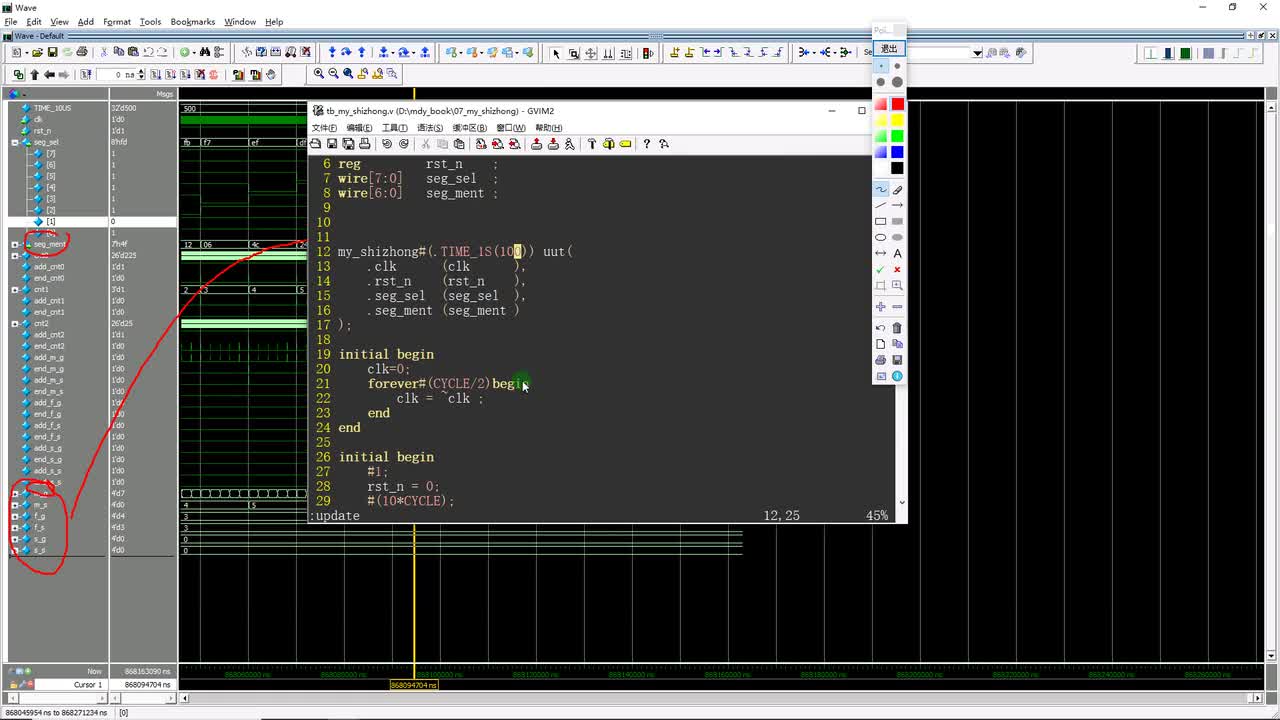

本文屬于本人原創,和大家一起學習FPGA,交流FPGA,希望大家多多支持。今天內容為數字時鐘設計,詳細內容看以下文件,文檔為設計文檔,project為代碼源程序。

2017-09-21 10:46:59

1.FPGA管腳是否具有電平判決功能將輸入的模擬時鐘信號判決為數字時鐘信號?2.單載波輸入,LVDS或者LVPECL差分輸出方波時鐘信號,應該選擇什么器件?

2018-12-20 09:31:59

在介紹了GPS 同步時鐘基本原理和FPGA 特點的基礎上,提出了一種基于FPGA 的GPS同步時鐘裝置的設計方案,實現了高精度同步時間信號和同步脈沖的輸出,以及GPS 失步后秒脈沖的平

2009-07-30 11:51:45 45

45 一種FPGA時鐘網絡中鎖相環的實現方案:摘 要:本文闡述了用于FPGA 的可優化時鐘分配網絡功耗與面積的時鐘布線結構模型。并在時鐘分配網絡中引入數字延遲鎖相環減少時鐘偏差,探

2009-08-08 09:07:22 25

25 影響FPGA設計中時鐘因素的探討:時鐘是整個電路最重要、最特殊的信號,系統內大部分器件的動作都是在時鐘的跳變沿上進行, 這就要求時鐘信號時延差要非常小, 否則就可能造成時

2009-11-01 14:58:33 26

26 DLL在FPGA時鐘設計中的應用:在ISE集成開發環境中,用硬件描述語言對FPGA 的內部資源DLL等直接例化,實現其消除時鐘的相位偏差、倍頻和分頻的功能。時鐘電路是FPGA開發板設計中的

2009-11-01 15:10:30 33

33 本文闡述了用于FPGA的可優化時鐘分配網絡功耗與面積的時鐘布線結構模型。并在時鐘分配網絡中引入數字延遲鎖相環減少時鐘偏差,探討了FPGA時鐘網絡中鎖相環的實現方案。

2010-08-06 16:08:45 12

12 提出了一種基于FPGA的時鐘跟蹤環路的設計方案,該方案簡化了時鐘跟蹤環路的結構,降低了時鐘調整電路的復雜度。實際電路測試結果表明,該方案能夠使接收機時鐘快速準確地跟蹤發

2010-11-19 14:46:54 31

31 大型設計中FPGA的多時鐘設計策略

利用FPGA實現大型設計時,可能需要FPGA具有以多個時鐘運行的多重數據通路,這種多時鐘FPGA設計必須特別小心,需要注意最大時鐘速率

2009-12-27 13:28:04 827

827

基于FPGA的提取位同步時鐘DPLL設計

在數字通信系統中,同步技術是非常重要的,而位同步是最基本的同步。位同步時鐘信號不僅用于監測輸入碼元信號,確保收發

2010-01-25 09:36:18 3699

3699

在FPGA設計中,為了成功地操作,可靠的時鐘是非常關鍵的。設計不良的時鐘在極限的溫度、電壓下將導致錯誤的行為。在設計PLD/FPGA時通常采用如下四種類型時鐘:全局時鐘、門控時鐘

2011-09-21 18:38:58 4131

4131

提出了一種基于數字示波器原理,以單片機和FPGA為控制核心的數字示波器實現方法。系統由信號調理、程控放大、比較整形和時鐘產生、采樣控制、測頻模塊和校準信號產生等模塊組成

2011-10-08 15:31:53 277

277 在Quartus Ⅱ開發環境下,用Verilog HDL硬件描述語言設計了一個可以在FPGA芯片上實現的數字時鐘. 通過將設計代碼下載到FPGA的開發平臺Altera DE2開發板上進行了功能驗證. 由于數字時鐘的通用

2011-11-29 16:51:43 184

184 FPGA 異步時鐘設計中如何避免亞穩態的產生是一個必須考慮的問題。本文介紹了FPGA 異步時鐘設計中容易產生的亞穩態現象及其可能造成的危害,同時根據實踐經驗給出了解決這些問題的

2011-12-20 17:08:35 63

63 SERDES在數字系統中高效時鐘設計方案,無論是在一個FPGA、SoC還是ASSP中,為任何基于SERDES的協議選擇一個參考時鐘源都是非常具有挑戰性的。

2012-02-16 11:23:43 11669

11669

利用FPGA實現大型設計時,可能需要FPGA具有以多個時鐘運行的多重數據通路,這種多時鐘FPGA設計必須特別小心,需要注意最大時鐘速率、抖動、最大時鐘數、異步時鐘設計和時鐘/數

2012-05-21 11:26:10 1591

1591

本文以FPGA平臺為基礎,在QuartusⅡ開發環境下設計開發多功能數字鐘。數字鐘實現計時\校時\整點報時\世界時鐘功能.

2012-12-18 11:51:03 40365

40365 2013-12-26 10:33:21 43

43 DLL在_FPGA時鐘設計中的應用,主要說明DLL的原理,在Xilinx FPGA中是怎么實現的。

2015-10-28 14:25:42 1

1 低功耗時鐘門控算術邏輯單元在不同FPGA中的時鐘能量分析

2015-11-19 14:50:20 0

0 數字時鐘

2016-03-11 16:12:41 72

72 基于FPGA的數字時鐘設計,可實現鬧鐘的功能,可校時。

2016-06-23 17:15:59 71

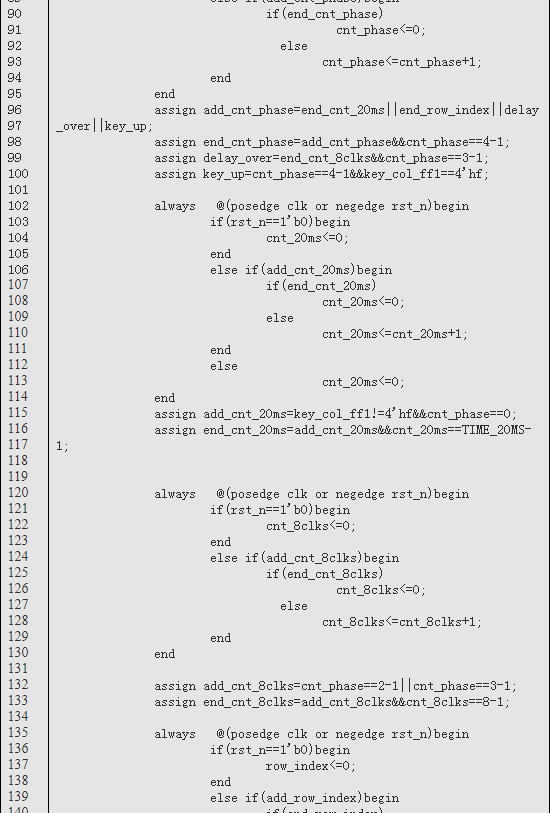

71 用Verilog寫的數字鐘,可調小時,分鐘,秒,模塊化設計,內部消抖,數碼管掃描等小模塊便于移植,已上板驗證通過

2016-08-09 17:12:33 15

15 數字時鐘C語音程序

2016-12-17 11:06:10 7

7 一種基于FPGA的時鐘相移時間數字轉換器_王巍

2017-01-07 22:23:13 3

3 如何正確使用FPGA的時鐘資源

2017-01-18 20:39:13 22

22 目前,大型設計一般推薦使用同步時序電路。同步時序電路基于時鐘觸發沿設計,對時鐘的周期、占空比、延時和抖動提出了更高的要求。為了滿足同步時序設計的要求,一般在FPGA設計中采用全局時鐘資源驅動設計的主時鐘,以達到最低的時鐘抖動和延遲。

2017-02-11 11:34:11 5427

5427 業內大多數FPGA 均提供數字時鐘管理( 賽靈思公司的全部FPGA 均具有這種特性)。賽靈思公司推出最先進的FPGA 提供數字時鐘管理和相位環路鎖定。相位環路鎖定能夠提供精確的時鐘綜合,且能夠降低抖動,并實現過濾功能。

2017-02-11 17:01:11 2173

2173

介紹一種采用FPGA(現場可編程門陣列電路)實現SDH(同步數字體系)設備時鐘芯片設計技術,硬件主要由1 個FPGA 和1 個高精度溫補時鐘組成.通過該技術,可以在FPGA 中實現需要專用芯片才能實現的時鐘芯片各種功能,而且輸入時鐘數量對比專用芯片更加靈活,實現該功能的成本降低三分之一.

2017-11-21 09:59:00 2653

2653

無淪是用離散邏輯、可編程邏輯,還是用全定制硅器件實現的任何數字設計,為了成功地操作,可靠的時鐘是非常關鍵的。設計不良的時鐘在極限的溫度、電壓或制造工藝的偏差情況下將導致錯誤的行為,并且調試困難、花銷

2017-11-25 09:16:01 5020

5020

一般情況下,FPGA器件內部的邏輯會在每個時鐘周期的上升沿執行一次數據的輸入和輸出處理,而在兩個時鐘上升沿的空閑時間里,則可以用于執行各種各樣復雜的處理。而一個比較耗時的復雜運算過程,往往無法一個時鐘周期完成,便可以切割成幾個耗時較小的運算,然后在數個時鐘上升沿后輸出最終的運算結果。

2018-05-23 05:56:00 8320

8320

基于FPGA的數字系統設計中大都推薦采用同步時序的設計,也就是單時鐘系統。但是實際的工程中,純粹單時鐘系統設計的情況很少,特別是設計模塊與外圍芯片的通信中,跨時鐘域的情況經常不可避免。如果對跨時鐘域

2018-09-01 08:29:21 6010

6010

跨時鐘域問題(CDC,Clock Domain Crossing )是多時鐘設計中的常見現象。在FPGA領域,互動的異步時鐘域的數量急劇增加。通常不止數百個,而是超過一千個時鐘域。

2019-08-19 14:52:58 3895

3895 時鐘是FPGA設計中最重要的信號,FPGA系統內大部分器件的動作都是在時鐘的上升沿或者下降沿進行。

2019-09-20 15:10:18 6055

6055

有一個有趣的現象,眾多數字設計特別是與FPGA設計相關的教科書都特別強調整個設計最好采用唯一的時鐘域。

2020-09-24 10:20:00 3603

3603

時鐘網絡反映了時鐘從時鐘引腳進入FPGA后在FPGA內部的傳播路徑。 報告時鐘網絡命令可以從以下位置運行: A,VivadoIDE中的Flow Navigator; B,Tcl命令

2020-11-29 09:41:00 3695

3695 。 不要隨意將內部信號作為時鐘,如門控時鐘和分頻時鐘,而要使用CLKDLL或者DCM產生的時鐘,或者可以通過建立時鐘使能或者DCM產生不同的時鐘信號。 FPGA盡量采取同步設計,也就是所有時鐘都是同一個源頭,如果使用兩個沒有相位關系的異步時鐘,必須

2020-12-11 10:26:44 2426

2426 區域(Region):每個FPGA器件被分為多個區域,不同的型號的器件區域數量不同。

FPGA時鐘資源主要有三大類:時鐘管理模、時鐘IO、時鐘布線資源。

時鐘管理模塊:不同廠家及型號的FPGA中

2020-12-09 14:49:03 21

21 FPGA時鐘資源主要有三大類 時鐘管理模、時鐘 IO 、時鐘布線資源。

2020-12-09 18:14:00 13

13 本文檔的主要內容詳細介紹的是FPGA硬件基礎之FPGA時鐘資源的工程文件免費下載。

2020-12-10 15:00:29 16

16 利用 FPGA 實現大型設計時,可能需要FPGA 具有以多個時鐘運行的多重數據通路,這種多時鐘FPGA 設計必須特別小心,需要注意最大時鐘速率、抖動、最大時鐘數、異步時鐘設計和時鐘/數據關系。設計過程中最重要的一步是確定要用多少個不同的時鐘,以及如何進行布線,本文將對這些設計策略深入闡述。

2021-01-15 15:57:00 14

14 引言:本文我們介紹一下全局時鐘資源。全局時鐘是一個專用的互連網絡,專門設計用于到達FPGA中各種資源的所有時鐘輸入。這些網絡被設計成具有低偏移和低占空比失真、低功耗和改進的抖動容限。它們也被設計成

2021-03-22 10:09:58 14973

14973

引言:7系列FPGA具有多個時鐘路由資源,以支持各種時鐘方案和要求,包括高扇出、短傳播延遲和極低的偏移。為了最好地利用時鐘路由資源,必須了解如何從PCB到FPGA獲取用戶時鐘,確定哪些時鐘路由資源

2021-03-22 10:16:18 6115

6115

引言:從本文開始,我們陸續介紹Xilinx 7系列FPGA的時鐘資源架構,熟練掌握時鐘資源對于FPGA硬件設計工程師及軟件設計工程師都非常重要。本章概述7系列FPGA時鐘,比較了7系列FPGA時鐘

2021-03-22 10:25:27 6070

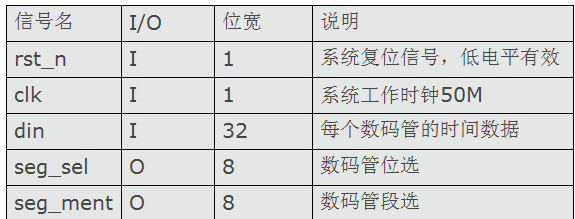

6070 EDA技術使得電子線路的設計人員能在計算機上完成電路的功能設計、邏輯設計、時序測試直至印刷電路板的自動設計。本文介紹了以 VHDL 語言和硬件電路為表達方式,以 Quartus II 軟件為設計工具,最終通過 FPGA 器件實現數字時鐘的設計過程。

2021-05-25 16:28:10 40

40 利用數字電子技術、EDA設計方法、FPGA等技術,設計、仿真并實現一個基于FPGA的數字電子時鐘基本功能,其基本組成框圖如圖1所示,振蕩器采用ALTERA的DE2-70實驗板的50MHz輸出,分頻器

2021-05-28 10:47:50 59

59 基于FPGA的數字時鐘設計畢業設計論文免費下載。

2021-05-28 10:49:19 75

75 有一個有趣的現象,眾多數字設計特別是與FPGA設計相關的教科書都特別強調整個設計最好采用唯一的時鐘域。換句話說,只有一個獨立的網絡可以驅動一個設計中所有觸發器的時鐘端口。雖然這樣可以簡化時序分析以及

2021-09-23 16:39:54 3632

3632 在設計FPGA項目的時候,對時鐘進行約束,但是因為算法或者硬件的原因,都使得時鐘約束出現超差現象,接下來主要就是解決時鐘超差問題,主要方法有以下幾點。 第一:換一個速度更快點的芯片,altera公司

2021-10-11 14:52:00 4267

4267

(08)FPGA時鐘概念1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA時鐘概念5)結語1.2 FPGA簡介FPGA(Field Programmable Gate

2021-12-29 19:41:17 2

2 (12)FPGA時鐘設計原則1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA時鐘設計原則5)結語1.2 FPGA簡介FPGA(Field Programmable

2021-12-29 19:41:27 17

17 (29)FPGA原語設計(差分時鐘轉單端時鐘)1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA原語設計(差分時鐘轉單端時鐘)5)結語1.2 FPGA簡介FPGA

2021-12-29 19:41:38 5

5 (30)FPGA原語設計(單端時鐘轉差分時鐘)1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA原語設計(單端時鐘轉差分時鐘)5)結語1.2 FPGA簡介FPGA

2021-12-29 19:41:48 10

10 ?xilinx 的 FPGA 時鐘結構,7 系列 FPGA 的時鐘結構和前面幾個系列的時鐘結構有了很大的區別,7系列的時鐘結構如下圖所示。

2022-07-03 17:13:48 4699

4699 電子發燒友網站提供《使用FPGA的數字時鐘(計時表).zip》資料免費下載

2022-11-23 10:38:36 7

7 ASIC 和FPGA芯片的內核之間最大的不同莫過于時鐘結構。ASIC設計需要采用諸如時鐘樹綜合、時鐘延遲匹配等方式對整個時鐘結構進行處理,但是 FPGA設計則完全不必。

2022-11-23 16:50:49 1249

1249

如果SoC設計規模小,在單個FPGA內可以容納,那么只要系統中的FPGA具有所SoC所設計需要時鐘的數量

2023-04-07 09:42:57 1705

1705 如果SoC設計規模小,在單個FPGA內可以容納,那么只要系統中的FPGA具有所SoC所設計需要時鐘的數量

2023-05-23 15:46:24 1420

1420

時鐘是每個 FPGA 設計的核心。如果我們正確地設計時鐘架構、沒有 CDC 問題并正確進行約束設計,就可以減少與工具斗爭的時間。

2023-07-12 11:17:42 1817

1817

有一個有趣的現象,眾多數字設計特別是與FPGA設計相關的教科書都特別強調整個設計最好采用唯一的時鐘域。換句話說,只有一個獨立的網絡可以驅動一個設計中所有觸發器的時鐘端口。雖然這樣可以簡化時序分析以及

2023-08-23 16:10:01 1372

1372 fpga跨時鐘域通信時,慢時鐘如何讀取快時鐘發送過來的數據? 在FPGA設計中,通常需要跨時鐘域進行數據通信。跨時鐘域通信就是在不同的時鐘域之間傳輸數據。 當從一個時鐘域傳輸數據到另一個時鐘域

2023-10-18 15:23:51 1901

1901 fpga與dsp通訊怎樣同步時鐘頻率?dsp和fpga通信如何測試? 在FPGA與DSP通訊時,同步時鐘頻率非常重要,因為不同的設備有不同的時鐘頻率,如果兩者的時鐘頻率不同步,會導致通訊數據的錯誤或

2023-10-18 15:28:13 2793

2793 FPGA為什么有時候還需要一個時鐘配置芯片提供時鐘呢? FPGA(Field Programmable Gate Array)是一種可編程邏輯器件,可以根據不同需要編程,實現不同的功能。在FPGA中

2023-10-25 15:14:20 2400

2400 FPGA(可編程邏輯門陣列)是一種集成電路芯片,具有可編程的數字邏輯功能。多功能數字鐘系統利用FPGA技術實現了時鐘的顯示、計時、報時等功能。本文將詳細介紹FPGA多功能數字鐘系統的原理。 一

2024-01-02 16:50:57 2245

2245 FPGA輸入的時鐘信號必須是方波么?正弦波會有影響么? FPGA是一種可編程邏輯器件,通常用于實現數字電路。輸入時鐘信號是FPGA中非常重要的時序信號,對整個系統的穩定性和性能都有很大影響。在

2024-01-31 11:31:42 5410

5410 FPGA 中包含一些全局時鐘資源。以AMD公司近年的主流FPGA為例,這些時鐘資源由CMT(時鐘管理器)產生,包括DCM、PLL和MMCM等。

2024-04-25 12:58:30 3304

3304

在FPGA(現場可編程門陣列)設計中,消除時鐘抖動是一個關鍵任務,因為時鐘抖動會直接影響系統的時序性能、穩定性和可靠性。以下將詳細闡述FPGA中消除時鐘抖動的多種方法,這些方法涵蓋了從硬件設計到軟件優化的各個方面。

2024-08-19 17:58:54 3753

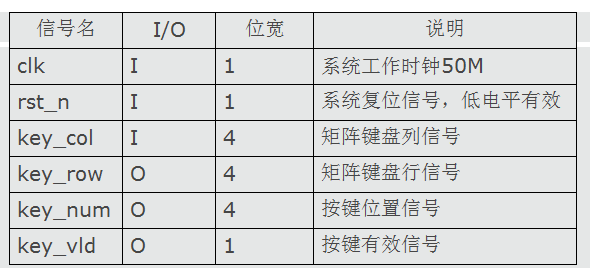

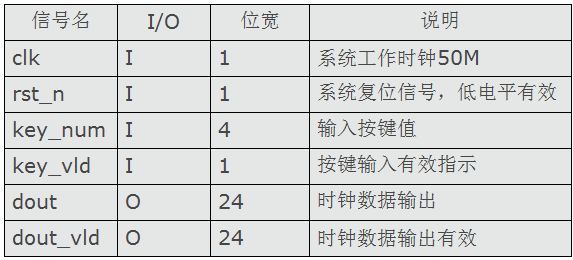

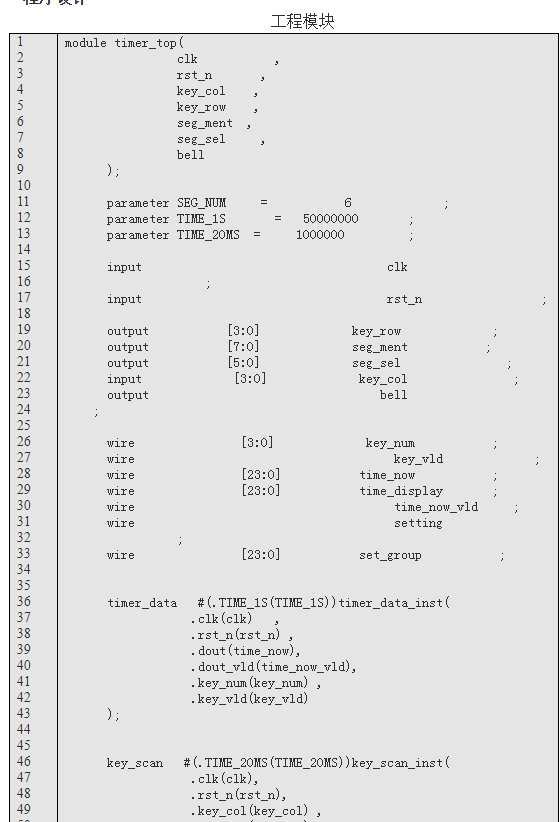

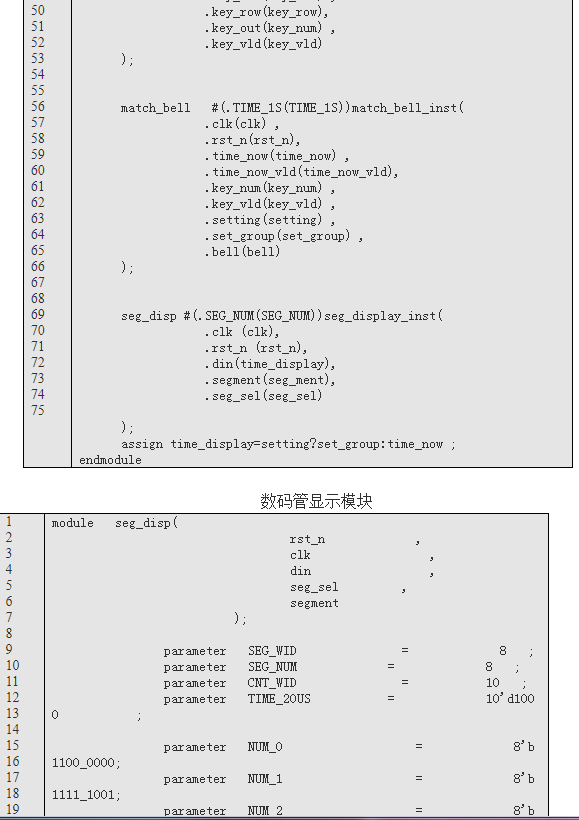

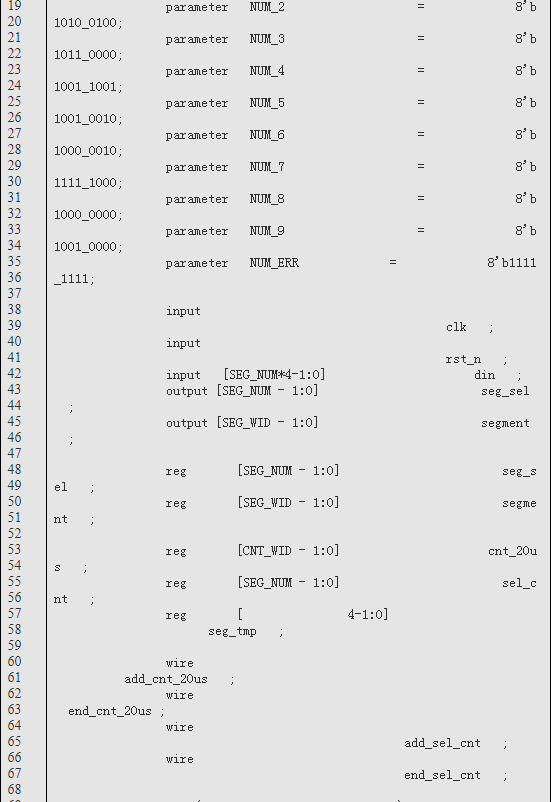

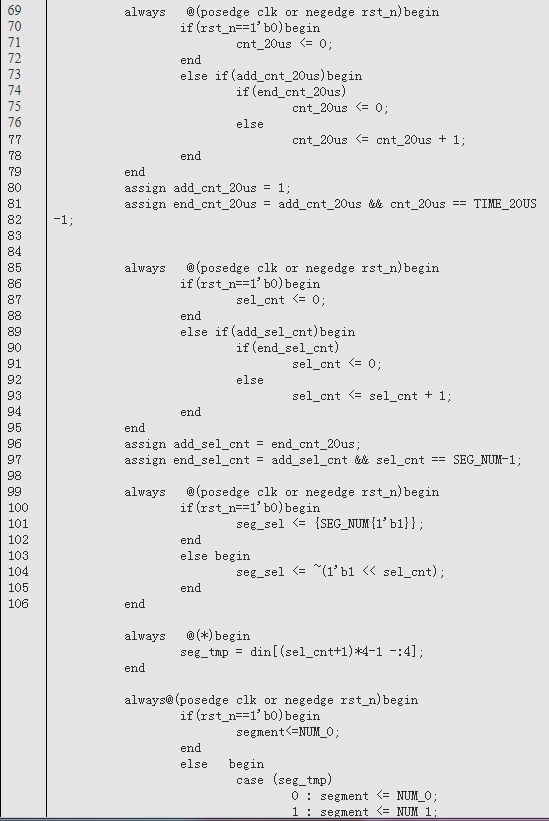

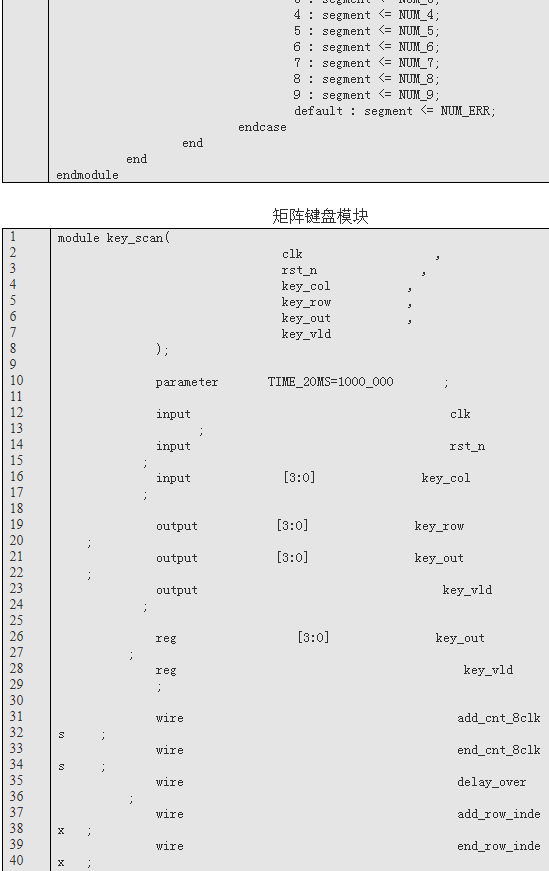

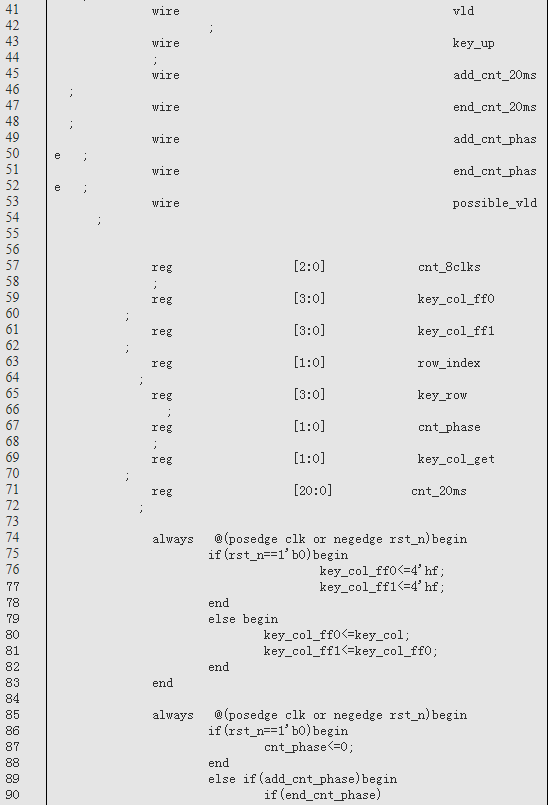

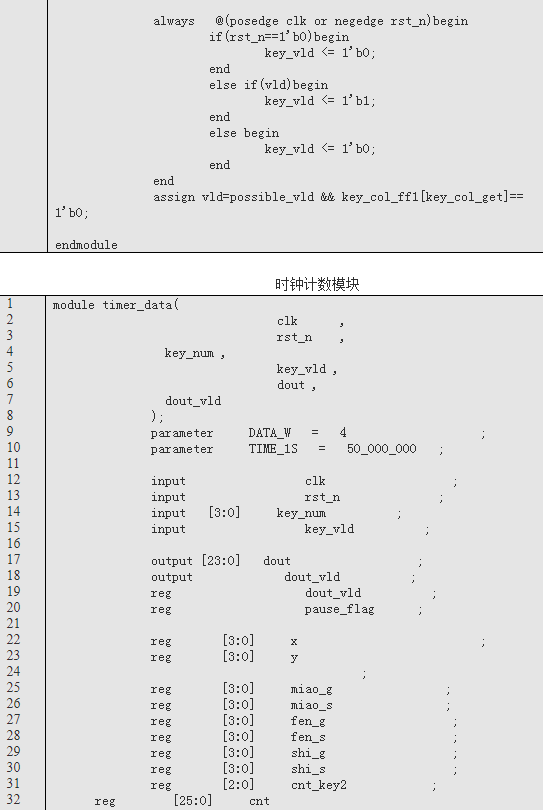

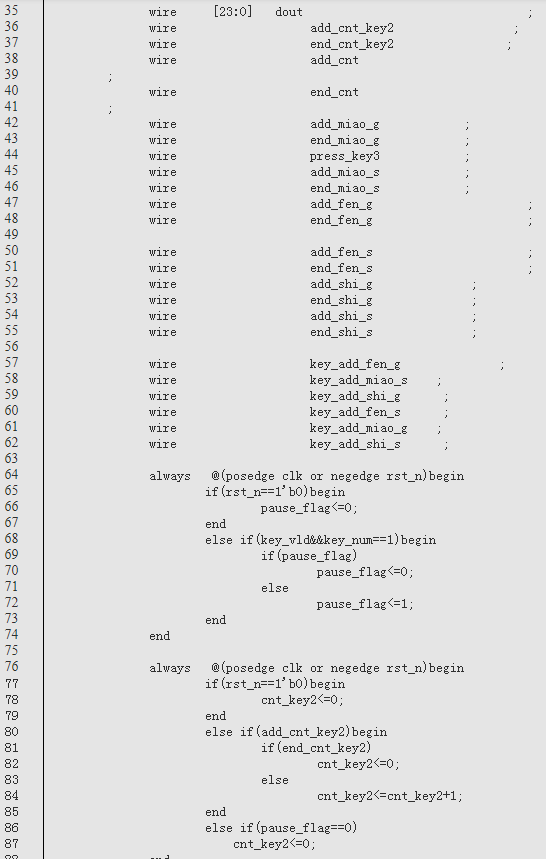

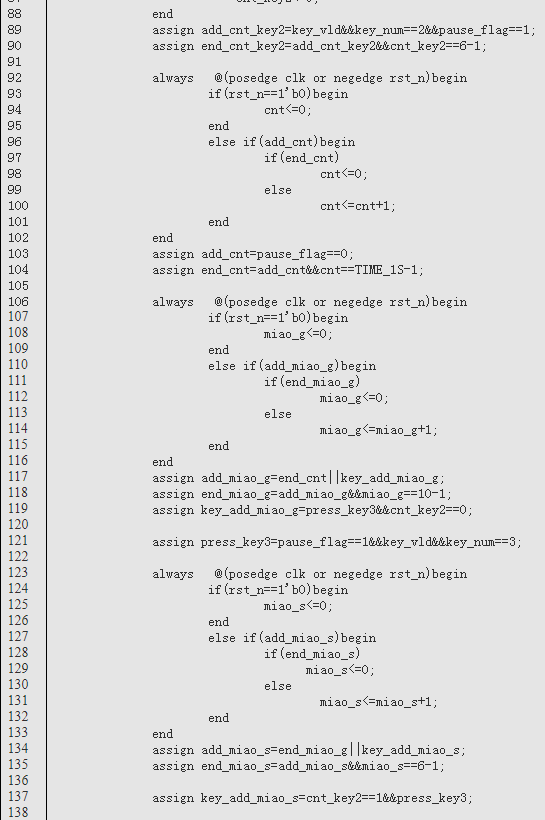

3753 本次的設計的數字鐘思路描述如下,使用3個key按鍵,上電后,需要先配置數字時鐘的時分秒,設計一個按鍵來控制數字時鐘的時,第二個按鍵來控制數字時鐘的分,本次設計沒有用按鍵控制數字時鐘的秒,原理一樣

2025-01-21 10:29:00 1302

1302

電子發燒友App

電子發燒友App

評論