引言:7系列FPGA具有多個時鐘路由資源,以支持各種時鐘方案和要求,包括高扇出、短傳播延遲和極低的偏移。為了最好地利用時鐘路由資源,必須了解如何從PCB到FPGA獲取用戶時鐘,確定哪些時鐘路由資源是最佳的,然后通過使用適當?shù)腎/O和時鐘緩沖器來訪問這些時鐘路由資源。該章節(jié)包括:

時鐘緩沖選擇考慮

時鐘輸入管腳

1.時鐘緩沖器選擇考慮

7系列FPGA擁有豐富的時鐘資源。各種緩沖器類型、時鐘輸入管腳和時鐘連接,可以滿足許多不同的應(yīng)用需求。選擇合適的時鐘資源可以改善布線、性能和一般FPGA資源利用率。BUFGCTRL(最常用作BUFG)是最常用的時鐘布線資源。這些真正的全局時鐘可以連接到器件的任何位置。但是在某些情況下,出于性能、功能或時鐘資源可用性的原因,使用備用時鐘緩沖器更為有利。最好在以下情況下使用BUFG:

設(shè)計或設(shè)計的一部分可以覆蓋整個器件的大面積區(qū)域,功能的本地化是不可能的。

硬件功能塊,如塊RAM、DSP或集成IP,跨越多個時鐘區(qū)域,級聯(lián)或需要連接到不在附近的CLB。

同步(glitch free)或異步時鐘切換,應(yīng)用程序能夠從停止的時鐘切換或選擇具有不同頻率的時鐘(例如,用于降低功耗)。

時鐘使能(CE)功能可用于在非運行期間降低功率。然而,在大多數(shù)情況下,由于時序(CE延遲)的限制,CE不能夠用于在時鐘元件處模擬真實的CE邏輯功能。

CE功能可用于在器件啟動后同步已初始化的時鐘元件。

BUFR和BUFIO組合的主要目的是支持源同步接口(如圖1所示)。當一個接口被放置在一個區(qū)域中時,BUFIO對SelectIOs的高速側(cè)進行時鐘控制,BUFR以較低的速度將解串器/串行器側(cè)時鐘送入提供時鐘域傳輸功能的FPGA邏輯中。對于需要更多邏輯和/或I/O的接口,BUFMR(BUFMRCE)用于將時鐘域傳輸功能擴展到上面和下面的(above and below)時鐘區(qū)域。當MMCM/PLL不能使用或不可用于分頻功能時,需要與源同步I/O用例無關(guān)的分頻時鐘的某些類型的應(yīng)用程序可以將BUFR用作簡單的時鐘分頻器。在這種情況下,必須特別注意時序和偏移,因為這不是BUFR的主要目的。有關(guān)選擇資源計時的更多信息,請參閱UG471,7系列FPGA SelectIO資源用戶指南。

水平時鐘緩沖器BUFH(BUFHCE)嚴格來說是一個區(qū)域資源,不能跨越上面或下面的時鐘區(qū)域。與BUFR不同,BUFH沒有分頻時鐘的能力。

BUFHs類似于全球時鐘資源,只是在區(qū)域基礎(chǔ)上跨越兩個水平區(qū)域。

BUFHs能夠作為MMCM/PLL的反饋,時鐘插入延遲可以得到補償。

當接口或邏輯云位于一個時鐘區(qū)域或兩個水平相鄰的時鐘區(qū)域時,BUFHs是首選的時鐘資源。

BUFH還具有時鐘使能引腳(BUFHCE),當邏輯或接口及其相關(guān)邏輯未激活時,可使用該引腳降低動態(tài)功耗。

時鐘使能功能可在時鐘周期的基礎(chǔ)上提供門控時鐘。

與全局時鐘樹類似,BUFH還可以連接到CLB(enable/reset)中的非時鐘資源,具有更好的偏移特性。

BUFH也可用于同步啟動時鐘區(qū)域中時鐘元件。

2.時鐘輸入規(guī)則

外部用戶時鐘必須通過稱為clock-capable(CC)輸入的差分時鐘管腳對引入FPGA。時鐘輸入管腳支持對內(nèi)部全局和區(qū)域時鐘資源的專用高速訪問。時鐘輸入管腳使用專用路由,必須用于時鐘輸入,以保證各種時鐘的時序特征。使用本地互聯(lián)的一般目的I/O不應(yīng)用于時鐘信號。

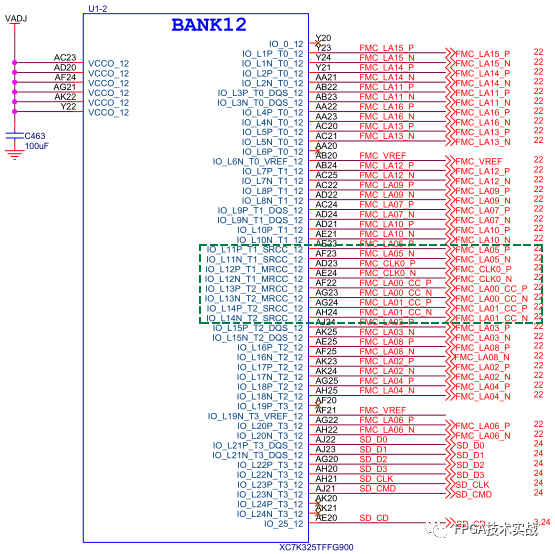

圖2、_CC時鐘管腳連接每個I/O Bank位于一個時鐘區(qū)域,包括50個I/O引腳。在每個I/O bank中每個I/O組中的50個I/O管腳中,有4個支持時鐘的輸入管腳對(共8個管腳)。每個時鐘輸入:

可連接到PCB上的差分或單端時鐘

可為任何I/O標準配置,包括差分I/O標準

有一個P-side(主)和一個N-side(從)

如果單端時鐘連接到差分時鐘管腳對的P側(cè),則N側(cè)不能用作另一個單端時鐘管腳,它只能用作用戶I/O。時鐘輸入管腳在每個I/O Bank中有2個MRCCs和2個SRCCs對。SRCC訪問單個時鐘區(qū)域和全局時鐘樹,以及同一列中上下的其他CMTs。SRCC可以驅(qū)動:

同一時鐘區(qū)域內(nèi)的區(qū)域時鐘線(BUFR、BUFH、BUFIO)。

同一時鐘區(qū)域和相鄰時鐘區(qū)域的CMT。

位于器件的上/下半部分的全局時鐘線(BUFG)。

MRCCs可以訪問多個時鐘區(qū)域和全局時鐘樹。MRCCs的功能與SRCCs相同,還可以驅(qū)動多時鐘區(qū)域緩沖器(BUFMR)來訪問多達三個時鐘區(qū)域。如果不用作時鐘,時鐘輸入管腳可以用作常規(guī)I/O。當用作常規(guī)I/O時,支持時鐘的輸入引腳可以配置為任何單端或差分I/O標準。時鐘輸入管腳可以連接到同一時鐘區(qū)域的CMT,和該時鐘區(qū)域的上下的CMT,但具有一定的限制。

2.1 單個時鐘驅(qū)動單個CMT

當時鐘輸入驅(qū)動單個CMT時,時鐘輸入管腳和CMT(MMCM/PLL)必須在同一時鐘區(qū)域。

2.2 單個時鐘驅(qū)動多個CMTs

一個時鐘輸入可以驅(qū)動同一列中的其他CMT。在這種情況下,一個MMCM/PLL必須被放置在與時鐘輸入管腳相同的時鐘區(qū)域中。在相鄰區(qū)域放置附加的CMT是更為優(yōu)化的,但是在同一列中,可以驅(qū)動比一個CMT更遠的CMT。CMT中使用的資源必須相同,才能自動放置此配置而不使用CLOCK_DEDICATED_ROUTE約束。如果需要混合MMCMs/PLL,則應(yīng)首先將其置于同一CMT中。如果有必要從不在同一時鐘區(qū)域的時鐘輸入管腳驅(qū)動CMT,并且在與時鐘輸入管腳相同的時鐘區(qū)域中沒有MMCM/PLL,則必須設(shè)置屬性CLOCK_DEDICATED_ROUTE = BACKBONE。在這種情況下,MMCM或PLL不能正確地將輸出與輸入時鐘對齊,即存在時鐘偏移。在同一列中專用資源驅(qū)動CMT是有限制的。一些Xilinx IP使用這些資源,從而使它們不可用于其他設(shè)計用途,并導致設(shè)計無法布線。如果到其他時鐘區(qū)域的專用路由不可用,則將CLOCK_DEDICATED_ROUTE設(shè)置為FALSE將允許使用本地互連邏輯,盡管這會導致更長的無補償延遲。如果由普通的IO管腳驅(qū)動全局時鐘資源,比如BUFG或者MMCM,則CLOCK_DEDICATED_ROUTE = FALSE。

2.3 時鐘輸入管腳放置規(guī)則

在創(chuàng)建初始設(shè)計之前,手動選擇支持時鐘的輸入引腳時,有兩個主要考慮因素:

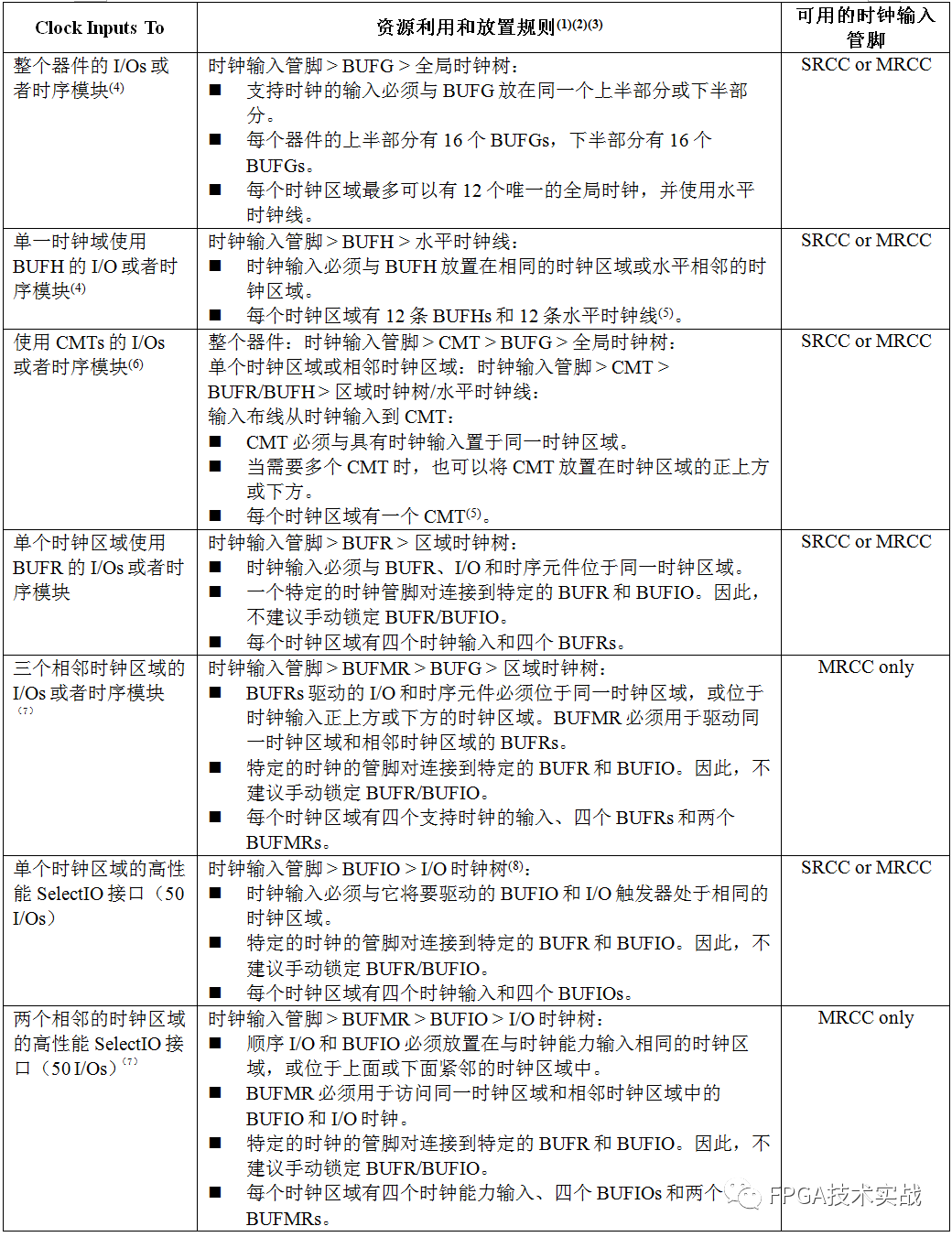

確保支持時鐘輸入可以連接到所需的時鐘資源。表所示的布局規(guī)則確保連通性。

確保所需的時鐘資源是可用的,并且沒有被設(shè)計的另一部分使用。確保通過時鐘輸入管腳進入的外部時鐘和來自IP的內(nèi)部生成時鐘不會在訪問內(nèi)部時鐘網(wǎng)絡(luò)時發(fā)生沖突,最好的方法是構(gòu)建包含所需時鐘網(wǎng)絡(luò)和IP的初始設(shè)計,并通過實現(xiàn)工具運行它。這大大增加了檢查和信心,即引腳不需要由于時鐘原因而改變。

遵循表2-1所示的放置規(guī)則,以確保具有時鐘輸入引腳選擇能夠訪問所需的內(nèi)部時鐘網(wǎng)絡(luò)。每個I/O Bank位于在一個時鐘區(qū)域中。注:通過確保正確選擇具有時鐘輸入引腳的位置,避免昂貴的電路板重新設(shè)計和差的時鐘時序。

表1、時鐘輸入放置規(guī)則在相同的封裝器件之間遷移時,將BUFG組織為16個top和16個bottom資源的上/下中心線可能相對于其他列發(fā)生了移動。具體地說,I/O列會更改與頂部/底部BUFGs的對齊方式。這會導致訪問BUFG的時鐘輸入引腳的不同對齊方式。圖1顯示了使用XC7K325T和XC7K160T器件的中心對齊示例。在這種情況下,當從相同封裝中的大器件移動到小器件時,中心線較低(相對于I/O列),或者從小器件移動到大器件時,中心線更高。如果時鐘輸入引腳被定位,設(shè)計可以是不可布線的。

圖3、使用XC7K325T和XC7K160T器件的中心對齊示例當遷移到相同封裝的一個較小的器件時,也可能會出現(xiàn)這樣的情況:較大器件的南側(cè)的所有BUFG都已被利用,而沒有更多的BUFG可用。見UG475:7系列FPGA封裝和引腳輸出規(guī)范,用于BUFG和I/O組對準。另外,具有多個超級邏輯區(qū)域(SLR)的器件在同一個包中從單個SLR中的單片路徑遷移時可能具有類似的限制。

原文標題:Xilinx 7系列FPGA架構(gòu)之時鐘資源(二)

文章出處:【微信公眾號:FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

責任編輯:haq

-

FPGA

+關(guān)注

關(guān)注

1662文章

22480瀏覽量

638438 -

Xilinx

+關(guān)注

關(guān)注

73文章

2205瀏覽量

131735 -

時鐘

+關(guān)注

關(guān)注

11文章

1998瀏覽量

135193

原文標題:Xilinx 7系列FPGA架構(gòu)之時鐘資源(二)

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

Xilinx FPGA中的混合模式時鐘管理器MMCME2_ADV詳解

Altera Agilex FPGA與SoC實現(xiàn)更智能的AI

淺談FPGA的時鐘輸入要求

Xilinx FPGA輸入延遲原語介紹

XC7Z020-2CLG484I 雙核異構(gòu)架構(gòu) 全能型 SoC

Xilinx FPGA中IDELAYCTRL參考時鐘控制模塊的使用

AMD UltraScale架構(gòu):高性能FPGA與SoC的技術(shù)剖析

使用Xilinx 7系列FPGA的四位乘法器設(shè)計

Xilinx FPGA串行通信協(xié)議介紹

請問如何將蜂鳥E203移植到Xilinx NEXYS A7 FPGA 開發(fā)板上?

【VPX650 】青翼凌云科技基于 VPX 系統(tǒng)架構(gòu)的 VU13P FPGA+ZYNQ SOC 超寬帶信號處理平臺

一文詳解xilinx 7系列FPGA配置技巧

Zynq-7000 SoC與7系列設(shè)備內(nèi)存接口解決方案數(shù)據(jù)手冊

正點原子AU15開發(fā)板資料發(fā)布!板載40G QSFP、PCIe3.0x8和FMC LPC等接口,性能強悍!

Xilinx Ultrascale系列FPGA的時鐘資源與架構(gòu)解析

Xilinx 7系列中FPGA架構(gòu)豐富的時鐘資源介紹

Xilinx 7系列中FPGA架構(gòu)豐富的時鐘資源介紹

評論