賽靈思在其FPGA中提供了豐富的時鐘資源,大多數設計人員在他們的FPGA設計中或多或少都會用到。不過對FPGA設計新手來說,什么時候用DCM、PLL、PMCD和MMCM四大類型中的哪一種,讓他們頗為困惑。本文為您解惑......

2013-07-23 09:25:53 20763

20763

針對不同類型的器件,Xilinx公司提供的全局時鐘網絡在數量、性能等方面略有區別,下面以Virtex-4系列芯片為例,簡單介紹FPGA全局時鐘網絡結構。

2013-11-28 18:49:00 14294

14294

介紹3種跨時鐘域處理的方法,這3種方法可以說是FPGA界最常用也最實用的方法,這三種方法包含了單bit和多bit數據的跨時鐘域處理,學會這3招之后,對于FPGA相關的跨時鐘域數據處理便可以手到擒來。 本文介紹的3種方法跨時鐘域處理方法如下:

2020-11-21 11:13:01 4997

4997

01、如何決定FPGA中需要什么樣的時鐘速率 設計中最快的時鐘將確定 FPGA 必須能處理的時鐘速率。最快時鐘速率由設計中兩個觸發器之間一個信號的傳輸時間 P 來決定,如果 P 大于時鐘周期 T,則

2020-11-23 13:08:24 4644

4644

7系列FPGA擁有豐富的時鐘資源。各種緩沖器類型、時鐘輸入管腳和時鐘連接,可以滿足許多不同的應用需求。選擇合適的時鐘資源可以改善布線、性能和一般FPGA資源利用率。BUFGCTRL(最常用作BUFG

2022-07-22 09:40:25 3922

3922 當我剛開始我的FPGA設計生涯時,我對明顯更小、更不靈活的 FPGA(想想 XC4000XL / Clcyone3/4和 Spartan)和工具的非常簡單的時鐘規則之一是盡可能只使用單個時鐘。當然,這并不總是可能的,但即便如此,時鐘的數量仍然有限。

2022-09-30 08:49:26 2145

2145 “全局時鐘和第二全局時鐘資源”是FPGA同步設計的一個重要概念。合理利用該資源可以改善設計的綜合和實現效果;如果使用不當,不但會影響設計的工作頻率和穩定性等,甚至會導致設計的綜合、實現過程出錯

2023-07-24 11:07:04 1443

1443

通過上一篇文章“時鐘管理技術”,我們了解Xilinx 7系列FPGA主要有全局時鐘、區域時鐘、時鐘管理塊(CMT)。 通過以上時鐘資源的結合,Xilinx 7系列FPGA可實現高性能和可靠的時鐘分配

2023-08-31 10:44:31 4432

4432

本文主要介紹Xilinx FPGA的GTx的參考時鐘。下面就從參考時鐘的模式、參考時鐘的選擇等方面進行介紹。

2023-09-15 09:14:26 5117

5117

生成時鐘包括自動生成時鐘(又稱為自動衍生時鐘)和用戶生成時鐘。自動生成時鐘通常由PLL或MMCM生成,也可以由具有分頻功能的時鐘緩沖器生成如7系列FPGA中的BUFR、UltraScale系列

2024-01-11 09:50:09 3808

3808

工作,由于配置時間很短,不會影響系統正常工作。也有少數FPGA采用反熔絲或Flash工藝,對這種FPGA,就不需要外加專用的配置芯片。

四、其他類型的FPGA和PLD

隨著技術的發展,在

2023-11-03 11:18:38

歡迎。經過了十幾年的發展,許多公司都開發出了多種可編程邏輯器件。比較典型的就是 Altera 公司和Xilinx 公司的 CPLD 器件系列和 FPGA 器件系列,它們開發較早,占用了較大的 PLD

2009-03-28 14:57:08

PLD是小規模集成電路,主要是替代TTL集成電路的可編程邏輯電路FPGA 是大規模集成電路,它是在PLD、PAL、GAL 、CPLD等可編程器件的基礎上進一步發展而成的。或者說是經過了幾代的升級產品

2018-08-28 09:15:53

FPGA設計重利用方法(Design Reuse Methodology)SRAM工藝FPGA的加密技術大規模FPGA設計中的多點綜合技術定點乘法器設計(中文)你的PLD是亞穩態嗎_設計異步多時鐘系統的綜合以及描述技巧使用retiming提高FPGA性能

2014-04-30 23:57:42

1.PLD/FPGA/CPLDPLD(Programmable Logic Device):可編程邏輯器件,數字集成電路半成品,芯片上按照一定的排列方式集成了大量的門和觸發器等基本邏輯元件,使用者

2021-07-30 07:26:19

PLD,CPLD,FPGA有何不同?

不同廠家的叫法不盡相同,PLD(Programmable Logic Device)是可編程邏輯器件的總稱,FPGA (Field Programmable

2024-04-12 16:58:35

`PLD/FPGA的分類和使用 在PLD/FPGA開發軟件中完成設計以后,軟件會產生一個最終的編程文件(如 .pof )。如何將編程文件燒到PLD芯片中去呢? 1.對于基于乘積項

2012-02-27 10:42:53

PLD是可編程邏輯器件(Programable Logic Device)的簡稱,FPGA是現場可編程門陣列(Field Programable Gate Array)的簡稱,兩者的功能基本相

2009-06-20 10:38:05

,足以滿足設計一般的數字系統的需要。目前常用EEPROM,CPLD,FPGA。 PLA,PAL,GAL是早期的可編程器件,已經淘汰。可編程邏輯器件PLD(Programmable Logic Dev...

2021-07-22 09:05:48

作者:張宇清可編程邏輯器件(PLD)的兩種主要類型是現場可編程門陣列(FPGA)和復雜可編程邏輯器件(CPLD)。根據半導體行業協會提供的數據,PLD現在是半導體行業中增長最快的領域之一,高性能

2019-07-29 08:07:20

可編程邏輯器件(PLD)的兩種主要類型是現場可編程門陣列(FPGA)和復雜可編程邏輯器件(CPLD)。根據半導體行業協會提供的數據,PLD現在是半導體行業中增長最快的領域之一,高性能PLD現在已經從

2019-07-17 07:19:16

可編程邏輯器件(PLD)的兩種主要類型是現場可編程門陣列(FPGA)和復雜可編程邏輯器件(CPLD)。根據半導體行業協會提供的數據,PLD現在是半導體行業中增長最快的領域之一,高性能PLD現在已經從

2019-07-22 06:51:56

網友們好象沒人提過PLD的話題,我感覺是對這個東西不太熟,其實PLD是大有用武之地的,其優勢在于:1、可以很靈活的實現各種“與、或、非”邏輯功能;2、任何復雜的邏輯運算都是一步完成,避免產生額外

2012-11-19 20:41:23

很大。 在設計PLD/FPGA時通常采用幾種時鐘類型。時鐘可分為如下四種類型:全局時鐘、門控時鐘、多級邏輯時鐘和波動式時鐘。多時鐘系統能夠包括上述四種時鐘類型的任意組合。1.全局時鐘對于一個設計項目

2012-12-14 16:02:37

.其他類型的FPGA和PLD 隨著技術的發展,在2004年以后,一些廠家推出了一些新的PLD和FPGA,這些產品模糊了PLD和FPGA的區別。例如Altera

2008-05-20 09:46:10

單片機的開發過程是怎樣的?常用的單片機類型有哪些?

2021-09-27 06:12:32

請問PCBA基板有哪些常用的類型有哪些?

2020-03-13 15:38:59

/FPGA產品60%以上是由Altera和Xilinx提供的。可以講Altera和Xilinx共同決定了PLD技術的發展方向。當然還有許多其它類型器件,如:Lattice,Vantis,Actel

2012-02-27 11:52:00

從FPGA或PLD轉換到門陣會遇到哪些時序問題?如何去避免這些問題的發生?

2021-04-30 06:54:18

,什么時候用DCM、PLL、PMCD和MMCM四大類型中的哪一種,讓他們頗為困惑。賽靈思現有的FPGA中沒有一款同時包含這四種資源(見表1)。 這四大類中的每一種都針對特定的應用。例如,數字時鐘管理器

2020-04-25 07:00:00

)兩類功能,瞬時邏輯主要是指與、或、非及其混合運算,輸出結果對輸入條件能即時響應;延時邏輯一般由時鐘信號驅動,主要實現寄存器、計數器以及與十序有關的邏輯功能。 最簡單的PLD器件一般有8個專用輸入端和8

2012-10-30 23:39:54

在分析電路時常用的定理有哪些

2021-03-11 06:33:09

作者:Altera公司 Tam Do

從便攜媒體播放器和手機,到視頻游戲控制臺,消費類視頻應用的迅速增長需要大量不同的接口和適配器,以使用戶在其電腦和各種娛樂信息設備間相互傳輸視頻數據。

常用

2018-12-28 07:00:06

的進化。之后,SPLD、CPLD和FPGA在20世紀80年代早期發展起來。表9.2 PLD分類PLD分類如表9.2所示。以下是用于理解現場可編程設備的關鍵術語。PAL是一種密度相對較小的現場可編程

2022-10-27 16:43:59

可編程邏輯器件(PLD)的兩種主要類型是現場可編程門陣列(FPGA)和復雜可編程邏輯器件(CPLD)。根據半導體行業協會提供的數據,PLD現在是半導體行業中增長最快的領域之一,高性能PLD現在已經從

2019-09-24 06:58:39

把握DCM、PLL、PMCD和MMCM知識是穩健可靠的時鐘設計策略的基礎。賽靈思在其FPGA中提供了豐富的時鐘資源,大多數設計人員在他們的FPGA設計中或多或少都會用到。不過對FPGA設計新手來說,什么時候用DCM、PLL、PMCD和MMCM四大類型中的哪一種,讓他們頗為困惑。

2019-09-18 08:26:21

什么叫電源?電源有哪些分類?常用的電源類型?

2021-03-16 14:40:58

請問一下平時在工程設計中Xilinx的FPGA常用,還是使用Altera的FPGA 常用?

2021-06-23 06:30:20

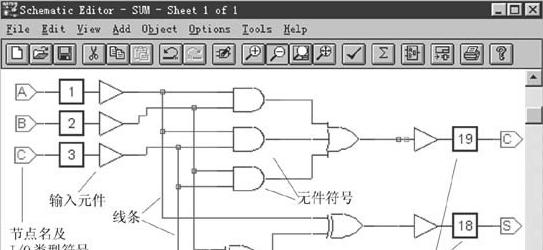

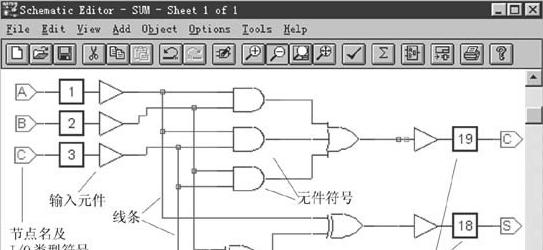

Multiple Clock System Design PLD設計技巧—多時鐘系統設計

Information Missing

Max+Plus II does

2008-09-11 09:19:41 25

25 用單片機配置FPGA—PLD設計技巧

Configuration/Program Method for Altera Device

Configure the FLEX Device

You

2008-09-11 09:36:56 23

23 基于PLD及FPGA的頻率與相位測量系統設計與實現:摘 要:本測量系統由頻率相位測量儀和DDS 雙路移相信號發生器兩部分組成。頻率相位測量由Altera EPM7128S84 CPLD 完成,雙路移相信號

2009-09-25 15:50:03 31

31 DLL在FPGA時鐘設計中的應用:在ISE集成開發環境中,用硬件描述語言對FPGA 的內部資源DLL等直接例化,實現其消除時鐘的相位偏差、倍頻和分頻的功能。時鐘電路是FPGA開發板設計中的

2009-11-01 15:10:30 33

33 FPGA,CPLD和其它類型PLD的結構各有其特點和長處,但概括起來,它們是由三大部分組成的:(1)一個二維的邏輯塊陣列,構成了PLD器件的邏輯組成核心;(2)輸入/輸出塊;(3)連

2009-12-02 15:19:40 24

24 本文闡述了用于FPGA的可優化時鐘分配網絡功耗與面積的時鐘布線結構模型。并在時鐘分配網絡中引入數字延遲鎖相環減少時鐘偏差,探討了FPGA時鐘網絡中鎖相環的實現方案。

2010-08-06 16:08:45 12

12 PLD/FPGA新手入門知識

PLD是可編程邏輯器件(Programable Logic Device)的簡稱,FPGA是現場可編程門陣列(Field Programable Gate Array)的簡稱,兩者的功能基本相

2009-06-20 10:31:05 1427

1427

什么是PLD(可編程邏輯器件)

PLD是可編程邏輯器件(Programable Logic Device)的簡稱,FPGA是現場可編程門陣列(Field Programable Gate Array)

2009-06-20 10:32:32 29733

29733

大型設計中FPGA的多時鐘設計策略

利用FPGA實現大型設計時,可能需要FPGA具有以多個時鐘運行的多重數據通路,這種多時鐘FPGA設計必須特別小心,需要注意最大時鐘速率

2009-12-27 13:28:04 827

827

理解不同類型的時鐘抖動

抖動定義為信號距離其理想位置的偏離。本文將重點研究時鐘抖動,并探討下面幾種類型的時鐘抖動:相鄰周期抖動、周期抖動、時間間隔誤

2010-01-06 11:48:11 2094

2094

PLD設計方法及步驟 1、PLD器件的設計步驟

1.電路邏輯功能描述

PLD器件的邏輯功能描述一

2010-09-18 09:08:30 5109

5109

在FPGA設計中,為了成功地操作,可靠的時鐘是非常關鍵的。設計不良的時鐘在極限的溫度、電壓下將導致錯誤的行為。在設計PLD/FPGA時通常采用如下四種類型時鐘:全局時鐘、門控時鐘

2011-09-21 18:38:58 4131

4131

PLD、FPGA優秀設計的十條戒律, 該文淺顯易懂的介紹了一個優秀設計必須考慮的問題,給出了設計方法和建議。仔細閱讀和消化本文,對提高PLD/FPGA設計水平大有裨益

2012-01-17 10:32:59 61

61 利用FPGA實現大型設計時,可能需要FPGA具有以多個時鐘運行的多重數據通路,這種多時鐘FPGA設計必須特別小心,需要注意最大時鐘速率、抖動、最大時鐘數、異步時鐘設計和時鐘/數

2012-05-21 11:26:10 1591

1591

用 VHDL /VerilogHD語言開發PLD/ FPGA 的完整流程為: 1.文本編輯:用任何文本編輯器都可以進行,也可以用專用的HDL編輯環境。通常VHDL文件保存為.vhd文件,Verilog文件保存為.v文件 2.功能仿真

2012-05-21 12:58:06 1687

1687 電子發燒友網整理: 本文主要描述可編程邏輯器件的類型及其優點,希望能給初學者們一點幫助。可編程邏輯器件的英文全稱為:programmable logic device 即PLD。PLD是做為一種通用集成電路

2012-06-08 11:14:11 6279

6279 。PLD可分為簡單PLD和復雜PLD,其中復雜PLD又包括CPLD和FPGA。在本專題我們將主要介紹CPLD和FPGA的相關技術知識。

2012-06-16 22:13:38

DLL在_FPGA時鐘設計中的應用,主要說明DLL的原理,在Xilinx FPGA中是怎么實現的。

2015-10-28 14:25:42 1

1 HL配套C實驗例程100例之定時器定時常用參數,配合開發板學習效果更好。

2016-04-11 16:09:41 3

3 常用的FPGA代碼,VHDL語言編寫。需要請下載

2016-05-26 11:36:16 16

16 基于FPGA的數字時鐘設計,可實現鬧鐘的功能,可校時。

2016-06-23 17:15:59 71

71 如何正確使用FPGA的時鐘資源

2017-01-18 20:39:13 22

22 PLD(Programmable Logic Device)是可編程邏輯器件的總稱。早期的PLD多屬于EEPROM或乘積項(Product Term)結構。FPGA(Field

2017-06-19 09:59:13 5942

5942 介紹3種跨時鐘域處理的方法,這3種方法可以說是FPGA界最常用也最實用的方法,這三種方法包含了單bit和多bit數據的跨時鐘域處理,學會這3招之后,對于FPGA相關的跨時鐘域數據處理便可以手到擒來。 本文介紹的3種方法跨時鐘域處理方法如下:打兩拍;異步雙口RAM;格雷碼轉換。

2017-11-15 20:08:11 14725

14725 PLD/FPGA 常用開發軟件maxplus2crack。 Altera公司的免費PLD開發軟件Altera公司的免費PLD開發軟件,界面與標準版的MaxplusII完全一樣,只支持MAX7000

2017-11-26 11:19:26 6

6 PLD/FPGA 常用開發軟件System Generator 9.10。 業內領先的高級系統級FPGA開發高度并行系統。

2017-11-26 11:34:56 14

14 PLD介紹 可編程邏輯器件PLD(Programable Logic Device)是允許用戶編程(配置)實現所需邏輯功能的電路, 它與分立元件相比,具有速度快、容量大、功耗小和可靠性高等優點。由于

2017-12-05 10:45:28 21

21 時鐘是FPGA設計中最重要的信號,FPGA系統內大部分器件的動作都是在時鐘的上升沿或者下降沿進行。

2019-09-20 15:10:18 6055

6055

時鐘網絡反映了時鐘從時鐘引腳進入FPGA后在FPGA內部的傳播路徑。 報告時鐘網絡命令可以從以下位置運行: A,VivadoIDE中的Flow Navigator; B,Tcl命令

2020-11-29 09:41:00 3695

3695 跨時鐘域處理的方法,這三種方法可以說是 FPGA 界最常用也最實用的方法,這三種方法包含了單 bit 和多 bit 數據的跨時鐘域處理,學會這三招之后,對于 FPGA 相關的跨時鐘域數據處理便可以手到擒來。 這里介紹的三種方法跨時鐘域處理方法如下: 打兩

2022-12-05 16:41:28 2398

2398 區域(Region):每個FPGA器件被分為多個區域,不同的型號的器件區域數量不同。

FPGA時鐘資源主要有三大類:時鐘管理模、時鐘IO、時鐘布線資源。

時鐘管理模塊:不同廠家及型號的FPGA中

2020-12-09 14:49:03 21

21 是最佳的,然后通過使用適當的I/O和時鐘緩沖器來訪問這些時鐘路由資源。該章節包括: 時鐘緩沖選擇考慮 時鐘輸入管腳 1.時鐘緩沖器選擇考慮 7系列FPGA擁有豐富的時鐘資源。各種緩沖器類型、時鐘輸入管腳和時鐘連接,可以滿足許多不同的應用需求

2021-03-22 10:16:18 6115

6115

引言:從本文開始,我們陸續介紹Xilinx 7系列FPGA的時鐘資源架構,熟練掌握時鐘資源對于FPGA硬件設計工程師及軟件設計工程師都非常重要。本章概述7系列FPGA時鐘,比較了7系列FPGA時鐘

2021-03-22 10:25:27 6070

6070 常用OP電路的類型介紹。

2021-05-31 10:46:38 24

24 編程數據存儲單元以陣列形式分布在FPGA中,一般把所有超過某一集成度PLD器件都稱為CPLD。 編程數據流由開發軟件自動生成,數據以串行方式移入移位寄存器圍繞一個可編程互連矩陣構成,對于可編程邏輯器件PLD能完成任何數字器件的功能。

2021-10-01 09:17:00 8125

8125 減少很多與多時鐘域有關的問題,但是由于FPGA外各種系統限制,只使用一個時鐘常常又不現實。FPGA時常需要在兩個不同時鐘頻率系統之間交換數據,在系統之間通過多I/O接口接收和發送數據,處理異步信號,以及為帶門控時鐘的低功耗

2021-09-23 16:39:54 3632

3632 (08)FPGA時鐘概念1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA時鐘概念5)結語1.2 FPGA簡介FPGA(Field Programmable Gate

2021-12-29 19:41:17 2

2 (12)FPGA時鐘設計原則1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA時鐘設計原則5)結語1.2 FPGA簡介FPGA(Field Programmable

2021-12-29 19:41:27 17

17 (29)FPGA原語設計(差分時鐘轉單端時鐘)1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA原語設計(差分時鐘轉單端時鐘)5)結語1.2 FPGA簡介FPGA

2021-12-29 19:41:38 5

5 (30)FPGA原語設計(單端時鐘轉差分時鐘)1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA原語設計(單端時鐘轉差分時鐘)5)結語1.2 FPGA簡介FPGA

2021-12-29 19:41:48 10

10 ?xilinx 的 FPGA 時鐘結構,7 系列 FPGA 的時鐘結構和前面幾個系列的時鐘結構有了很大的區別,7系列的時鐘結構如下圖所示。

2022-07-03 17:13:48 4699

4699 今天浩道跟大家分享硬核網絡故障排錯干貨,主要針對網絡丟包時常用的排錯思路。讓你遇到網絡丟包時,不再迷茫!

2022-10-24 09:20:47 2607

2607 ASIC 和FPGA芯片的內核之間最大的不同莫過于時鐘結構。ASIC設計需要采用諸如時鐘樹綜合、時鐘延遲匹配等方式對整個時鐘結構進行處理,但是 FPGA設計則完全不必。

2022-11-23 16:50:49 1249

1249

PLD(Programmable Logic Device)是一種由用戶根據需要而自行構造邏輯功能的數字集成電路。目前主要有兩大類型:CPLD(Complex PLD)和FPGA(Field Programmable Gate Array)。

2023-04-29 16:46:00 2255

2255 常用直線模組的類型

2023-07-29 17:45:32 2278

2278

減少很多與多時鐘域有關的問題,但是由于FPGA外各種系統限制,只使用一個時鐘常常又不現實。FPGA時常需要在兩個不同時鐘頻率系統之間交換數據,在系統之間通過多I/O接口接收和發送數據,處理異步信號,以及為帶門控時鐘的低功耗

2023-08-23 16:10:01 1372

1372 FPGA為什么有時候還需要一個時鐘配置芯片提供時鐘呢? FPGA(Field Programmable Gate Array)是一種可編程邏輯器件,可以根據不同需要編程,實現不同的功能。在FPGA中

2023-10-25 15:14:20 2400

2400 FPGA輸入的時鐘信號必須是方波么?正弦波會有影響么? FPGA是一種可編程邏輯器件,通常用于實現數字電路。輸入時鐘信號是FPGA中非常重要的時序信號,對整個系統的穩定性和性能都有很大影響。在

2024-01-31 11:31:42 5410

5410 FPGA 中包含一些全局時鐘資源。以AMD公司近年的主流FPGA為例,這些時鐘資源由CMT(時鐘管理器)產生,包括DCM、PLL和MMCM等。

2024-04-25 12:58:30 3304

3304

在FPGA(現場可編程門陣列)設計中,消除時鐘抖動是一個關鍵任務,因為時鐘抖動會直接影響系統的時序性能、穩定性和可靠性。以下將詳細闡述FPGA中消除時鐘抖動的多種方法,這些方法涵蓋了從硬件設計到軟件優化的各個方面。

2024-08-19 17:58:54 3753

3753 PLD的定義和應用 一、PLD的定義 PLD(Programmable Logic Device)即可編程邏輯器件,是一種能夠根據用戶的需求和設計規格,通過內部的可編程連接和邏輯門陣列,靈活地組合

2025-02-01 10:35:00 6636

6636 功能,包括邏輯運算、數據存儲、輸入輸出控制等。 性能要求 :了解應用對PLD的時鐘速度、邏輯資源、I/O接口數量、功耗等方面的具體要求。 封裝要求 :根據應用場景,選擇合適的封裝類型,如DIP、SOP、QFP等,以及相應的體積和引腳間距。 二、

2025-01-20 09:40:55 1047

1047 (Design Planning) 選擇PLD類型 :根據需求選擇合適的PLD類型,如FPGA、CPLD等。 資源評估 :評估所需的邏輯資源、

2025-01-20 09:46:33 1979

1979 1. 理解PLD的基本概念 PLD的定義 :PLD是一種可以通過編程來配置的集成電路,用于實現特定的數字邏輯功能。 PLD的類型 :包括FPGA(Field-Programmable Gate

2025-01-20 09:48:06 1586

1586 FPGA是什么?了解FPGA應用領域、差分晶振在FPGA中的作用、常用頻率、典型案例及FCom差分振蕩器解決方案,為高速通信、數據中心、工業控制提供高性能時鐘支持。

2025-03-24 13:03:01 3041

3041

電子發燒友App

電子發燒友App

評論