FPGA?是什么

FPGA(Field Programmable Gate Array),現場可編程門陣列,一種半定制的數字集成電路。FPGA 憑借其靈活性高、開發周期短、處理性能強(并行)等特點,廣泛應用于通信、圖像處理、醫療等領域。隨著科技的進步,FPGA 在人工智能、5G 和自動駕駛等領域也有一席之地。

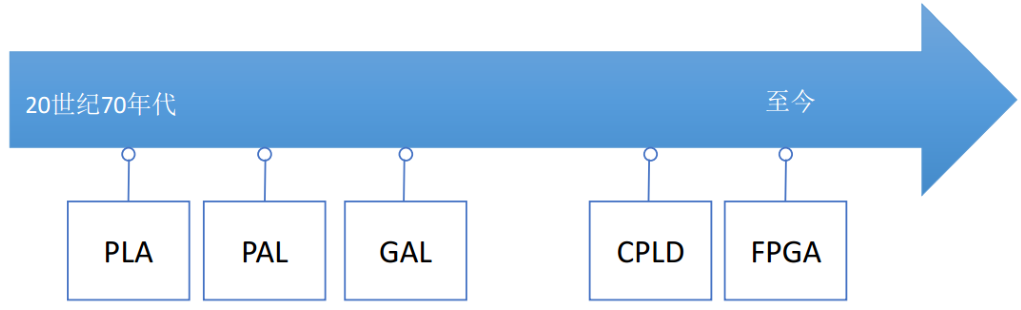

FPGA 它是在 PAL、GAL、CPLD 等可編程器件的基礎上進一步發展的產物。它是 作為專用集成電路(ASIC)領域中的一種半定制電路而出現的,既解決了定制電路的不足,又克服了原有可編程器件門電路個數有限的缺點。

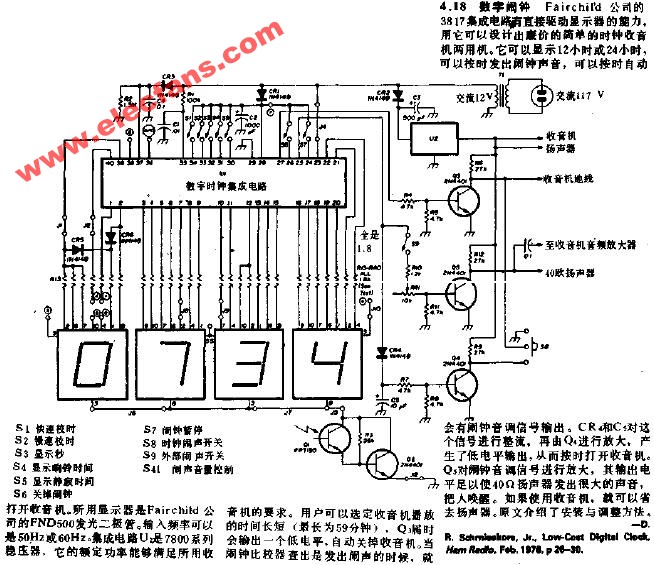

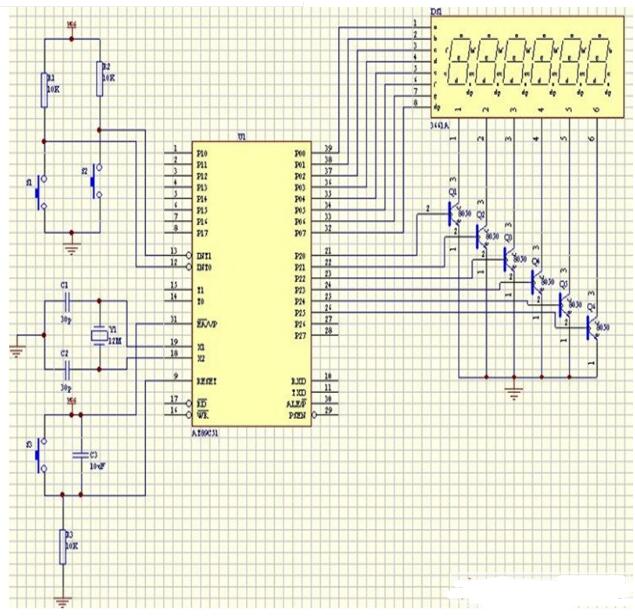

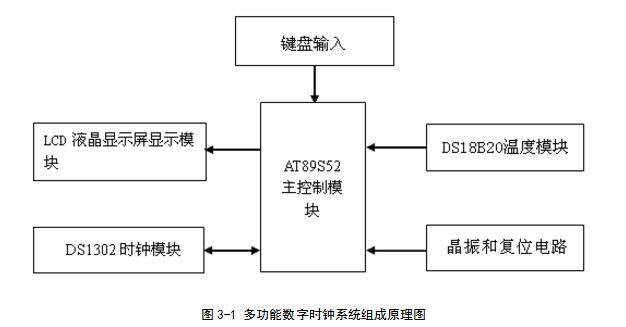

比如用面包板搭建數字時鐘電路;雖然電路是一個數字時鐘,里面有晶振、蜂鳴器、數碼管,以及各種 74 系列的小芯片,這些小芯片能夠實現的功能也就相當于幾個邏輯門,如果你親自動手去搭建它,肯定會知道搭建該電路是非常麻煩的,一根線一根線去連接,不斷對照原理圖,生怕搭錯一根線,搞不好心態就崩了。

這僅僅是搭建一個簡單的數字時鐘就這么多跟線了。如果我們想要實現更加復雜的功能,那么我們就要犯難了,因為我們需要使用幾十個或者上百個這種專用小芯片來完成,這樣就會使得電路板的布局、布線變得困難,還會極大的影響到整個系統的性能,而且搭出來的電路體積龐大,也不美觀,實用性極差,所以這種方式毫無疑問是不行的。

為了改變這種情況,大家就想到了一個辦法,那就是通過專用集成電路(ASIC)來實現,我們可以將要實現的特定需求交給 ASIC 廠商,讓他們設計出一個專用集成電路芯片,這樣就可以解決這種問題了。

比如說,我們把數字時鐘功能要求交給 ASIC 廠商,ASIC 廠商就會根據數字時鐘功能要求設計出一個專用集成電路芯片,這一個小小的芯片它其實就完成了我們數字時鐘電路功能。這種方法雖然很好,但同時也會帶來很多其他的問題,比如說,生成周期長,芯片難驗證,芯片內部電路不可以更改等等問題。于是人們就開始不斷地去探索,看看有沒有什么辦法既能讓我很好的實現功能,又能解決定制電路的不足。

于是 FPGA 應運而生,于 1985 年由 Xilinx 創始人之一 Ross Freeman 發明,屬于可編程邏輯器件 PLD(Programmable Logic Device)的一種。

Xilinx A7 系列 FPGA 芯片

真正意義上的第一顆 FPGA 芯片 XC2064 為 Xilinx 所發明,這個時間差不多比著名的摩爾定律晚 20 年左右,但是 FPGA 一經問世,后續的發展速度之快,超出大多數人的想象。

我們要知道一塊專用的 ASIC 定制集成電路的芯片他在出廠前功能就已經定死了,就拿上面的數字時鐘來舉例,假如我現在拿到一塊全新的數字時鐘芯片,那么我只需要看看廠家給我提供的數據手冊,看看它是怎么操作的,可能僅僅只需要給它通上電然后簡單的配置一下它就能工作了。

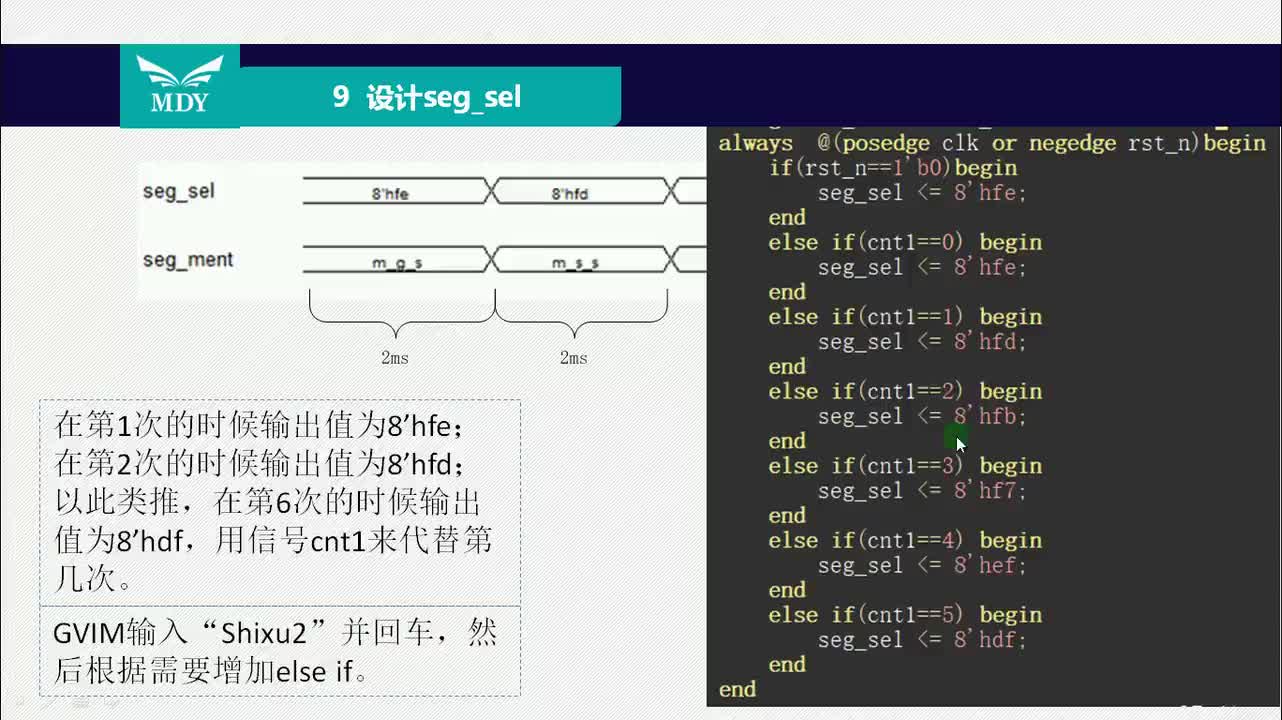

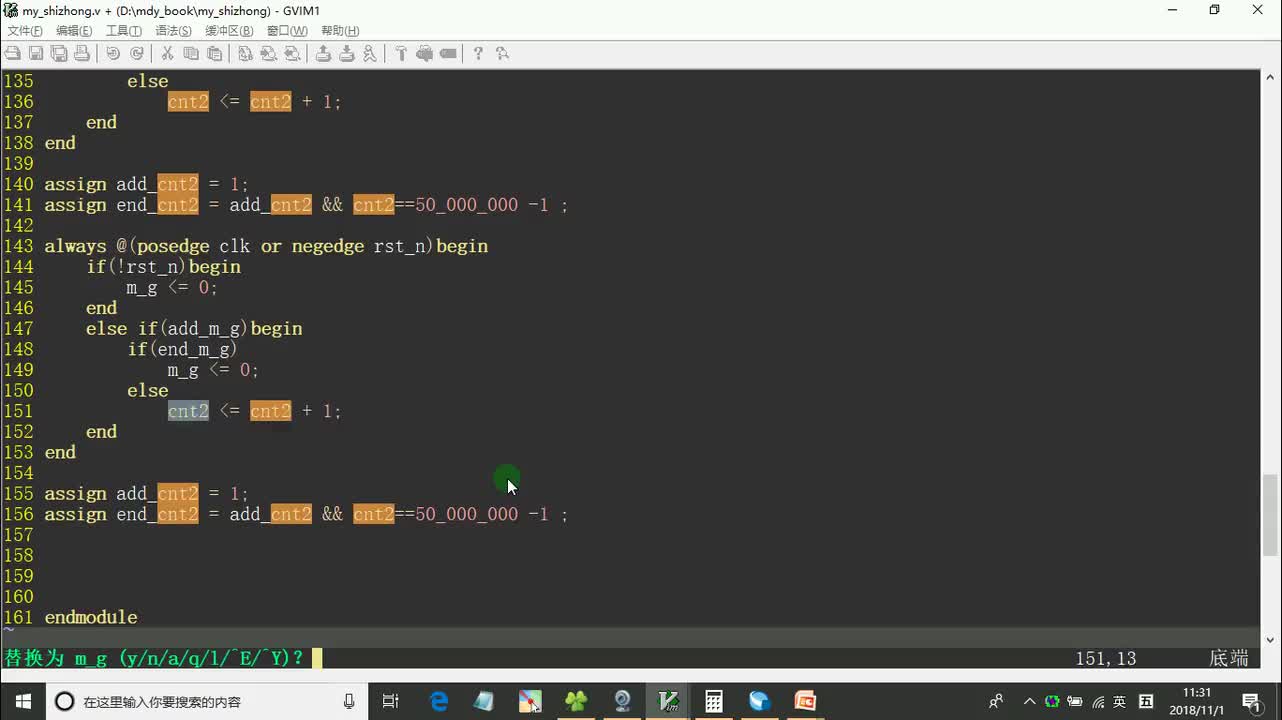

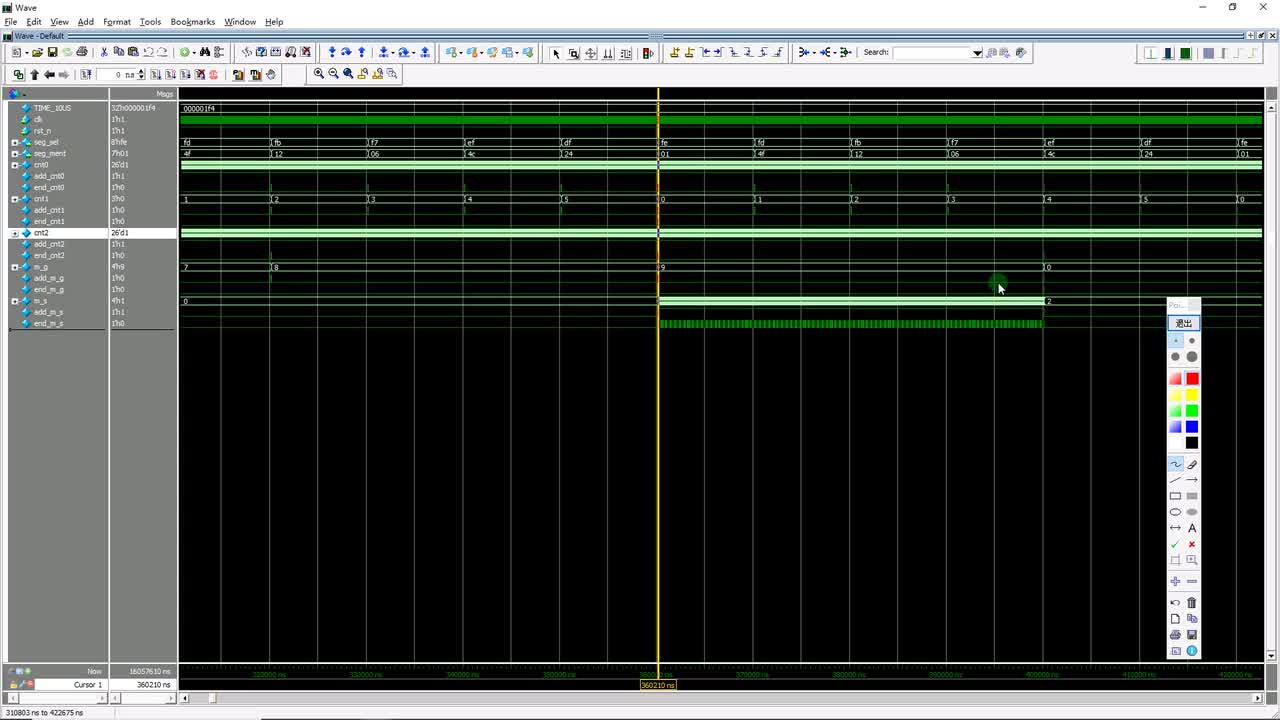

它的功能是不可更改的,就只能跑個數字時鐘,而且它內部電路是啥樣的我也不知道,雖然用起來簡單,但是缺乏靈活性,但 FPGA 就不一樣了,它在出廠的那一刻是不具備任何功能的,可以說就是一張白紙。你可以在這張白紙上肆意創作,你想要它實現數字時鐘的功能沒問題,通過特定的編輯語言,例如 Verilog、VHDL 等硬件描述語言將數字時鐘的邏輯編寫好,下載到 FPGA 內部,它就會生成一個數字時鐘的電路,去完成數字時鐘的功能。當你不想要這個功能了,沒問題你可以隨時將內部程序擦除,或者用一個新的設計去覆蓋原有的設計。理論上我們可以用 FPGA 去生成一個任意我們想要的功能,正是基于這種強大的可編輯能力,FPGA 近年來越來越受到市場的認可,在未來 FPGA 的適用范圍必將越來越廣闊。

FPGA 有什么用

FPGA 所能應用的領域大概可以分成六大類:

1)通信領域

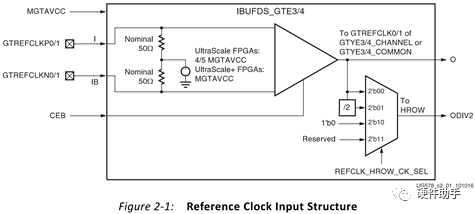

FPGA 在通信領域的應用可以說是無所不能,得益于 FPGA 內部結構的特點,它可以很容易地實現分布式的算法結構,這一點對于實現無線通信中的高速數字信號處理十分有利。因為在無線通信系統中,許多功能模塊通常都需要大量的濾波運算,而這些濾波函數往往需要大量的乘和累加操作。而通過 FPGA 來實現分布式的算術結構,就可以有效地實現這些乘和累加操作。尤其是 Xilinx 公司的 FPGA內部集成了大量的適合通信領域的一些資源比如:基帶處理(通道卡)、接口和連接功能以及 RF(射頻卡)三大類:

(1)基帶處理資源

基帶處理主要包括信道編解碼(LDPC、Turbo、卷積碼以及 RS 碼的編解碼算法)和同步算法的實現(WCDMA 系統小區搜索等)。

(2)接口和連接資源

接口和連接功能主要包括無線基站對外的高速通信接口(PCI Express、以太網 MAC、高速 AD/DA 接口)以及內部相應的背板協議(OBSAI、CPRI、EMIF、LinkPort)的實現。

(3)RF 應用資源

RF 應用主要包括調制/解調、上/下變頻(WiMAX、WCDMA、TD-SCDMA 以及 CDMA2000 系統的單通道、多通道 DDC/DUC)、削峰(PC-CFR)以及預失真(Predistortion)等關鍵技術的實現。

總而言之只要你 FPGA 學的好,在通信領域你絕對可以大展身手。

2)數字信號處理領域

在數字信號處理領域 FPGA 同樣所向披靡,主要是因為它的高速并行處理能力。FPGA 最大優勢是其并行處理機制,即利用并行架構實現數字信號處理的功能。這一并行機制使得 FPGA 特別適合于完成 FIR 等數字濾波這樣重復性的數字信號處理任務,對于高速并行的數字信號處理任務來說,FPGA 性能遠遠超過通用 DSP 處理器的串行執行架構,還有就是它接口的電壓和驅動能力都是可編程配置的不像傳統的 DSP 需要受指令集控制,因為指令集的時鐘周期的限制,不能處理太高速的信號,對于速率級為 Gbps 的 LVDS 之類信號就難以涉及。所以在數字信號處理領域 FPGA 的應用也是十分廣泛的。

3)視頻圖像處理領域

隨著時代的變換,人們對圖像的穩定性、清晰度、亮度和顏色的追求越來越高, 像以前的標清(SD)慢慢演變成高清(HD),到現在人們更是追求藍光品質的圖像。這使得處理芯片需要實時處理的數據量越來越大,并且圖像的壓縮算法也是越來越復雜,使得單純的使用 ASSP 或者 DSP 已經滿足不了如此大的數據處理量了。這時 FPGA 的優勢就凸顯出來了,它可以更加高效的處理數據,所以在圖像處理領域在綜合考慮成本后,FPGA 也越來越受到市場的歡迎。

4)高速接口設計領域

其實看了 FPGA 在通信領域和數字信號處理領域的表現,我想大家也已應該猜 到了在高速接口設計領域,FPGA 必然也是有一席之地的。它的高速處理能力和多達成百上千個的 IO 決定了它在高速接口設計領域的獨特優勢。

比如說我需要和 PC 端做數據交互,將采集到的數據送給 PC 機處理,或者將處理后的結果傳給 PC 機進行顯示。PC 機與外部系統通信的接口比較豐富,如 ISA、PCI、PCI Express、PS/2、USB 等。傳統的做法是對應的接口使用對應的接口芯片,例如 PCI 接口芯片,當我需要很多接口時我就需要多個這樣的接口芯片,這無疑會使我們的硬件外設變得復雜,體積變得龐大,會很不方便,但是如果使用 FPGA 優勢立馬就出來了,因為不同的接口邏輯都可以在 FPGA 內部去實現,完全沒必要那么多的接口芯片,在配合 DDR 存儲器的使用,將使我們接口數據的處理變得更加得心應手。

5)人工智能領域

如果大家比較喜歡關注科技板塊的新聞的話最近一定會被 5G 通信和人工智能充斥 眼球,確實 21 世紀已經不知不覺走到了 2020 年,在這 20 年間,人工智能迅速發展,5G 的順利研發也使人工智能如虎添翼,可以預見,未來必將是人工智能的天下。

FPGA 在人工智能系統的前端部分也是得到了廣泛的應用,例如自動駕駛,需要對行駛路線、紅綠燈、路障和行駛速度等各種交通信號進行采集,需要用到多種傳感器,對這些傳感器進行綜合驅動和融合處理就可以使用 FPGA。還有一些智能機器人,需要對圖像進行采集和處理,或者對聲音信號進行處理都可以使用 FPGA 去完成,所以 FPGA 在人工智能系統的前端信息處理上使用起來得心應手。

6)IC?驗證領域

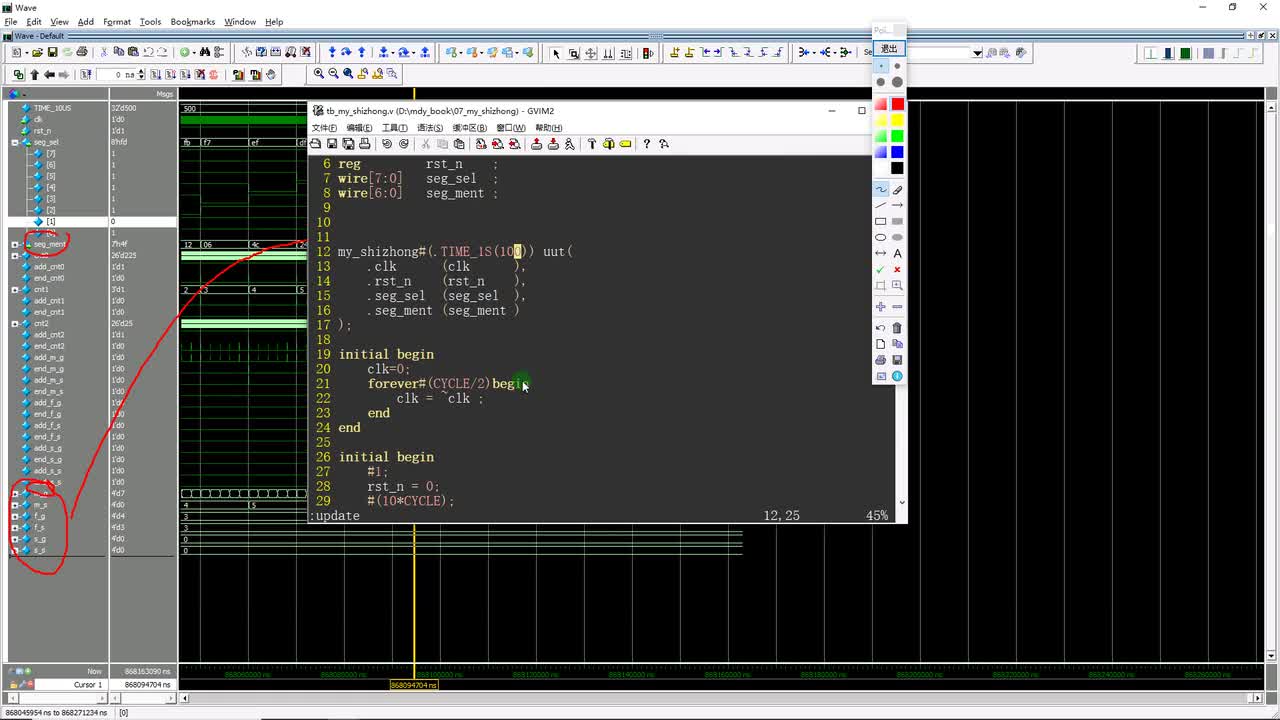

IC 這個詞大家可能一聽到就覺得特別高深,不是凡人所能觸及到的,而 IC 設計更是一些神人才能勝任的工作。不可否認的是 IC 設計門檻確實比較高,但是我們也沒必要把它過于神話,其實簡單點來講我們可以拿 PCB 設計來與之比較,PCB 是拿一個個元器件在印制線路板上去搭建一個特定功能的電路組合,而 IC 設計呢是拿一個個 MOS 管,PN 節在硅基襯底上去搭建一個特定功能的電路組合,一個 宏觀一個微觀。PCB 如果設計廢了大不了重新設計再打樣也不會造成太大損失,但是如果 IC 設計廢了再重新設計那損失就很慘重了,俗話說大炮一開,黃金萬兩,那么在 IC 領域***一開黃金萬兩也不是吹的,光刻膠貴的要命,光刻板開模也不便宜,加上其他多達幾百上千道工序,其中人力、物力、機器損耗、機器保養,絕對是讓人肉疼的損失,所以 IC 設計都要強調一版成功。保證 IC 一版成功就要進行充分的仿真測試和 FPGA 驗證,仿真驗證是在服務器上面跑仿真軟件進行測試,類似 ModelSim/VCS 軟件;FPGA 驗證主要是把 IC 的代碼移植到 FPGA 上面,使用 FPGA 綜合工具進行綜合、布局布線到最終生成 bit 文件,然后下載到 FPGA 驗證板上面進行驗證,對于復雜的 IC 我們還可以給他拆成幾個部分功能去分別驗證,每個功能模塊放在一個 FPGA 上面,FPGA 生成的電路非常接近真實的 IC 芯片。這樣極大的方便我們 IC 設計人員去驗證自己的 IC 設計。

FPGA 的生產廠商

兩大巨頭:Xilinx 和 Altera。

一群小弟:紫光同創、京微雅格、高云半導體、上海安路、西安智多晶等,同國外領先廠商相比,國產 FPGA 廠商不論從產品性能、功耗、功能上都有較大差距。

ZYNQ

ZYNQ = FPGA + ARM 核,可以自己定制電路,同時還可以做普通的嵌入式開發。

Zynq-7000 系列是 Xilinx 公司推出的全可編程片上系統,包含 PS(Processing System,處理器系統)和 PL(Programmable Logic,可編程邏輯)兩部分。Zynq SoC 整合了ARM 雙核 cortex-A9 處理器和 Xilinx 7 系列 FPGA 架構,使得它不僅擁有 ASIC 在能耗、性能和兼容性方面的優勢,而且具有 FPGA 硬件可編程性的優點。

PYNQ:Python Productivity for Zynq = Python + ZYNQ,是 Xilinx 推出的一種開放源代碼框架,使用 Python 語言和庫,使設計人員可以利用 zynq 中可編程邏輯和微處理器的優勢來快速構建高性能的嵌入式應用程序。

補充

PLD:Programmable Logic Device,可編程邏輯器件。

SoC:System on Chip,片上系統。

審核編輯:黃飛

?

電子發燒友App

電子發燒友App

評論