FPGA輸入的時鐘信號必須是方波么?正弦波會有影響么?

FPGA是一種可編程邏輯器件,通常用于實現數字電路。輸入時鐘信號是FPGA中非常重要的時序信號,對整個系統的穩定性和性能都有很大影響。在FPGA設計中,時鐘信號通常需要滿足一定的要求。

首先,時鐘信號在FPGA中必須是一個周期性的信號。這是因為FPGA內部的邏輯電路和存儲元件的工作是基于時鐘信號的邊沿來進行的。通過適當的同步和時序控制,時鐘信號的邊沿可以有效地用來觸發不同的操作和數據傳輸。因此,時鐘信號必須具有與系統同步的周期和相位。

其次,時鐘信號在FPGA中通常需要是一個方波信號。方波信號具有明確的跳變邊沿,適合用來觸發和同步FPGA內部的邏輯運算。方波信號可以提供準確的時序信息,并且與最小化噪聲和時序不確定性有關。

然而,如果使用正弦波作為時鐘信號會有一些影響。首先,正弦波信號的周期和相位通常不是固定的,因此很難確保與FPGA內部邏輯的同步。其次,正弦波信號可能引入額外的相位噪聲和頻率擾動,從而影響FPGA內部時序的穩定性和可靠性。此外,正弦波信號在傳輸過程中存在幅度衰減和相位變化的問題,可能導致時鐘信號信噪比的下降。

為了解決這些問題,通常使用專門的時鐘發生器或PLL電路來生成穩定的方波時鐘信號。這樣可以確保時鐘信號的周期性、相位準確性和穩定性,以滿足FPGA內部邏輯的要求。

總之,FPGA輸入時鐘信號要求為周期性的方波信號,正弦波信號可能會引入相位、頻率和幅度方面的問題,影響FPGA內部邏輯的正確性和性能。因此,在FPGA設計中,使用穩定的方波時鐘信號是非常重要的。

-

FPGA

+關注

關注

1660文章

22412瀏覽量

636320 -

正弦波

+關注

關注

11文章

658瀏覽量

58981 -

時鐘信號

+關注

關注

4文章

505瀏覽量

29974

發布評論請先 登錄

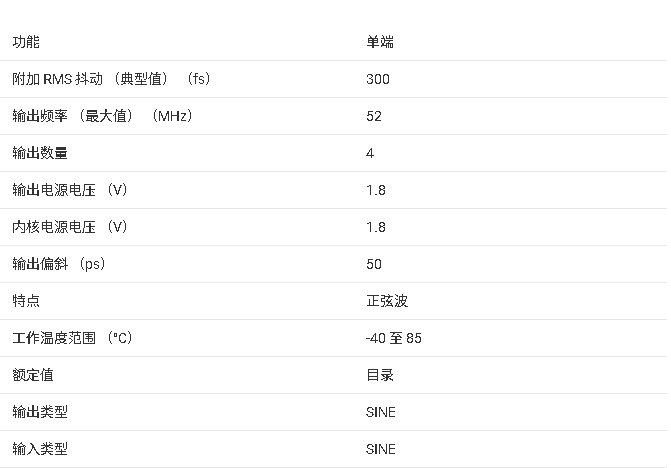

CDC3S04:四通道低功耗低抖動正弦波時鐘緩沖器的卓越之選

基于STM32F103驅動AD9833模塊 DDS信號發生器輸出正弦波/三角波/方波可編程信號

基于STM32F103 并行驅動AD9851模塊 DDS函數信號發生器輸出正弦波/方波信號

普源DG1022Z信號發生器正弦波頻率調節指南

?CDC3S04 四通道正弦波時鐘緩沖器技術文檔總結

信號發生器產生正弦波的頻率精準調節方法

正弦波逆變器的工作原理與控制方式

磁性元件變革:告別正弦波激勵源,擁抱方波

無刷直流電機方波正弦波復合驅動器設計

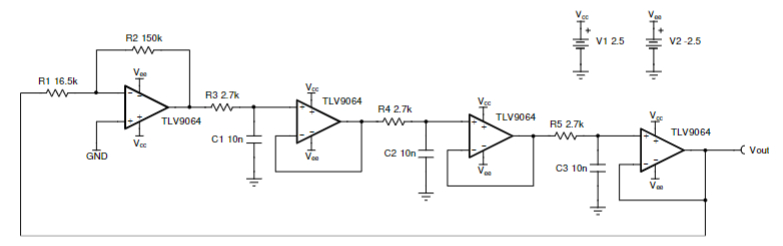

TI 正弦波發生器電路

FPGA輸入的時鐘信號必須是方波么?正弦波會有影響么?

FPGA輸入的時鐘信號必須是方波么?正弦波會有影響么?

評論