聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1660文章

22412瀏覽量

636313 -

收發器

+關注

關注

10文章

3819瀏覽量

111199 -

賽靈思

+關注

關注

33文章

1798瀏覽量

133435

發布評論請先 登錄

相關推薦

熱點推薦

JAE新增支持1000BASE-T1車載以太網標準的MX74系列連接器產品

日本航空電子工業(JAE)關于車載以太網連接器“MX74系列”,在現有支持100BASE-T1車載以太網標準的產品基礎上,新增支持1000BASE-T1標準(可實現1Gbps通信速度)的產品型號,并已正式對外銷售。

AMD 推出第二代 Kintex UltraScale+ 中端FPGA,助力智能高性能系統

第二代AMD Kintex UltraScale+ FPGA 系列 , 對于依賴中端FPGA 為性能關鍵型系統提供支持的設計人員而言,可謂一項重大進步。 這一全新系列構建在業經驗證的

使用Aurora 6466b協議實現AMD UltraScale+ FPGA與AMD Versal自適應SoC的對接

在本博客中,我們將介紹使用 Aurora 6466b 協議實現 AMD UltraScale+ FPGA 與 AMD Versal 自適應 SoC 的對接。我們還將涵蓋有關 IP 配置

解析SN65LVDS10x:4端口LVDS與4端口TTL - LVDS中繼器的卓越性能

解析SN65LVDS10x:4端口LVDS與4端口TTL - LVDS中繼器的卓越性能 在電子設計的領域中,數據傳輸的高效性和穩定性始終是工程師們關注的核心。今天,我們將深入探討德州儀器(TI

電子工程師必看:SN65LVDS10x系列解析與設計指南

- to - LVDS中繼器,為我們在這方面提供了出色的解決方案。今天,我就來詳細解析一下這個系列的產品,以及在設計中需要注意的要點。 文件下載: sn65lvds104.pdf 一、SN65

AMD UltraScale架構:高性能FPGA與SoC的技術剖析

AMD UltraScale架構:高性能FPGA與SoC的技術剖析 在當今的電子設計領域,高性能FPGA和MPSoC/RFSoC的需求日益增長。AMD的UltraScale架構憑借其創

如何利用Verilog HDL在FPGA上實現SRAM的讀寫測試

本篇將詳細介紹如何利用Verilog HDL在FPGA上實現SRAM的讀寫測試。SRAM是一種非易失性存儲器,具有高速讀取和寫入的特點。在FPGA中

NucleiStudio下載程序到FPGA中的E203上

使用NucleiStudio開發應用程序,并將應用程序的代碼下載到FPGA上。這里,以helloworld為例,介紹該過程遇到的問題以及解決方法。

1、新建Nuclei RISC-V C/C++項目,使用ILM的下載

發表于 10-20 09:24

AMD Spartan UltraScale+ FPGA的優勢和亮點

AMD Spartan UltraScale+ FPGA 集小型封裝、先進的 I/O 功能與低功耗等優勢于一體。該系列 FPGA 配備高速 16.3 Gb/s 收發器、內置的外部內存控制器以及

AMD FPGA異步模式與同步模式的對比

本文講述了AMD UltraScale /UltraScale+ FPGA 原生模式下,異步模式與同步模式的對比及其對時鐘設置的影響。

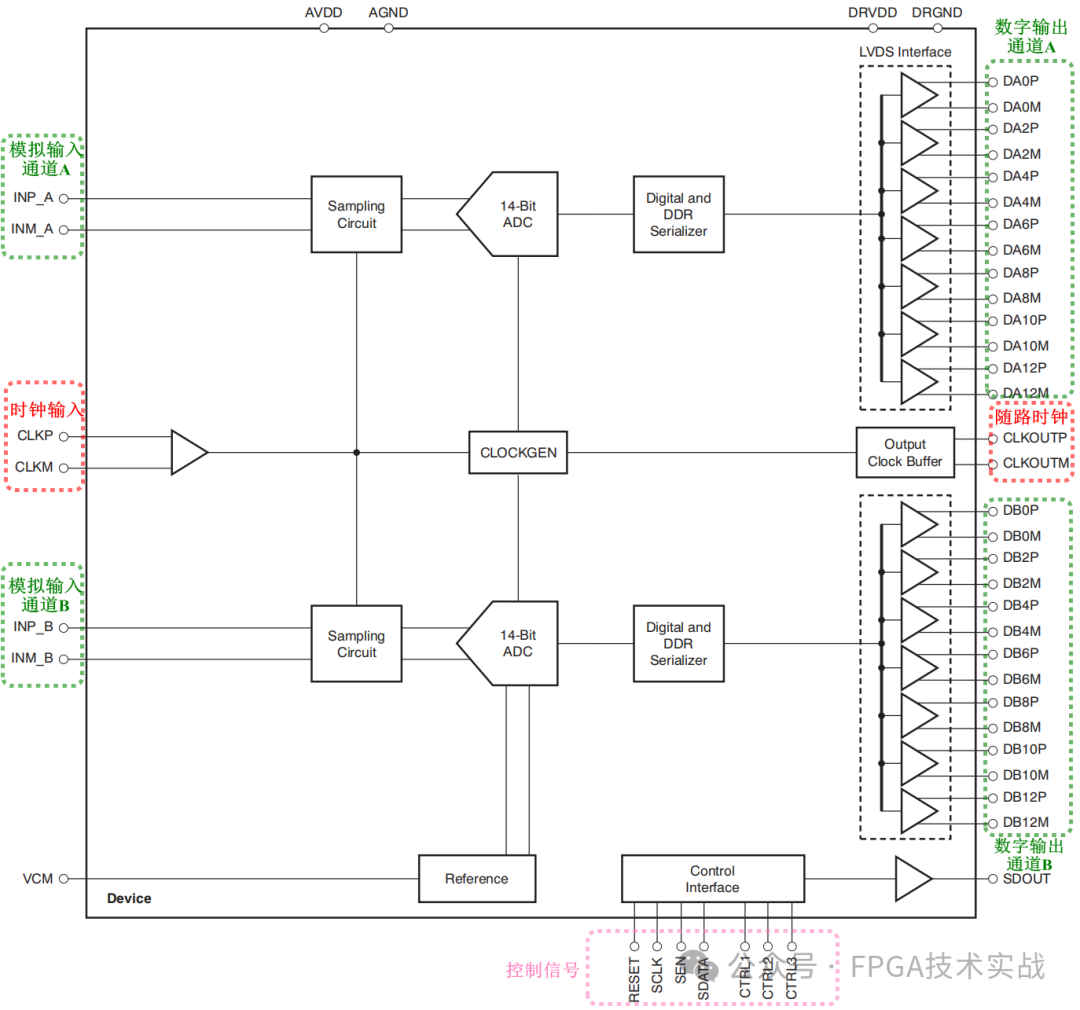

Altera FPGA與高速ADS4249和DAC3482的LVDS接口設計

引言: 本文以TI的ADS4249(ADC)和DAC3482(DAC)之間的接口為例,介紹Altera FPGA與ADC/DAC之間的DDR LVDS接口設計以及時序約束詳細設計。本文介紹

AMD Spartan UltraScale+ FPGA 開始量產出貨

邊緣應用而設計,為業經驗證的 UltraScale+ FPGA 和自適應 SoC 產品組合帶來了現代化的連接、后量子密碼等功能。 三款最低

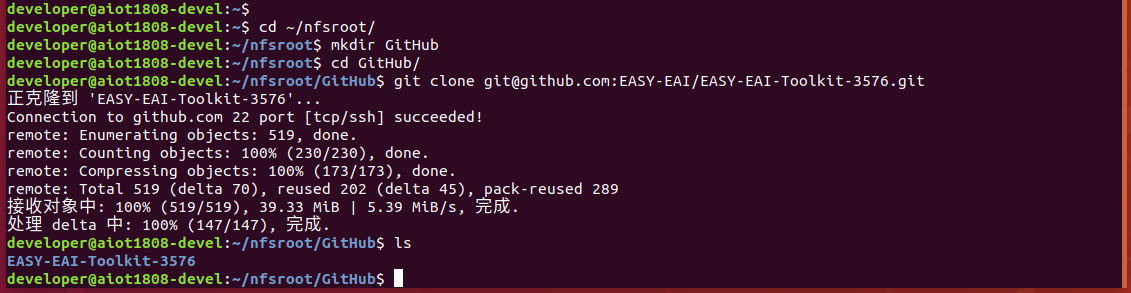

基于RK3576的BASE64編解碼

本文介紹了BASE64編解碼的基本概念及其在EASY-EAI API中的實現。BASE64是一種用于傳輸8Bit字節碼的編碼方式,通過64個可打印字符表示二進制數據。EASY-EAI

Xilinx Ultrascale系列FPGA的時鐘資源與架構解析

Ultrascale是賽靈思開發的支持包含步進功能的增強型FPGA架構,相比7系列的28nm工藝,Ultrascale采用20nm的工藝,主要有2個系列:Kintex和Virtex

UltraScale FPGA中的LVDS上的1000Base-X的介紹

UltraScale FPGA中的LVDS上的1000Base-X的介紹

評論