綜合

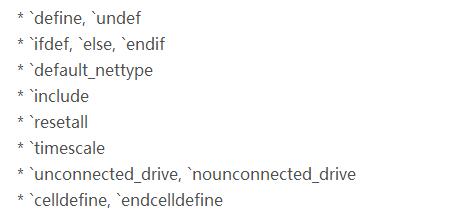

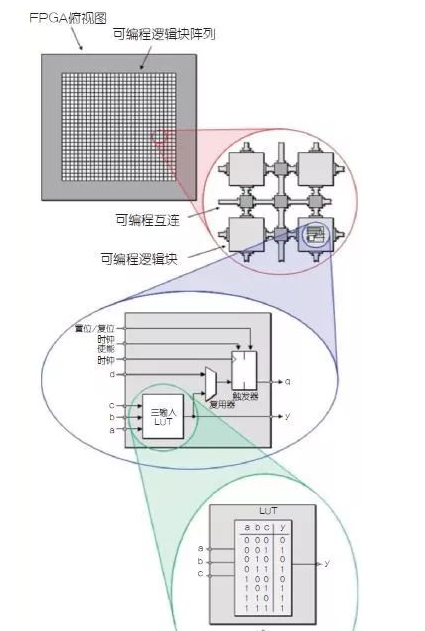

構(gòu)建FPGA的第一階段稱為綜合。此過程將功能性RTL設(shè)計(jì)轉(zhuǎn)換為門級(jí)宏的陣列。這具有創(chuàng)建實(shí)現(xiàn)RTL設(shè)計(jì)的平面分層電路圖的效果。

在這種情況下,宏實(shí)際上是內(nèi)部FPGA單元的模型。這可以是FPGA中的任何數(shù)字元素,例如觸發(fā)器,RAM或查找表(LUT)。

綜合工具

我們可以使用許多不同的工具來運(yùn)行綜合過程。

兩個(gè)主要的FPGA供應(yīng)商(Xilinix 和 Intel)都提供適用于大多數(shù)項(xiàng)目的免費(fèi)綜合工具。

除此之外,還有許多 我們可以使用的開源綜合工具。這些工具中最流行的是 yosys ,它經(jīng)常與 Lattice FPGA一起使用。

也有用于此目的的付費(fèi)工具。這些工具中最著名的是Synopsys的Synplify Pro 和Mentor Graphics的Leonardo Spectrum。

與免費(fèi)工具相比,付費(fèi)工具通常能夠提供更多優(yōu)化的網(wǎng)表。通常,對(duì)于大型或高速設(shè)計(jì),我們只需要付費(fèi)工具即可。

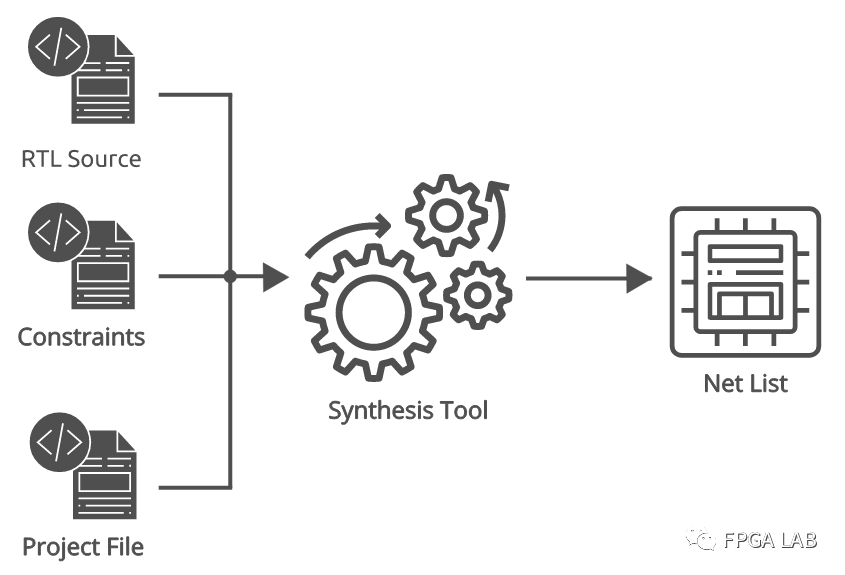

綜合過程至少需要兩個(gè)輸入。

其中第一個(gè)是我們?cè)O(shè)計(jì)的源代碼。

我們還需要一個(gè)腳本或項(xiàng)目文件,用于定義綜合工具的配置。該腳本通常告訴工具目標(biāo)為哪個(gè)FPGA,設(shè)計(jì)的引腳以及在運(yùn)行綜合時(shí)使用哪種策略。

除此之外,優(yōu)良作法是創(chuàng)建一個(gè)文件,該文件定義設(shè)計(jì)的時(shí)序約束,我們稱之為約束文件。

綜合

我們使用時(shí)序約束來定義有關(guān)FPGA的細(xì)節(jié),而這些細(xì)節(jié)無法在源代碼中指定。

這包括諸如時(shí)鐘頻率,時(shí)鐘域數(shù)和外部接口的時(shí)序之類的信息。

這些細(xì)節(jié)決定了綜合器為優(yōu)化FPGA內(nèi)的時(shí)序投入了多少精力。

邏輯利用率

作為綜合過程的一部分,我們還可以對(duì)設(shè)計(jì)進(jìn)行一些分析。但是,在布局和布線過程之后,此信息通常更可靠。

這些分析中的第一個(gè)是設(shè)計(jì)的邏輯利用率。該分析詳細(xì)說明了我們?cè)O(shè)計(jì)使用的每種不同類型的FPGA單元有多少個(gè)。

設(shè)備中的各個(gè)單元隨芯片的不同以及供應(yīng)商之間的不同而不同。

幾乎所有現(xiàn)代芯片都將包括RAM,某種形式的LUT和觸發(fā)器。

高端芯片還可以包括專用的DSP內(nèi)核,時(shí)鐘管理模塊(例如PLL)以及其他外圍接口(例如ADC)或?qū)S玫母咚俳涌凇?/p>

完成綜合過程后,我們可以生成報(bào)告,以絕對(duì)值和器件中所有可用單元的百分比告訴我們?cè)O(shè)計(jì)中使用了多少個(gè)單元。

在運(yùn)行綜合過程之后,經(jīng)常會(huì)發(fā)現(xiàn)我們的設(shè)計(jì)對(duì)我們的設(shè)備而言太大了。發(fā)生這種情況時(shí),我們有很多選擇。

通常可以通過更改綜合工具的配置來降低利用率。這樣的示例可以是更改FSM編碼或選擇其他綜合算法。

如果我們的設(shè)計(jì)僅比我們選擇的FPGA大一點(diǎn),那么這種減少就足夠了。

如果這還不能充分降低利用率,那么我們必須選擇一個(gè)新的FPGA或提高原始代碼的效率。

時(shí)序分析

運(yùn)行綜合后,我們還可以分析FPGA的時(shí)序。

我們使用該分析來確定FPGA是否可以以所需的頻率運(yùn)行我們的設(shè)計(jì)。

當(dāng)我們的設(shè)計(jì)不能以所需的頻率運(yùn)行時(shí),我們不能確定內(nèi)部觸發(fā)器將不會(huì)有時(shí)序違規(guī)。因此,我們無法保證我們的設(shè)備能夠按預(yù)期運(yùn)行。

我們通常會(huì)在布局和布線過程之后詳細(xì)分析設(shè)計(jì)的時(shí)序。由于時(shí)序取決于FPGA中單元的位置,因此經(jīng)過此過程,結(jié)果將更加準(zhǔn)確。

綜合后仿真

在綜合過程中,我們可以要求該工具以VHDL或verilog生成網(wǎng)表。

此過程還生成一組時(shí)序延遲,該時(shí)序延遲可對(duì)信號(hào)通過FPGA的傳播進(jìn)行建模。

然后,我們可以使用此信息來運(yùn)行我們的綜合網(wǎng)表的仿真。

由于這些仿真還可以對(duì)我們的設(shè)計(jì)時(shí)序進(jìn)行建模,因此它們可以為最終設(shè)備的行為提供更準(zhǔn)確的模型。

無論我們?cè)谠O(shè)計(jì)中使用哪種語(yǔ)言,我們通常都使用verilog生成綜合后仿真模型。

這樣做的原因是基于Verilog的模型比其VHDL等效模型的仿真速度更快。這對(duì)于綜合后仿真尤其重要,因?yàn)樗鼈兺ǔ?zhí)行時(shí)間較長(zhǎng)。

運(yùn)行綜合后仿真有兩個(gè)主要優(yōu)點(diǎn)。

- 首先,這些仿真有助于確保我們生成的網(wǎng)表與原始RTL模型的行為相匹配。

- 其次,可以更緊密地考慮芯片的時(shí)序。這有助于我們發(fā)現(xiàn)可能與基于時(shí)序的錯(cuò)誤(例如時(shí)序違規(guī))相關(guān)的錯(cuò)誤。

盡管運(yùn)行后綜合仿真有很多優(yōu)點(diǎn),但是我們通常不會(huì)在設(shè)計(jì)流程中這樣做。

- 原因之一是這些仿真需要很長(zhǎng)時(shí)間才能運(yùn)行。綜合后的仿真需要幾天來運(yùn)行全套測(cè)試的情況并不少見。

- 另一個(gè)原因是,我們也可以在由我們的布局和布線工具生成的網(wǎng)表上運(yùn)行仿真。

由于這些網(wǎng)表更能代表最終的芯片方案,因此最好使用該網(wǎng)表進(jìn)行任何時(shí)序仿真。

布局布線(實(shí)現(xiàn))

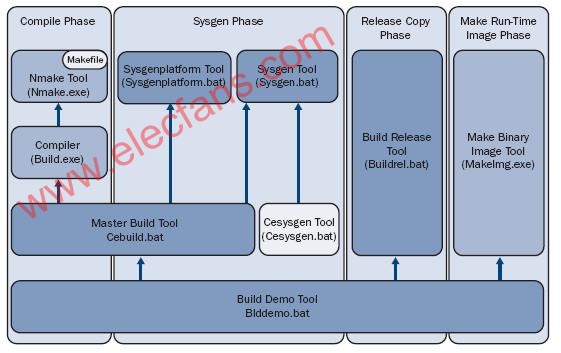

完成綜合后,我們需要將網(wǎng)表映射到FPGA中的實(shí)際資源。此過程稱為“布局布線”,實(shí)際上包含幾個(gè)不同的步驟。

- 通常,此過程的第一階段涉及優(yōu)化網(wǎng)表。我們使用此過程刪除或替換網(wǎng)表中任何多余或重復(fù)的元素。

- 然后,將優(yōu)化后的網(wǎng)表映射到FPGA中的物理單元,這通常稱為布局。

- 完成布局過程后,然后運(yùn)行稱為布線的過程。

我們使用構(gòu)建過程的這一部分來定義所選FPGA中不同單元之間的互連。

為了滿足設(shè)計(jì)的時(shí)序要求,我們通常會(huì)執(zhí)行此過程的幾次運(yùn)行。但是,布局布線工具負(fù)責(zé)根據(jù)我們的配置安排這些多次運(yùn)行。

當(dāng)我們難以使設(shè)計(jì)滿足時(shí)序要求時(shí),通常會(huì)增加允許工具執(zhí)行的運(yùn)行次數(shù)和類型。

布局布線工具

對(duì)于Xilinx或Intel部件,沒有第三方布局和布線工具,這意味著我們必須使用供應(yīng)商特定的工具。這些版本可以免費(fèi)下載,盡管也提供付費(fèi)版本。

這些工具也有付費(fèi)版本可用,盡管通常只有針對(duì)高端FPGA的設(shè)計(jì)才需要它們。

對(duì)于萊迪思的FPGA,開源的nextpnr軟件是一種流行的布局布線工具。

根據(jù)我們?cè)O(shè)計(jì)的大小,布局和布線過程可能需要幾個(gè)小時(shí)才能完成。

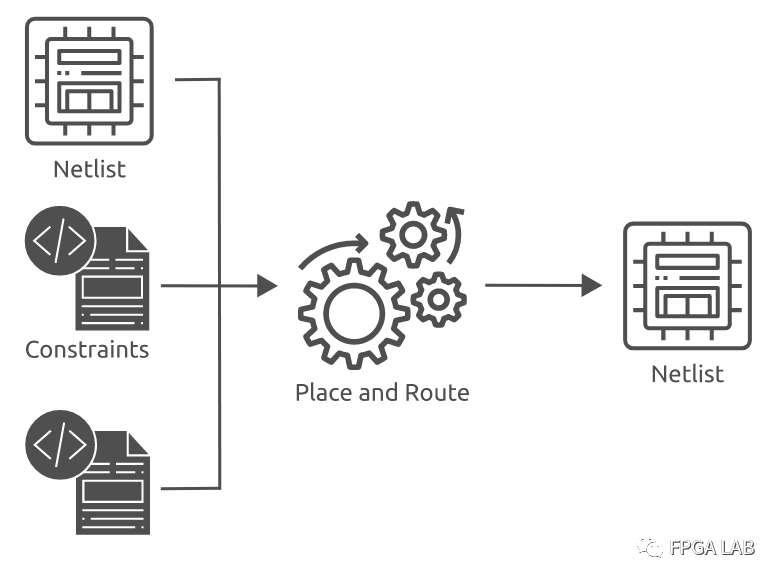

與綜合過程一樣,布局布線工具需要大量輸入才能正確運(yùn)行。

我們使用綜合工具生成的網(wǎng)表是最重要的輸入。該網(wǎng)表通常是.edf文件,盡管這在工具之間有所不同。

通常,我們還使用項(xiàng)目文件或腳本來確定布局和布線工具的配置。

我們使用它來定義重要信息,例如FPGA零件號(hào)和封裝。除此之外,我們使用此腳本定義布局和路線工具的配置。

我們還需要向工具提供一個(gè)約束文件,以定義我們?cè)O(shè)計(jì)的時(shí)序特征。該文件通常與我們?cè)诰C合過程中使用的文件相同,該文件定義了有關(guān)時(shí)鐘頻率和域的信息。

我們還使用約束文件來定義我們的設(shè)計(jì)的物理特性,而這些特性在HDL代碼中無法描述。至少,這將包括輸入和輸出到設(shè)備物理引腳的映射。

流程圖顯示了綜合網(wǎng)表,約束和項(xiàng)目文件作為布局和布線工具的輸入,網(wǎng)表作為輸出。

布局布線

時(shí)序與利用率

與綜合過程一樣,在布局和路線完成之后,我們可以生成許多報(bào)告。這使我們可以進(jìn)一步分析設(shè)計(jì)以確保其正常工作。

我們通常會(huì)在完成布局和布線過程后運(yùn)行實(shí)用程序報(bào)告。

該報(bào)告詳細(xì)介紹了我們用于通過FPGA實(shí)現(xiàn)設(shè)計(jì)的不同單元的數(shù)量。

該報(bào)告與我們?cè)诰C合過程中可以生成的報(bào)告完全相同。但是,當(dāng)我們?cè)谕瓿刹季植季€過程后生成此報(bào)告時(shí),該報(bào)告會(huì)更準(zhǔn)確。

我們通常在完成布局和布線過程后執(zhí)行的另一項(xiàng)分析是靜態(tài)時(shí)序分析(STA)。

我們使用此過程來計(jì)算設(shè)計(jì)中所有邏輯鏈的延遲時(shí)間。通過計(jì)算此信息,布局布線工具可以確定芯片是否能夠以指定的時(shí)鐘頻率運(yùn)行。

布局布線工具會(huì)在最壞情況和最佳情況下的定時(shí)條件下執(zhí)行此分析。但是,最常見的情況是在硅中出現(xiàn)最壞情況下的延遲會(huì)導(dǎo)致時(shí)序問題。

我們通常將STA報(bào)告用作設(shè)計(jì)驗(yàn)證的關(guān)鍵部分。

如果我們的設(shè)計(jì)使STA失敗,那么我們將無法保證FPGA能夠可靠地工作。發(fā)生這種情況時(shí),我們要么必須使用不同的設(shè)置再次運(yùn)行實(shí)施過程,要么必須更改設(shè)計(jì)。

編程文件生成

FPGA設(shè)計(jì)實(shí)現(xiàn)的最后階段是生成編程文件。

通常,我們使用布局和布線工具來生成我們的編程文件。

但是,我們通常將其作為單獨(dú)的過程運(yùn)行。

僅當(dāng)布局和布線過程生成其輸出后,才能運(yùn)行此過程。我們只需要告訴工具生成該輸出所需的文件類型即可。

完成此過程后,我們可以使用生成的文件對(duì)FPGA進(jìn)行編程。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論