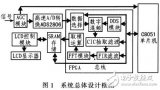

該系統采用C8051系列單片機中的 C8051F121作為控制器,CvcloneⅢ系列EP3C40F484C8型FPGA為數字信號算法處理單元。

2015-02-03 15:58:26 5785

5785

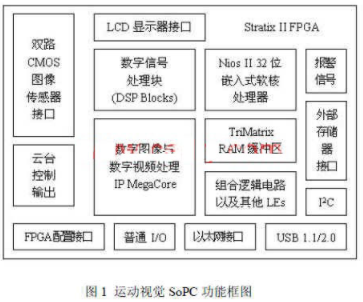

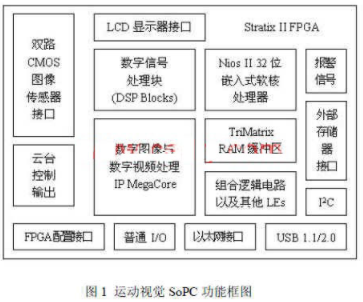

該模塊主要負責視頻圖像的采集,攝像頭參數的設置和云臺步進電機的控制。其中,通過 I2C總線可以設定攝像頭內部控制寄存器。在 FPGA中,實現 I2C總線控制器的途徑有兩種:一種是在 Nios II

2020-08-19 16:11:33 1283

1283

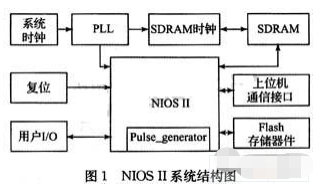

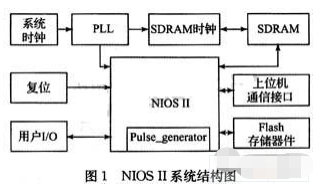

只有設計出了高頻率的、參數化的脈沖發生器,脈沖加工電源的精度、參數化才可以實現。該電源系統中采用的是性價比較好的Altera公司的Cyclone II序列的FPGA芯片EP2C8Q208C7。其邏輯資源足夠實現系統的功能。

2021-02-23 10:01:45 3861

3861

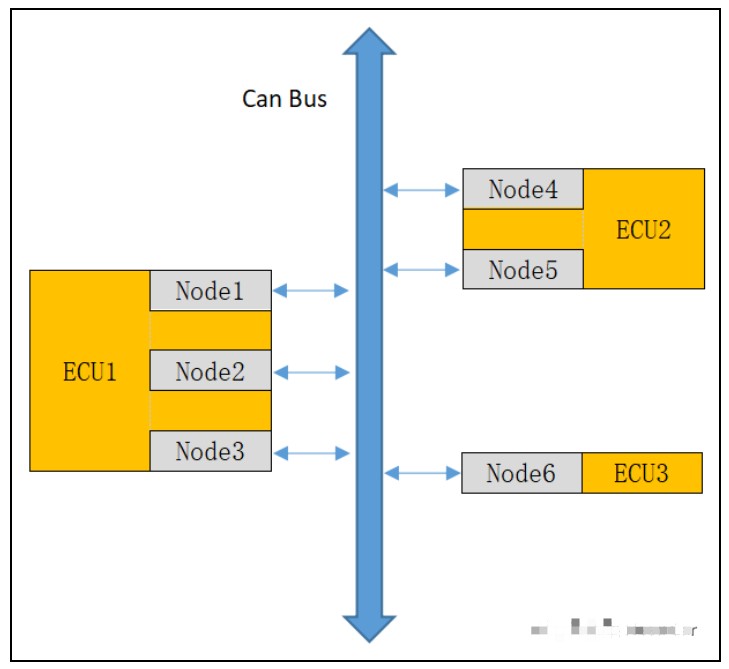

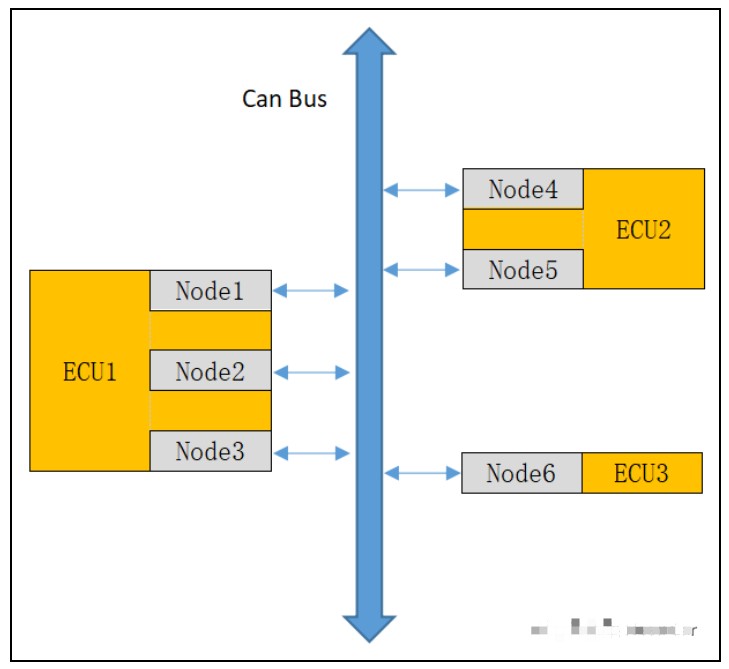

TSMaster軟件平臺支持對不同總線(CAN、LIN、FlexRay)報文和信號的過濾,包括全局接收過濾、數據流過濾、窗口過濾、字符串過濾、可編程過濾,針對不同的總線信號過濾器的使用方法基本相

2024-06-22 08:21:30 2885

2885

EP2S60F484I4N特價 EP2S60F484I4N貨期EP2S60F484I4N 價格EP2S60F484I4N國宇航芯特價訂貨EP2S60F484C4N國宇航芯特價訂貨

2020-01-06 09:07:44

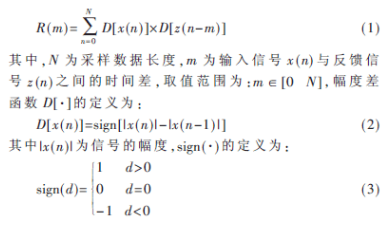

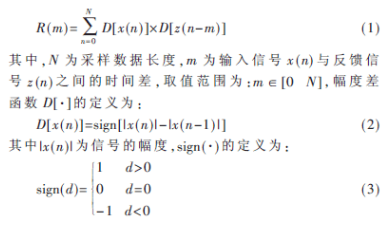

采集數據中的量化噪聲,在進行數據壓縮前采用濾波的預處理技術。介紹LZW算法和滑動濾波算法的基本理論,詳細闡述用單片FPGA實現兩種算法的方法。最終測試結果表明,該設計方案能夠有效濾除數據中的高頻噪聲

2010-04-24 09:05:21

的數目之外,就是采用可編程邏輯器件,主要是FPGA芯片來實現。本課程以DSP設計在FPGA芯片上的開發為主線,遵照由淺入深的基本步驟和思路進行詳細講解,每一個知識點都給出了基于ISE(HDL語言

2009-07-21 09:22:42

最近,需要使用fpga實現iec-61850-9-2報文編碼,設計中涉及到的 字段非常多,以至于邏輯特別復雜,占用資源太多,設計的頻率上不去。有沒有哪位同道做過fpga報文編碼類的設計,請不吝賜教。

2013-11-12 23:20:19

fpga實現濾波器fpga實現濾波器在利用FPGA實現數字信號處理方面,分布式算法發揮著關鍵作用,與傳統的乘加結構相比,具有并行處理的高效性特點。本文研究了一種16階FIR濾波器的FPGA設計方法

2012-08-12 11:50:16

就已經出現,隨著FPGA芯片價格的不斷降低,其在工業領域的應用正在飛速發展,采用FPGA來實現SVPWM調制算法也將層出不窮2. 系統任務分析及實現SVPWM調制算法相對比較復雜,在完成系統控制任務

2022-01-20 09:34:26

CAN過濾器的配置(f103 hal1.8 系列)can的過濾器的配置是對can接收到的報文進行過濾的配置,在STM32芯片中,可以對can的報文進行過濾,從而省略cpu的處理過程。can的過濾模式

2021-08-19 06:11:28

我現在使用CC3200 transceiver mode,我想將報文過濾下,請問transceiver mode下支持sl_WlanRxFilterAdd 過濾條件添加嗎?如果能,我想要根據field:FRAME_SUBTYPE_FIELD來過濾,能給一個例子嗎

2016-04-27 10:12:25

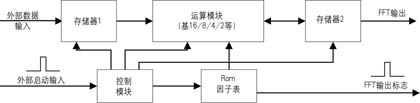

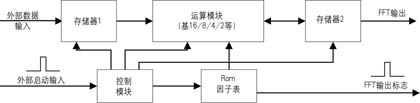

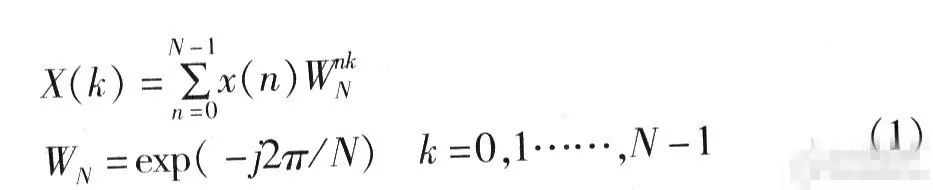

FPGA實現的 FFT 處理器的硬件結構。接收單元采用乒乓RAM 結構, 擴大了數據吞吐量。中間數據緩存單元采用雙口RAM , 減少了訪問RAM 的時鐘消耗。計算單元采用基 2 算法, 流水線結構, 可在

2017-11-21 15:55:13

的要求和FPGA芯片設計的靈活性結合起來,采用Alter公司的CycloneⅡ系列FPGA芯片EP2C35F672C8,用VHDL語言編程,最后分別使用Quartus Ⅱ和Matlab軟件開發工具驗證實現

2010-05-28 13:38:38

求助!STC12C5A60S2無法實現開平方算法(sqrt函數),以及atan2和asin怎么辦?我已經包含了相關的頭文件了,但是編譯通不過。

2020-05-20 09:07:38

下面內容為轉載:一、在STM32互聯型產品中,CAN1和CAN2分享28個過濾器組,其它STM32F103xx系列產品中有14個過濾器組,用以對接收到的幀進行過濾。1、過濾器組 每組過濾器包括了2個

2021-08-23 07:29:40

處理器的數目之外,就是采用可編程邏輯器件,主要是FPGA芯片來實現。本課程以DSP設計在FPGA芯片上的開發為主線,遵照由淺入深的基本步驟和思路進行詳細講解,每一個知識點都給出了基于ISE(HDL語言

2009-07-21 09:20:11

內容簡介這是一本深入解讀基礎算法及其電路設計,以打通算法研發到數字IC設計的實現屏障,以及指導芯片設計工程師從底層掌握復雜電路設計與優化方法為目標的專業技術書。任何芯片(如WiFi芯片、5G芯片

2024-11-21 17:14:02

的不足,同時也方便在現場可編程門陣列(FPGA)中增加一些其他相關的應用功能,因此在FPGA中實現CVSD語音編譯碼調制功能的前景將是非常廣闊的。這里將詳細介紹什么是CVSD?其算法分析如何在FPGA中實現?

2019-08-07 07:04:27

基于FPGA的FFT算法研究

2012-08-24 01:09:50

基于FPGA的模糊PID控制算法的研究及實現

2013-03-18 14:25:05

進行了校驗,通過了功能仿真。同時,借助于QuatusII綜合布線工具,使用Altera公司的StratixII EP2S60 FPGA芯片進行了綜合、布線,模塊的運行頻率達到107MHz,RLDRAM

2008-10-07 11:00:19

本設計方案采用了一種改進的快速中值濾波算法,成功地在Altera公司的高性能Stratix II EP2S60上實現整個數字紅外圖像濾波,在保證實時性的同時,使得硬件體積大為縮減,大大降低了成本

2021-04-23 06:00:55

ALTERA的高端FPGA芯片Stratix II EP2S系列EP2S60,板卡使用FPGA用于獲取雙通道數據采集,實現1路的Base CameraLink輸入,一路Base CameraLink

2012-06-13 11:39:49

ALTERA的高端FPGA芯片Stratix II EP2S系列EP2S60,板卡使用FPGA用于獲取雙通道數據采集,實現1路的Base CameraLink輸入,一路Base CameraLink

2012-06-13 12:01:23

本設計中采用了ALTERA公司的 EP1C3T144芯片進行設計,實際測試表明系統的各項設計要求均得到滿足并且系統工作良好,該設計采用了SOPC技術和FPGA,幾乎將整個系統下載于同一芯片中,實現了

2021-04-30 06:56:14

如何采用FPGA芯片完成基于LMS算法的自適應譜線增強系統的設計?

2021-04-29 06:55:16

如何采用STC12C5A60S2實現無線多功能防火報警系統的設計?

2021-10-13 07:07:03

和模式識別的主要特征提取手段,在計算機視覺、圖像分析等應用中起著重要的作用,是圖像分析與處理中研究的熱點問題。數字信號和圖像處理算法的實現有多種途徑,傳統上多采用高級語言編程實現,便于使用的還有

2019-07-31 06:38:07

介紹了利用現場可編程邏輯門陣列FPGA實現直接數字頻率合成(DDS)的原理、電路結構和優化方法。重點介紹了DDS技術在FPGA中的實現方法,給出了采用ALTERA公司的ACEX系列FPGA芯片EP1K30TC進行直接數字頻率合成的VHDL源程序。

2021-04-30 06:29:00

如何去實現一種基于stc15f2k60s2芯片的流水燈編程呢?

2021-10-25 06:48:41

如何在ALTERA公司的Quartus II環境下用VHDL、Verilog HDL實現設計輸入,采用同步時鐘,成功編譯、綜合、適配和仿真,并下載到Stratix系列FPGA芯片EP1S25F780C5中。

2021-04-15 06:19:38

一種在FPGA中實現的基于軟判決的Viterbi譯碼算法,并以一個(2,1,2)、回溯深度為10的軟判決Viterbi譯碼算法為例驗證該算法,在Xilinx的XC3S500E芯片上實現了該譯碼器,最后對其性能做了分析。 關鍵詞: OFDM;Viterbi譯碼;軟判決;FPGA

2009-09-19 09:41:24

各位朋友好,我的導師要求我設計一個新的報文調度算法,能夠實現不同優先級的報文在發送的過程中,實現高優先級報文的低延時和低抖動。要求使用stm32的LWIP協議棧進行報文調度算法的開發,請問要實現

2020-04-07 04:35:59

和Motion JPEG三種算法,有將這3種算法用FPGA實現的大神么?還有就是這3種算法到底適不適合用FPGA實現,麻煩有過研究的大大們分析下啊!謝謝!PS:如果有這3種算法的資料說明麻煩大家分享下,我找到的都是C語言的源碼,看起來好吃力!

2017-07-04 11:17:17

方面不支持64位操作,于是RC6修正這個錯誤,使用4個32位寄存器而不是2個64位寄存器,以更好地實現加解密。利用FPGA來實現RC6算法,可以提高運算速度。芯片設計為RC6算法處理器,輔助計算機處理器完成加解密操作,可以方便地實現對加解密的分析和研究。因此,此芯片可以作為協處理器來看待。

2019-08-19 07:27:09

本帖最后由 eehome 于 2013-1-5 10:04 編輯

指紋識別算法的研究及基于FPGA的硬件實現

2012-05-23 20:14:46

設計題目:基于NXP K60的蜂窩物聯網數據傳輸終端設計1. 設計所采用的控制芯片必須是K60系列;2. 蜂窩物聯網芯片推薦采用中移物聯網公司的NB-IoT系列芯片。3. 數據傳輸關系:RS485

2019-12-19 21:27:55

和論證的基礎上,選取較優化的預處理算法,作為FPGA指紋預處理平臺的算法。并用FPGA實現所選算法。1 處理步驟 本系統采用XILINX公司Spartan 3E系列FPGA作為核心控制芯片,通過富士通

2009-09-19 09:38:11

協同過濾算法的原理及實現基于物品的協同過濾算法詳解協同過濾算法的原理及實現

2020-11-05 06:51:34

基FPGA Cyclone II_EP2C5 EP2C8的頻率計

基FPGA_Cyclone_II_EP2C5/EP2C8的頻率計

功能描述:按4*4鍵盤上的1,2,3...號按鍵可依次測出 25000000Hz ,12500000Hz ....的分

2008-11-30 12:17:01 87

87 本文基于Altera的FPGA(StatixⅡ-EP2S30F484C3)架構,實現了碼率為1/2,幀長為1008bits的規則(3,6)LDPC碼譯碼器。所采用的最小-和算法相對于傳統的和-積算法在不損失譯碼性能的前提下,

2009-06-06 14:12:20 31

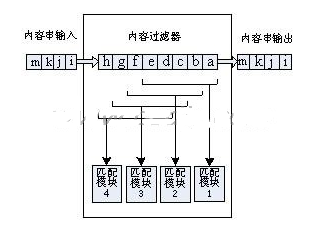

31 模式匹配是基于攻擊特征的信息過濾系統中的網絡數據包分析技術,匹配算法的性能直接影響到整個系統的效率,是當前信息過濾監測系統的一個主要瓶頸,因此以速度較快的BM

2009-08-15 11:36:28 19

19 IP 過濾是把IP 數據報文分成不同種類的過程,主要取決于IP 報頭中的信息。基于軟件的字符串匹配已經不能跟上高速的網絡傳輸速度,需要尋找

2009-09-09 09:17:52 16

16 介紹AES 算法的原理以及基于FPGA 的高速實現。結合算法和FPGA 的特點,采用查表法優化處理了字節代換運算、列混合運算。同時,為了提高系統工作速度,在設計中應用了內外結合

2010-01-25 14:26:51 29

29 Stratix II EP2S60 DSP Development Board

The Stratix® II EP2S60 DSP development board

2010-04-07 10:54:27 53

53 介紹AES算法的原理以及基于FPGA的高速實現。結合算法和FPGA的特點,采用查表法優化處理了字節代換運算、列混合運算。同時,為了提高系統工作速度,在設計中應用了內外結合的流水線

2010-07-17 18:09:43 46

46 介紹了AES中,SubBytes算法在FPGA的具體實現.構造SubBytes的S-Box轉換表可以直接查找ROM表來實現.通過分析SubBytes算法得到一種可行性硬件邏輯電路,從而實現SubBytes變換的功能.

2010-11-09 16:42:48 25

25

橫向LMS算法是實現自適應數字波束形成的基本方法之一。提出了一種用Matab/Simulink中DSP Builder模塊庫設計算法模型,然后應用FPGA設計軟件Modelsim 、QuartusII分析自適應濾波

2010-12-07 14:03:38 23

23 提出一種基于DCT域的數字水印算法,并用FPGA硬件實現其中關鍵部分DCT變換。采用VHDL語言有效設計和實現DCT變換,分析與仿真結果表明:與軟件實現相比,用FPGA實現水印算法具有高

2010-12-28 10:22:14 20

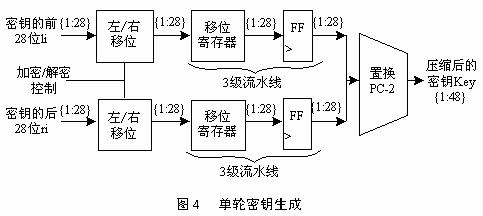

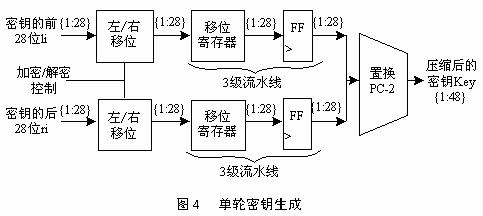

20 摘要:介紹3-DES算法的概要;以Xilinx公司SPARTANII結構的XC2S100為例,闡述用FPGA高速實現3-DES算法的設計要點及關鍵部分的設計。引 言

2006-03-13 19:36:42 1016

1016

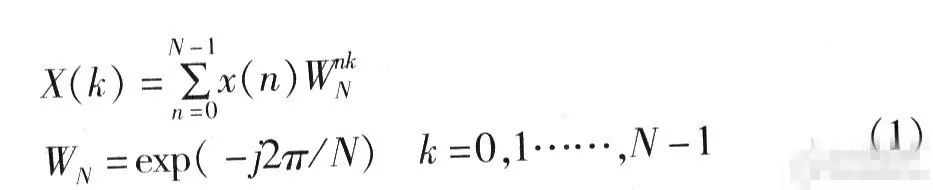

用FPGA實現FFT算法

引言 DFT(Discrete Fourier Transformation)是數字信號分析與處理如圖形、語音及圖像等領域的重

2008-10-30 13:39:20 1843

1843

摘要:介紹3-DES算法的概要;以Xilinx公司SPARTANII結構的XC2S100為例,闡述用FPGA高速實現3-DES算法的設計要點及關鍵部分的設計。

關鍵詞:3-DES

2009-06-20 14:22:00 1600

1600

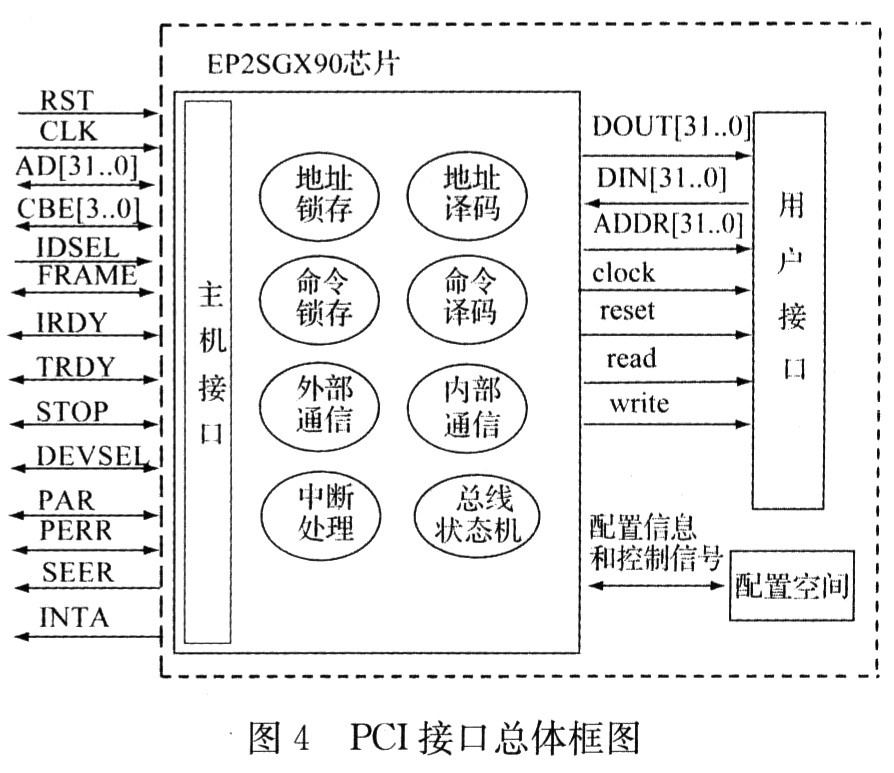

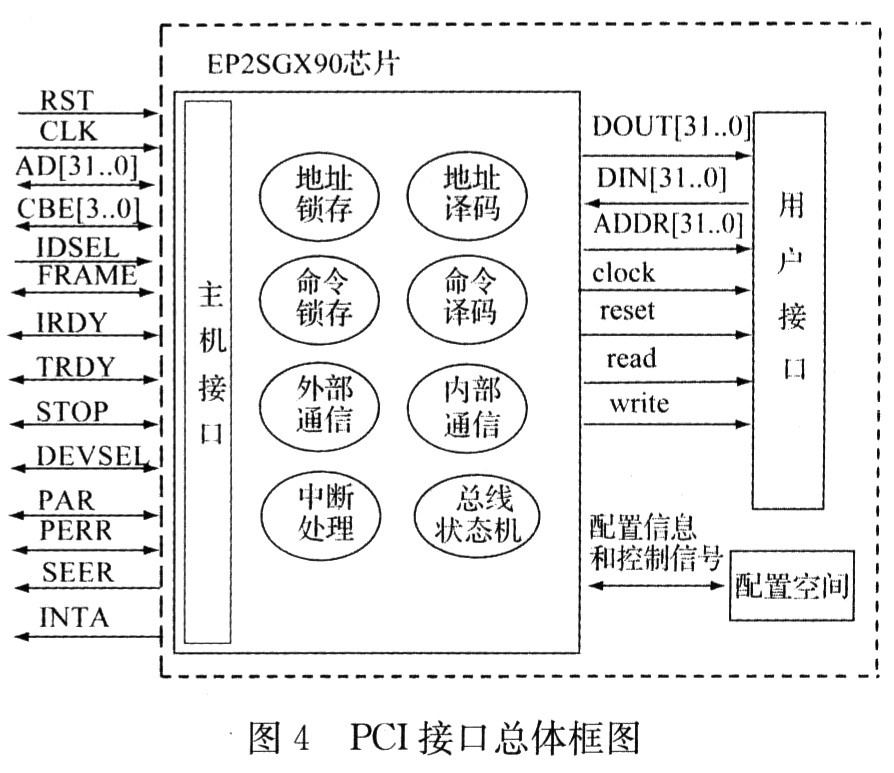

基于EP2SGX系列FPGA的PCI接口設計

0 引 言??? 在現代雷達數據處理系統和其他應用系統中,傳統的ISA、EISA等總線已逐漸無法適應高速數據傳輸的要求。而PCI局

2009-12-04 11:16:58 1121

1121

全相位頻譜分析APFFT是傳統FFT 的一種改進算法5 能改善FFT 的柵欄效應和截斷效 應#具有頻譜泄露少$相位不變的特性% 介紹采用FPGA器件實現APFFT 算法# 精度高于模擬式測量# 并且適用性強$成本低#所得到的LMG-NM3OO 仿真結果與MATLAB 軟件仿真結果一致.

2011-02-11 14:10:31 69

69 本文介紹的電子消像旋系統采用Altera公司的StratixII系列FPGA芯片和ADI公司的ADSP2183為核心,可以滿足系統對功能、實時性及精度的要求。

2011-09-13 11:28:00 1717

1717

差分功耗分析是破解AES密碼算法最為有效的一種攻擊技術,為了防范這種攻擊技術本文基于FPGA搭建實驗平臺實現了對AES加密算法的DPA攻擊,在此基礎上通過掩碼技術對AES加密算法進行優

2011-12-05 14:14:31 52

52 EP2C5T144C8-FPGA開發板采用Altera公司推出的CYCLONEⅡ系列芯片EP2C5T144C8芯片作為核心處理器進行設計,CYCLONEⅡ系列芯片可以說是目前市場上性價比較高的芯片,比第一代的EP1C6或者EP1C12等芯片

2011-12-06 10:24:54 671

671 以Altera公司的FPGA EP2S60為例,探討了SOPC系統設計的綜合優化方法。

2012-03-12 11:49:28 1720

1720

本系統的設計是基于Altera公司的EP2S60系列的開發板,板上集成兩片 SDRAM存儲芯片、視頻輸入接口和VGA輸出接口

2012-12-16 10:07:31 1553

1553 ECT圖像重建算法的FPGA實現

ECT圖像重建算法的FPGA實現

2015-11-19 14:59:41 2

2 基于FPGA的JPEG解碼算法的研究與實現,很好的資料,快來學習吧

2016-02-18 13:53:55 0

0 基于FPGA的模糊PID控制算法的研究及實現-2009。

2016-04-05 10:39:29 22

22 CCD圖像的顏色插值算法研究及其FPGA實現

2016-08-29 15:02:03 12

12 FPGA平臺實現基于遺傳算法的圖像識別的研究

2016-08-29 15:02:03 11

11 基于FPGA的JPEG解碼算法的研究與實現

2016-08-29 16:05:01 11

11 基于FPGA的數字信號處理算法研究與高效實現

2016-08-29 23:20:56 42

42 神經網絡圖像壓縮算法的FPGA實現技術研究,下來看看

2016-09-17 07:29:23 19

19 空間圖像CCSDS壓縮算法研究與FPGA實現,感興趣小伙伴們可以瞧一瞧。

2016-09-18 14:57:42 17

17 基于FPGA的ECC快速算法研究及設計_陳俊杰

2017-01-07 19:08:43 2

2 算法進行深入研究,面向Xilinx K7 410T FPGA 芯片設計SHA-1算法實現結構,完成SHA-1算法編程,進行測試和后續應用。該算法在FPGA 上實現,可以實現3.2G bit/s的吞吐率

2017-10-30 16:25:54 4

4 描述語言實現,最終下載到FPGA芯片Stratix EP1S25F780C5中。 關鍵詞: 狀態機 流水線 3DFS FPGA 隨著網絡的快速發展,信息安全越來越引起人們的關注。加密技術作為信息安全的利器,正發揮著重大的作用。通過在硬件設備(如由器、交換機等)中添加解

2017-11-06 11:10:09 7

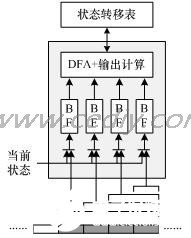

7 針對當前采用正則表達式匹配的深度報文檢測系統匹配效率低下,難以滿足高速網絡線速處理的問題,本文提出了一種基于現場可編程門陣列(Field Programmahle Gate ArraV,FPGA

2017-11-10 11:06:55 7

7 公司的Spartan6系列FPGA芯片,系統可以實現將四路攝像頭采集的視頻信號從任意通道放大到1 920x1 080@60 Hz的分辨率顯示,結果表明輸出視頻圖像的實時性和細節保持良好。

2017-11-16 11:48:09 5853

5853

介紹一種采用FPGA(現場可編程門陣列電路)實現SDH(同步數字體系)設備時鐘芯片設計技術,硬件主要由1 個FPGA 和1 個高精度溫補時鐘組成.通過該技術,可以在FPGA 中實現需要專用芯片才能實現的時鐘芯片各種功能,而且輸入時鐘數量對比專用芯片更加靈活,實現該功能的成本降低三分之一.

2017-11-21 09:59:00 2653

2653

本文采用Altera公司Stratix II系列的EP2S90F1508C3芯片,以Quartus II 8.1為開發環境[4],采用硬件描述語言VHDL進行SM3算法的FPGA實現。SM3算法實現

2017-11-24 15:33:59 3108

3108

針對防火墻粗粒度過濾Modbus/TCP導致工控系統存在安全威脅的問題,研究基于Modbus功能碼的細粒度過濾算法。基于Modbus TCP功能碼的特征,對其功能碼字段進行解析,實現基于白名單規則

2018-01-16 15:32:34 0

0 傳統的基于幾何區域分割的報文分類算法在空間切分時,通常只采用一種切分方法,并不會根據每個域的特點選取不同的對策.提出了一種采用混合切分法的報文分類算法HIC(hybrid intelligent

2018-02-24 14:06:31 0

0 語義主題,從語義層面計算用戶對各資源的偏好概率,將計算出的偏好概率與協同過濾算法計算出的資源相似度相結合,預測用戶偏好值,實現個性化推薦。在Movielens數據集上的實驗結果表明,與傳統基于標簽的推薦算法相比,該算法能消除標簽

2018-03-07 13:58:03 0

0 本系統采用了LATTICE的XP系列芯片,所用軟件為splever7.0,應用本軟件有一個新加功能,可以用FPGA的底層資源生成一個簡單CPU的框架,并且在軟件的庫里邊,有很多的模塊可以調用,例如GPIO接口,I2C接口等。本系統的設計使用的是I2C接口。

2020-03-12 08:03:00 1888

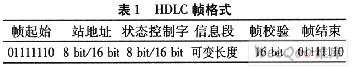

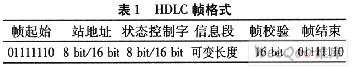

1888 它還具有設計開發周期短、設計制造成本低、可實時在線檢驗等優點,因此被廣泛用于特殊芯片設計中。本設計中采用Altera公司的EP2C70F672C8芯片來實現HDLC協議控制器。

2018-12-30 11:00:00 4456

4456

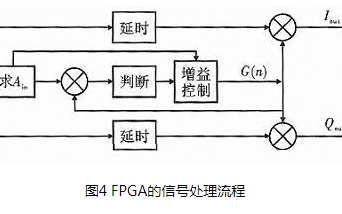

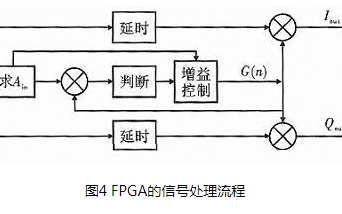

,采用AGC算法,可提高音頻信號系統和音頻信號輸出的穩定性,解決了AGC調試后的信號失真問題。本文針對基于實用AGC算法的音頻信號處理方法與FPGA實現,及其相關內容進行了分析研究。

2018-09-30 16:29:14 3573

3573

基于FPGA芯片Stratix II EP2S60F672C4設計實現了數字基帶預失真系統中的環路延遲估計模塊。該模塊運用了一種環路延遲估計新方法,易于FPGA實現。同時,在信號失真的情況下也能給

2018-12-19 11:04:26 2192

2192

高、資源敏感而計算時延要求并不高,這時我們需要一種保證計算正確且資源開銷最低的FPGA實現方法,本文給出了實現乘除法、開方運算的FPGA串行實現算法,并與LPM宏函數進行了性價比比較。結果表明,本文給出的各算法計算準確,資源量遠小于調用LPM宏函數。

2020-07-29 17:48:57 1835

1835

隨著深亞微米工藝的發展, FPGA 的容量和密度不斷增加,以其強大的并行乘加運算(MAC)能力和靈活的動態可重構性,被廣泛應用于通信、圖像等許多領域。但是在復雜算法的實現上,FPGA 不如嵌入式

2020-12-23 12:33:00 1

1 如何利用FPGA實現FFT算法,包括算法選取、算法驗證、系統結構設計、FPGA實現和測試整個流程。設計采用Good-Thomas算法,利用Verilog HDL描述的方式實現了不定點FFT系統,并以FPGA芯片virtex4為硬件平臺,進行了仿真、綜合、板級驗證等工作。仿真結果表明

2021-01-25 14:27:15 8

8 ,通過Quartus II 7.1的綜合與仿真,以及在EP2S60F1020C4 FPGA目標器件上的實現結果表明,該方法能夠有效地減少硬件資源的使用且滿足高速實時性的要求。

2021-03-23 15:44:54 31

31 摘要:在對FFT(快速傅立葉變換)算法進行研究的基礎上,描述了用FPGA實現FFT的方法,并對其中的整體結構、蝶形單元及性能等進行了分析。

2022-04-12 19:28:25 6618

6618 有些transceiver有PNC過濾功能,也可以在硬件上設置此過濾功能。針對NXP TJA1145 Transceiver而言,只能過濾通信速率在1Mbps的報文,因此要注意項目中的網絡管理報文

2022-08-23 12:09:08 6708

6708

目前,硬件實現FFT算法的方案主要有:通用數字信號處理器(DSP)、FFT專用器件和現場可編程門陣列(FPGA)。DSP具有純軟件實現的靈活性,適用于流程復雜的算法,如通信系統中信道的編譯

2023-05-11 15:31:41 3540

3540

簡介:北京革新創展科技有限公司GX-SOPC-EP2C35-M672FPGA開發板采用IntelCycloneII系列芯片,外圍提供豐富的通訊接口、連接器、開關、按鍵、配置與調試接口、存儲、LED、顯示、加速度傳感器、溫度傳感器、電源等,以及豐富的實驗項目資源。

2022-03-08 17:16:04 5

5 運算的運算步驟遠比定點運算繁瑣,運算速度慢且所需硬件資源大大增加,因此基于浮點運算的LMS算法的硬件實現一直以來是學者們研究的難點和熱點。 本文正是基于這種高效結構的多輸入FPA,在FPGA上成功實現了基于浮點運算的LMS算法。測試

2023-12-21 16:40:01 1590

1590 :?FPGA芯片采用了altera的Cyclon IV E系列的“EP4CE10F17C8”,軟件環境-Quartus-Ⅱ,采用的AD芯片為—AD-TLC549。 通過FPGA實現以下時序

2024-12-17 15:27:00 1613

1613

電子發燒友App

電子發燒友App

評論