按照一定的時間規律,向負載通斷電一次形成一個周期。反復執行便構成脈沖電源。脈沖電源有單正脈沖電源和雙正脈沖電源、負脈沖電源。

2011-12-19 10:38:33 10167

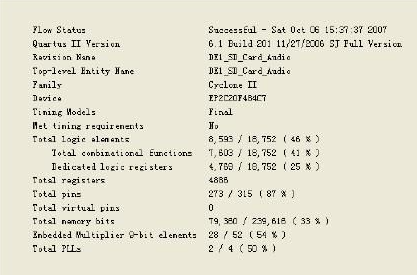

10167 為了研究數字化γ能譜儀,本文提出一種基于FPGA的數字核脈沖分析器硬件設計方案,該方案采用現場可編程邏輯部件(FPGA),完成數字多道脈沖幅度分析儀的硬件設計。用QuartusⅡ軟件在FPGA平臺上完成了數字核脈沖的幅度提取并生成能譜。

2013-11-21 10:57:26 2545

2545

本文介紹的FPGA的特殊電源要求,說明了如何設計這些聰明的芯片的電源,然后回顧了一系列的針對FPGA應用的電源模塊。

2015-11-24 18:01:01 1323

1323 極高的性能和密度,而且還針對器件總功率進行了優化,同時可以支持高達1 Gbps的高速差分I/O信號,因而是一款超快的FPGA。該芯片中所含的高性能嵌入式DSP塊的運行頻率高達370 MHz。另外Stratix II還有12個可編程PLL,并具有健全的時鐘管理和頻率合成能力。能實現最大的系統性能。

2020-12-10 11:42:00 1919

1919

本作品的設計意圖即在Nios. II處理器的平臺上實現我們研究提出的一種可行的,魯棒性高的算法,即利用我們實驗室研究的關于MRI Spine圖像分割算法實現了脊椎核磁共振矢狀圖(Sagittal

2021-04-15 14:16:16 5095

5095

復雜的片上系統 (SoC)。 這種復雜性對電源提出了苛刻的要求。為應對這些挑戰,電源需要多個輸出以及開關穩壓器的組合以提高效率和線性穩壓器以實現清潔電源。 本文描述了 FPGA 的特殊電源要求,解釋了如何為這些智能芯片設計電源,然后回顧了針對

2023-03-30 17:05:03 2753

2753

硬件連線:74ALVC164245芯片實現3.3V到5V的電平轉換,OE直接接地, DIR直接接3.3V電源,芯片A口接FPGA管腳,B口直接驅動達林頓管ULN2803ADW,FPGA管腳為常低

2024-12-16 08:39:34

{:soso_e141:}新手初學FPGA~有個問題......在安裝軟件時,安了這兩個軟件 nios ii 和 Quartus II{:soso_e136:}但后來認真看了一下,對這兩個軟件的區分

2012-09-12 21:51:30

本帖最后由 qlc111 于 2013-4-23 16:58 編輯

FPGA Nios II 視頻資料 特權 深入淺出FPGA + 特權和你一起學Nios II+黑金Nios II +一些資料存于百度網盤中,下面是下載地址:百度網盤下載地址

2013-04-22 21:54:16

FPGA實現高速FFT處理器的設計介紹了采用Xilinx公司的Virtex - II系列FPGA設計高速FFT處理器的實現方法及技巧。充分利用Virtex - II芯片的硬件資源,減少復雜邏輯,采用

2012-08-12 11:49:01

的缺點。

FPGA和CPU、GPU、ASIC的芯片等核心區別是其底層邏輯運算單元的連線及邏輯布局未固化,用戶可通過 EDA 軟件對邏輯單元和開關陣列編程,進行功能配置,從而去實現特定功能的集成電路芯片

2024-04-17 11:13:59

FPGA入門:Quartus II的安裝 本文節選自特權同學的圖書《FPGA/CPLD邊練邊學——快速入門Verilog/VHDL》書中代碼請訪問網盤:http://pan.baidu.com/s

2015-02-03 11:08:43

脈沖耦合神經網絡(PCNN)在FPGA上的實現,實現數據分類功能,有報酬。QQ470345140.

2013-08-25 09:57:14

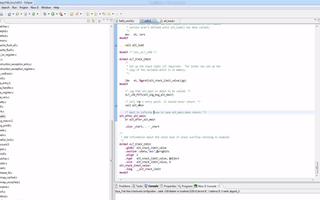

Quartus II的FPGA設計手冊。本使用手冊主要是針對使用Quartus Ⅱ 5.0軟件進行FPGA設計開發的常見的功能進行介紹。主要分以下幾個步驟:1. Quartus II 軟件的安裝步驟

2012-03-08 16:45:28

開關產生輸入信號,通過FPGA處理信號,最后FPGA把處理后的信號傳到電機,由電機來完成一系列的動作,如表1所示。所以其邏輯設計是實現智能的關鍵。結束硬件選型后,利用Quartus II搭建硬件原理圖

2014-12-04 15:43:23

FPGA內部有一個脈沖信號,通過output輸出,從而驅動labview采樣,用示波器發現 輸出管腳電壓一直是0.9V,沒有脈沖,后來將脈沖信號改為一個上升沿,示波器還是看不到電壓的變化,這是什么原因啊?load_i是脈沖信號,load_ii是上升沿,在輸出端都采不到。。。。

2017-06-01 22:51:20

`勇敢的芯伴你玩轉Altera FPGA連載77:基于SignalTap II的超聲波測距調試之SignalTap II調試特權同學,版權所有配套例程和更多資料下載鏈接:http

2018-06-14 20:10:38

基于FPGA的數字脈沖壓縮技術1.數字脈沖壓縮實現原理2.電路設計2.1APEX2OKE系列FPGA 簡介2.2 基于FPGA 的算法研究及實現 2.3 脈沖壓縮在FPGA 上的實現

2011-03-02 09:41:50

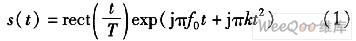

使用。 本文基于快速傅里葉IP核可復用和重配置的特點,實現一種頻域的FPGA數字脈壓處理器,能夠完成正交輸入的可變點LFM信號脈沖壓縮,具有設計靈活,調試方便,可擴展性強的特點。 1 系統功能硬件

2018-11-09 15:53:22

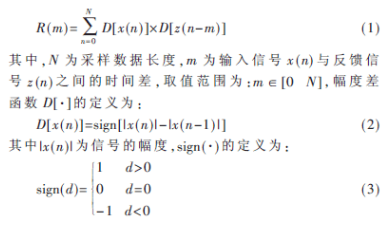

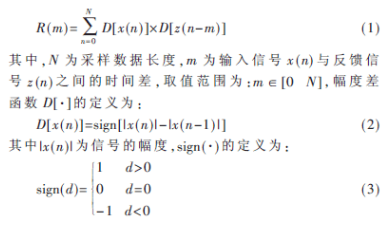

初相的目的。經后續能量歸一可以消除幅度不穩定造成的影響。所以經過DSU處理,可以消除或減小磁控管產生的發射脈沖幅相不穩定性。2 基于FPGA的DSU實現由于本雷達信號處理數據量大、實時性強、動態范圍

2015-02-05 15:34:43

http://115.com/file/ant54869#《基于VHDL的FPGA與NIOS_II實例精煉》第七章代碼.rarhttp://115.com/file/e7wphx31#《基于VHDL

2012-02-06 11:27:54

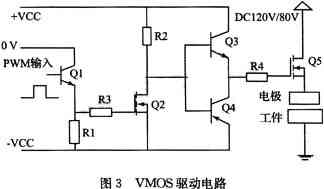

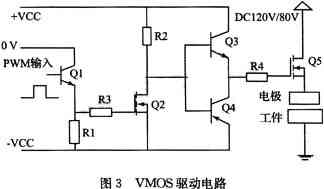

請教:我想把FPGA輸出的TTL脈沖信號放大,波形的特征是:信號周期100us,脈沖寬度100ns,上升時間不大于50ns。

信號如圖所示:

目前想采用的方案是:

FPGA輸出的脈沖信號通過

2024-09-13 08:13:39

準諧振原邊操控器;內置700V功率三極管,它為原邊反應工作形式,專利的“零電壓帶載發動”可完成芯片空載損耗。NC-Cap/PSR-II獲得優秀的EMI,無異音技能有用下降異音,該芯片供給了全面的智能

2019-12-05 17:12:01

可重構技術具有什么優點?怎么實現基于FPGA可重構智能儀器的設計

2021-05-06 06:44:38

怎么實現基于FPGA技術的智能導盲犬設計?

2021-05-08 07:37:31

你好!我對柏樹FX3是新的,我有一些問題。我找到了一個例子,說明了如何使用SPI在SelectMap模式下實現FPGA配置。是否可以使用GPIF II在FPGA從SelpDeMMAP模式中配置

2018-12-03 11:43:34

用電池單電源供電,如何實現正負脈沖輸出要輸出正負雙向的脈沖波形,是不是必須得用正負電源系統做?但是很奇怪我看到樣品并沒有用正負電源,只有一個電池供電,實現了如下的波形,是怎么做到的?有哪些好的方式?1.全橋驅動?如圖是否可以實現2.等幅波+調制?

2022-03-15 14:47:21

如題,請問各位大神如何將ucos ii/iii移植FPGA Nios ii。Altera的FPGA軟件里可以直接例化調用一個ucos,但要如何自己移植一個原版系統呢?

2019-11-06 23:17:44

請問怎么用FPGA(quartus II)實現微分,聽說是用D觸發器,但是不懂原理,求指教。。。

2013-08-11 18:29:39

學習一段時間FPGA,大約模糊的知道如果用FPGA實現跑馬燈得考慮硬件上到底怎么實現LED燈的狀態變換而用nios ii實現的時候,貌似是用軟件控制?不知道這種理解是否正確,還有有情大神可否講解一下FPGA實現與nios ii實現的本質區別?

2014-11-11 15:21:37

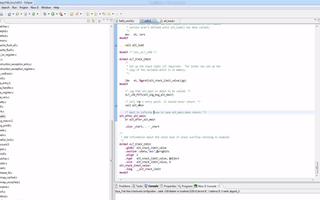

概括來說,FPGA的實現過程分為2步:分析綜合與布局布線。這一點,在Quartus II軟件中體現的尤為明顯。這是Quartus II軟件在編譯時的任務欄。紅框中的兩步,正是分析綜合與布局布線。而在

2021-07-26 07:20:45

Altera Quartus II 設計軟件提供完整的多平臺設計環境,能夠直接滿足特定設計需要,為可編程芯片系統(SOPC) 提供全面的設計環境。QuartusII 軟件含有 FPGA 和 CPLD 設計所有階段的

2009-04-21 23:09:59 22

22 This manual describes the Verilog portion of Synopsys FPGACompiler II / FPGA Express application

2009-07-23 09:59:06 21

21 基于PIC單片機的脈沖電源:設計了一種金屬凝固過程用脈沖電源。該電源采用PIC16F877作為主控芯片,實現對窄脈沖電流幅值的檢測,以及時電流脈沖幅值根據模糊PID算法進行閑環控

2009-10-10 14:30:27 65

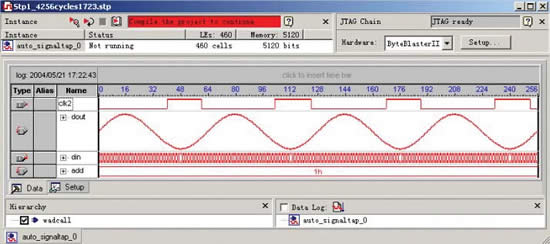

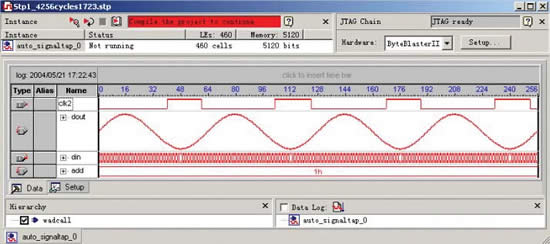

65 本文介紹了可編程邏輯器件開發工具Quartus II 中SingalTap II 嵌入式邏輯分析器的使用,并給出一個具體的設計實例,詳細介紹使用SignalTap II對FPGA調試的具體方法和步驟。關鍵字 : S

2009-11-01 14:49:39 45

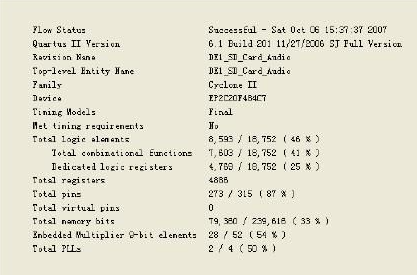

45 本文使用FPGA芯片來模擬實際的乒乓球游戲。本設計是基于Altera公司的FPGA Cyclone II芯片EP2C35的基礎上實現,運用Verilog HDL語言編程,在Quartus II軟件上進行編譯、仿真,最終在Altera公司的DE2

2010-02-24 14:51:17 88

88 本文使用FPGA芯片來模擬實際的乒乓球游戲。本設計是基于Altera公司的FPGA Cyclone II芯片EP2C35的基礎上實現,運用Verilog HDL語言編程,在Quartus II軟件上進行編譯、仿真,最終在Altera公司的DE2

2010-07-17 18:08:41 56

56 基于FPGA高速、可編程的優點,設計了一款可以靈活改變脈沖輸出周期和輸出個數的周期脈沖發生器。利用VHDL語言編寫了全部模塊,并在Altera公司提供的QuartusⅡ4.1開發軟件上實現了

2010-12-08 15:58:00 52

52

為解決雷達探測能力與距離分辨力之間的問題,在線性調頻信號脈沖壓縮的原理的基礎上,利用MATLAB軟件對數字脈沖壓縮算法進行仿真,給出一種基于FPGA分布式算法的

2010-12-24 16:10:59 37

37 Altera Cyclone II FPGA幫助Newtec實現了靈活的高性能雙向衛星寬帶終端在當今高速視頻下載和數據傳輸環境中,互聯網已經成為世界上很多家庭的日常工具。該技術雖然發展很快,但

2008-09-16 09:58:30 942

942 分立元件電路設計復雜,電路調試困難,基于單片機或者是32位的嵌入式CPU的脈沖電源性能有了很大的提高,也具有了很高的智能性,但對于不同的處理器

2009-02-12 15:49:32 1713

1713

FPGA的多路可控脈沖延遲系統設計

采用數字方法和模擬方法設計了一種最大分辨率為0.15 ns級的多路脈沖延遲系統,可以實現對連續脈沖信號的高分辨

2009-03-29 15:09:48 2975

2975

摘 要 :本文介紹了可編程邏輯器件開發工具Quartus II 中SingalTap II 嵌入式邏輯分析器的使用,并給出一個具體的設計實例,詳細介紹使用SignalTap II對FPGA調試的具體方

2009-06-20 10:42:18 1909

1909

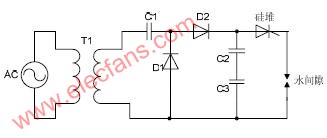

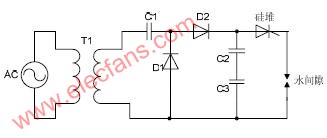

脈沖電源原理圖

等離子體電源采用脈沖電源供電,放電極直接置于水中,

2010-02-22 10:28:13 19677

19677

Altera 40-nm Arria II GX FPGA轉入量產

Altera公司今天宣布,開始量產發售40-nm Arria® II GX FPGA系列的第一款器件。Arria II GX器件系列專門針對3-Gbps收發器應用,為用戶提供了

2010-02-25 09:21:16 1265

1265 介紹了Arria II GX FPGA亮點,高速收發器特性,Arria II GX FPGA架構以及Arria II GX FPGA 開發套件主要特性,開發板方框圖,詳細的開發

2010-07-27 17:03:44 3465

3465

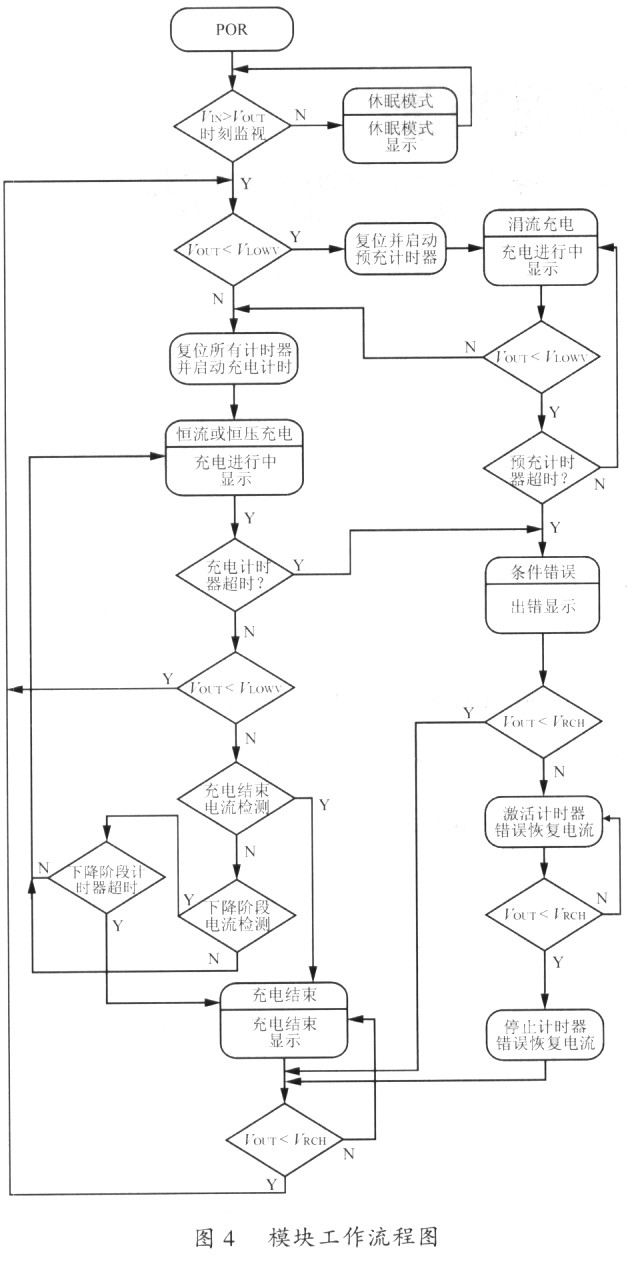

摘要:在分析了鋰離子電池的充電過程和bqTINY—II系列電源管理芯片功能特點的基礎上,設計出了一種以bq24020芯片為核

2010-12-23 16:59:30 1288

1288

要求改變脈沖周期和輸出脈沖個數的脈沖輸出電路模塊在許多工業領域都有運用。采用數字器件設計周期和輸出個數可調節的脈沖發生模塊是方便可行的。為了使之具有高速、靈活的優點,本文采用atelra公司的可編程芯片FPGA設計了一款周期和輸出個數可變的脈沖發生器

2011-01-20 13:40:28 6772

6772

本文提供的解決方案可防止FPGA設計被拷貝,即使配置比特流被捕獲,也可以保證FPGA設計的安全性。通過在握手令牌由MAX II器件傳送給FPGA之前,

2011-01-29 16:23:29 1628

1628

脈沖電源是一個應用很廣的技術領域。在粒子加速器裝置中的應用也已經有40多年的歷史。脈沖電源在加速器裝置中的功用主要有二個: 1.束流偏轉:激勵脈沖磁鐵,快速的偏轉運動的帶電粒子。實現束流的注入(injection)、引出(extraction)和剔除(dumping)等操作。

2011-02-18 16:28:35 71

71 首先分析了8PSK 軟解調算法的復雜度以及MAX算法的基本原理,并在Altera 公司的Stratix II 系列FPGA芯片上實現了此軟解調硬件模塊

2011-04-08 11:22:15 9209

9209

為了對運動控制系統中的脈沖進行精確控制以減少累計誤差,需要對脈沖進行分、倍頻和合成處理。介紹了通用的各種形式分頻器的實現方法,給出了在Altera公司的Cyclone II系列EP2C8Q208C8型

2011-06-13 16:53:56 66

66 用大多數FPGA都可以實現一個數字UWB(超寬帶)脈沖發生器。本設計可以創建一個兩倍于FPGA時鐘頻率的脈沖信號(

2011-09-06 11:59:48 6142

6142

在直流電氣傳動系統中使用的可控直流電源大部分是晶閘管相控整流電源,而晶閘管觸發脈沖形成單元是晶閘管相控整流系統的重要組成部分.該設計采用FPGA實現智能電力電子控制器的研

2011-10-17 17:12:13 73

73 為了對運動控制系統中的脈沖進行精確控制以減少累計誤差,需要對脈沖進行分、倍頻和合成處理。介紹了通用的各種形式分頻器的實現方法,給出了在Altera公司的CyclONe II系列EP2C8Q208C8型

2011-10-21 17:55:34 32

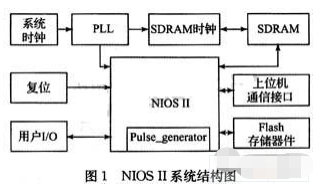

32 Nios II內核詳細實現

2012-10-17 13:59:49 83

83 本系統采用經濟型的Cyclone II FPGA芯片作為核心,基于Nios II軟核處理器,采用軟硬件結合的方式設計數碼相框并實現。

2013-01-08 11:07:15 9965

9965

Altera公司 (NASDAQ: ALTR)今天宣布推出Quartus? II軟件13.0版,這一軟件實現了性能最好的FPGA和SoC,提高了設計人員的效能。28 nm FPGA和SoC用戶的編譯

2013-05-07 14:30:30 4183

4183 針對脈沖耦合神經網絡(PCNN)具有神經元脈沖同步激發、適合硬件實現的特點,提出了一種基于FPGA的PCNN實時處理系統。系統設計了時鐘分頻、串口通信、串并轉換、PCNN結構和VGA顯示等功能

2015-12-21 10:16:24 6

6 NIOS_II各種性能表格對NIOS_II內核在各種型號的FPGA上的實現的性能說明

2015-12-21 17:19:15 22

22 dac0832ad08098259a,825382508255等芯片的fpga實現及仿真

2016-01-20 15:12:47 13

13 基于Quartus_II_的FPGACPLD開發。

2016-05-20 11:16:35 51

51 vhdl語法介紹FPGA設計實例nios ii設計實例北航版本

2016-07-14 17:34:13 74

74 FPGA II實戰演練V1.0,感興趣的小伙伴們可以瞧一瞧。

2016-11-17 11:43:16 7

7 FPGA II實戰演練V1.0,感興趣的小伙伴們可以瞧一瞧。

2016-11-05 14:48:04 12

12 FPGA-Quartus II各個器件源碼

2017-03-19 19:49:39 59

59 電子發燒友網站提供《基于FPGA的脈沖信號參數測量儀的設計與實現.pdf》資料免費下載

2017-05-27 08:00:00 85

85 針對半導體激光器 (LD)脈 沖驅動工作 的需要 ,提 出了一種 新型的基于 FPGA技術 的 LD脈沖驅動電源的設計方法。結合 FPGA技術 ,利用 日立 SH系列單片機 HD64F7045為控制

2017-11-09 17:28:02 31

31 脈沖電源是什么?用戶的負載需要斷續加電,即按照一定的時間規律,向負載加電一定的時間,然后又斷電一定的時間,通斷一次形成一個周期。如此反復執行,便構成脈沖電源。例如對于無極性電解電容器的老練工藝中

2017-11-14 17:31:16 34053

34053 介紹一種采用FPGA(現場可編程門陣列電路)實現SDH(同步數字體系)設備時鐘芯片設計技術,硬件主要由1 個FPGA 和1 個高精度溫補時鐘組成.通過該技術,可以在FPGA 中實現需要專用芯片才能實現的時鐘芯片各種功能,而且輸入時鐘數量對比專用芯片更加靈活,實現該功能的成本降低三分之一.

2017-11-21 09:59:00 2653

2653

針對無線廣播系統對高精度的同步頻率信號的需求,設計一種基于AD9548芯片的鎖定CJPS秒脈沖的頻率源系統。分析了AD9548鎖相頻率合成器的基本原理以及工作特性,采用FPGA+AD9548芯片

2017-12-07 11:10:46 2

2 觀看這一視頻演示,了解Stratix? II GX FPGA是怎樣幫助您任意改變背板卡的位置,同時全面保持信號完整性不變的。利用Stratix II GX FPGA的即插即用信號完整性技術,您不

2018-06-22 03:56:00 2999

2999 、功耗與實時性要求都很高的實時SAR成像系統,其應用十分廣泛。在整個有距離-多普勒(R-D)算法中方位脈沖壓縮系統是設計的關鍵。隨著FPGA芯片突飛猛進的發展,實時雷達成像方位脈沖壓縮系統在FPGA上實現變成了可能。

2018-12-30 11:10:00 5100

5100

關鍵詞:Quartus , FPGA , Stratix 與以前的版本相比,只需要一半的時間就能實現業界性能最好的設計 Altera公司今天宣布推出Quartus II軟件13.0版,這一軟件實現了

2018-09-25 09:12:01 1542

1542 關鍵詞:FPGA , SignalTap 一、為啥別忘了我 嵌入式邏輯分析儀—SigbalTap II,是Altera Quartus II 自帶的嵌入式邏輯分析儀,與Modelsim軟件仿真

2018-10-01 15:30:01 1201

1201 Stratix II是ALTERA公司生產的一款高性能FPGA器件。它采用TSMC的90 nm低k絕緣工藝技術生產,等價邏輯單元(LE)高達180 k,嵌入式存儲器容量達到9 MB。該器件不但具有

2018-10-24 14:45:14 1

1 基于FPGA芯片Stratix II EP2S60F672C4設計實現了數字基帶預失真系統中的環路延遲估計模塊。該模塊運用了一種環路延遲估計新方法,易于FPGA實現。同時,在信號失真的情況下也能給

2018-12-19 11:04:26 2192

2192

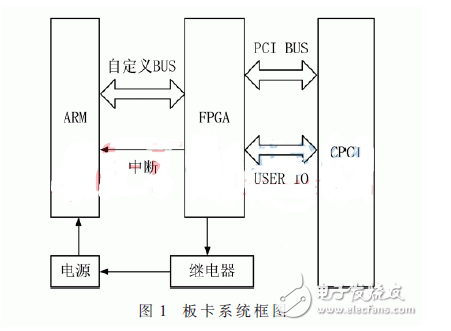

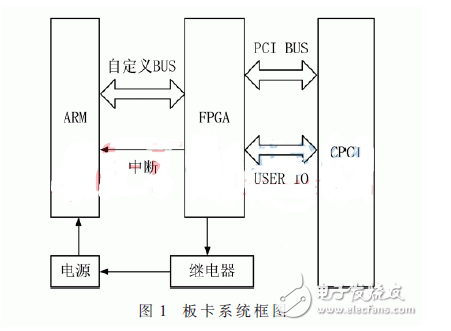

本文提出了一種基于FPGA的CPCI系統的設計和實現,使用廉價FPGA芯片實現CPCI通信協議,同時利用FPGA的可編程特性實現電源控制、靈活中斷、外部觸發、外部通信等特殊應用的功能,解決了CPCI協議經過CPCI橋時的沖突問題。

2019-01-06 11:37:13 3401

3401

本文檔的主要內容詳細介紹的是FPGA視頻教程之如何使用NIOS II處理器詳細資料免費下載。

2019-03-20 14:35:26 6

6 1.1兆比特的嵌入式內存。Cyclone II FPGA采用臺積電90納米低K介電工藝在300毫米晶片上制造,以確保快速可用性和低成本。通過最小化硅區,Cyclone II設備可以在單個芯片上支持復雜

2019-03-25 08:00:00 15

15 Nios II系列軟核處理器是Altera的第二代FPGA嵌入式處理器,其性能超過200DMIPS,在Altera FPGA中實現僅需35美分。Altera的Stratix 、Stratix GX

2019-09-26 07:00:00 2027

2027

Nios II系列軟核處理器是Altera的第二代FPGA嵌入式處理器,其性能超過200DMIPS,在Altera FPGA中實現僅需35美分。Altera的Stratix 、Stratix GX

2019-09-25 07:09:00 2849

2849

研制了基于現場可編程門陣列 (FPGA)實現的、用于± 50 0 kvar靜止補償器 (STATCOM)的 PWM脈沖發生器。該脈沖發生器通過接口單元接收 DSP寫入的 PWM脈沖寬度數據 ,然后

2020-01-07 11:15:43 24

24 Quartus II軟件為使用Altera?FPGA和CPLD設備進行設計的系統設計師提供了一個完整的軟件解決方案。Quartus II程序員是Quartus II軟件包的一部分,它允許您編程

2020-09-17 14:41:00 34

34 在本輔導教材中,將重點講解如何將一個設計項目物理地實現于FPGA 芯片中。我們將展示如何用手工的方法選擇器件封裝的引腳,并且把這些引腳用做電路的輸入和輸出信號,此外還將描述如何使用Quartus II 編程器模塊把編譯完的電路傳送到所選擇的FPGA芯片中。

2020-10-27 16:26:00 20

20 本文檔的主要內容詳細介紹的是使用FPGA實現PWM電源的程序和工程文件免費下載。

2021-01-19 15:53:24 5

5 片多通道高速串行ADC用于X射線脈沖信號的采集,利用數字電位計及高壓電源模塊實現探測器偏置電壓的精細調節,利用數據存儲校正電路等完成采集數據的校正處理,并可通過圖像傳輸電路完成圖像數據的傳輸與顯示以及系統功能的調試。與上位

2021-06-01 09:37:44 17

17 FPGA_ASIC-S698MSoC芯片中EDAC模塊的設計與實現(第四屆星載電源技術學術研討會)-該文檔為FPGA_ASIC-S698MSoC芯片中EDAC模塊的設計與實現總結文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-09-15 11:05:19 6

6 FPGA-SoC芯片中EDAC模塊的設計與實現(深圳市宇衡源電源技術)-該文檔為FPGA-SoC芯片中EDAC模塊的設計與實現簡介文檔,是一份還算不錯的參考文檔,感興趣的可以下載看看,,,,,,,,,,,,,,,,,

2021-09-27 14:32:18 13

13 本篇主要介紹Xilinx FPGA的電源設計,主要包括電源種類、電壓要求、功耗需求,上下電時序要求,常見的電源實現方案等。

2022-10-17 17:43:39 8052

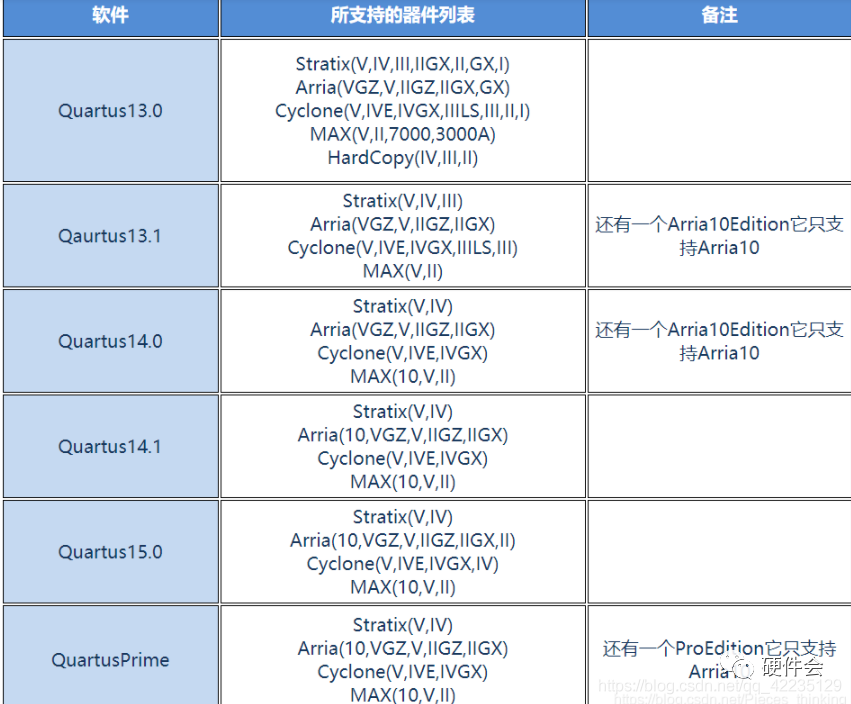

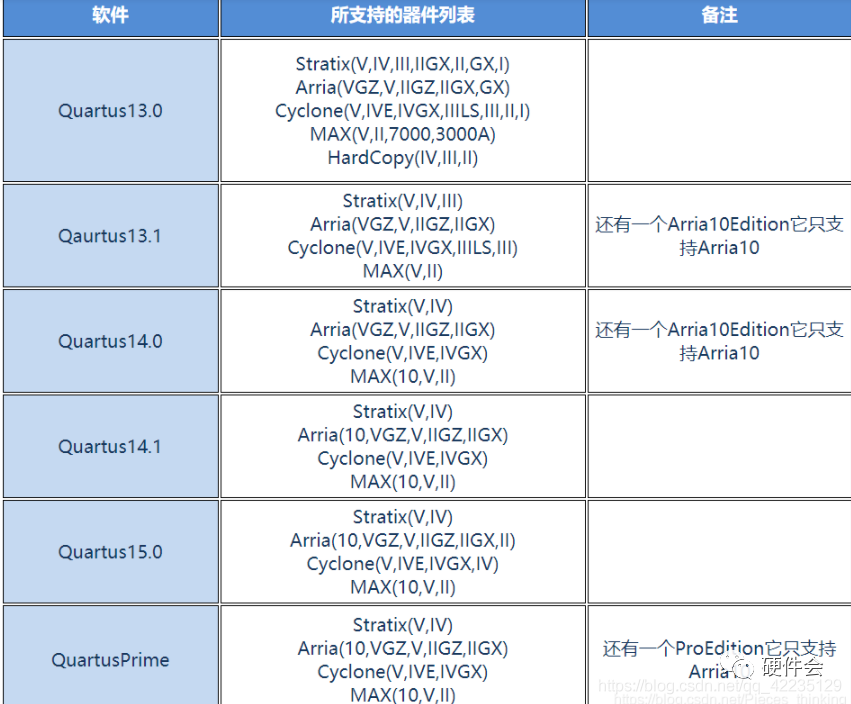

8052 用Quartus II開發ALTERA的FPGA時,有時候會發現沒有自己對應的芯片型號

2023-07-24 15:15:40 17833

17833

FPGA芯片和人工智能芯片(AI芯片)在設計和應用上存在一些關鍵的區別,這些區別主要體現在它們的功能、優化目標和適用場景上。

2024-03-14 17:26:02 2490

2490 隨著科技的發展和制造業對高品質、高精度焊接需求的增長,精密脈沖焊接技術在工業生產中的地位愈發重要。本文將深入探討高性能精密脈沖焊接電源的應用及其在實際工程中的實現路徑。

一、引言

精密

2024-11-16 09:27:12 1484

1484 概述:?利用FPGA實現AD芯片的時序,進一步實現與AD芯片數據的交互,主要熟悉FPGA對時序圖的實現,掌握時序圖轉換Verilog硬件描述語言技巧后與其它芯片進行數據的交互也是類似的。 說明

2024-12-17 15:27:00 1613

1613

電子發燒友App

電子發燒友App

評論