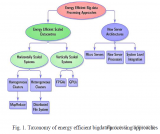

本文從硬件加速的視角考察深度學習與FPGA,指出有哪些趨勢和創新使得這些技術相互匹配,并激發對FPGA如何幫助深度學習領域發展的探討。

2016-03-24 13:41:06 2819

2819 大小調整,另一種使用Xilinx xfopencv library實現了在FPGA上硬件加速的圖像大小調整。 初始化 1. 首先在SD卡內配置Pynq-Z2最新鏡像PYNQ image v2.5并燒錄

2020-11-19 15:29:43 4206

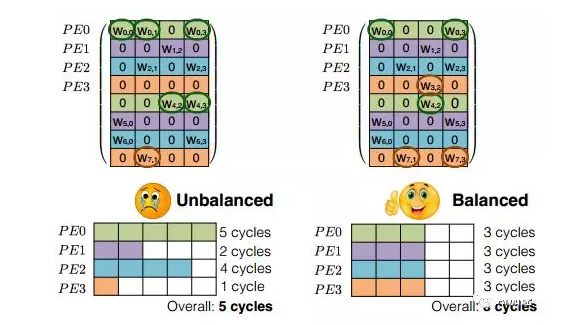

4206 的應用于語音識別、機器翻譯、手寫識別等。LSTM涉及到大量的矩陣乘法和向量乘法運算,會消耗大量的FPGA計算資源和帶寬。為了實現硬件加速,提出了稀疏LSTM。核心是通過剪枝算法去除影響較小的權重,不斷迭代訓練以達到目標函數收斂。參與實際運算的權重數量大大縮減,這可以有效降低FPGA計算資源

2020-11-29 11:24:19 4160

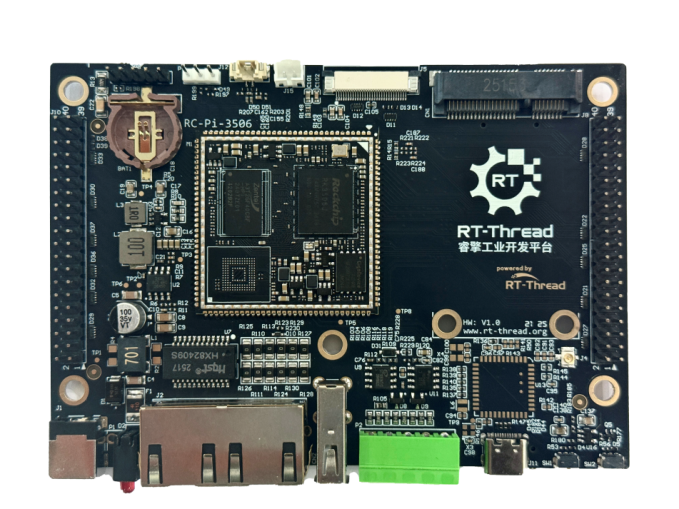

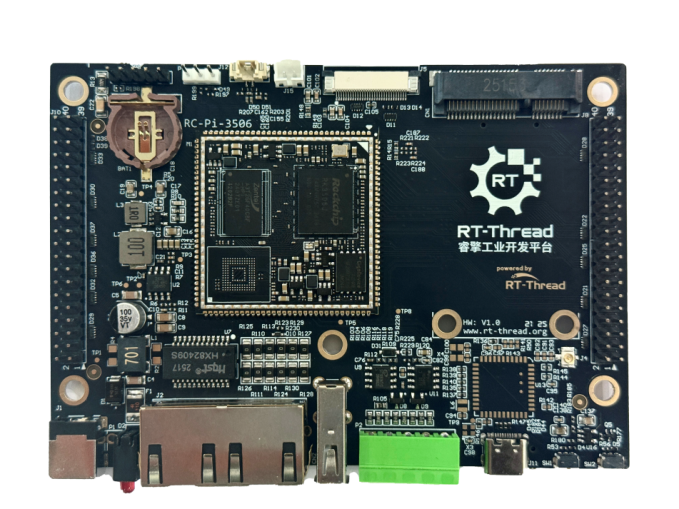

4160 )。AMP模式下虛擬網卡驅動支持,雙系統通信更加便利,更完善的Perfetto多核性能調試工具,AIUVC人臉識別示例,優化LVGL支持硬件加速等。并提供對應的教

2025-09-29 17:36:55 9961

9961

利用硬件模塊來替代軟件算法以充分利用硬件所固有的快速特性(硬件加速通常比軟件算法的效率要高),從而達到性能提升、成本優化目的,當前主要是如下兩大加速方式:FPGA 現場可編程門陣列,可針對某個具體的軟件

2017-12-29 11:25:28

突破40%;數據中心加速卡市場復合增長率達34%......

2. 萬億級市場的四大賽道1) 智能駕駛新基建:單輛L4自動駕駛車搭載12-16片FPGA;動態可重構技術實現毫秒級算法切換

2025-03-03 11:21:28

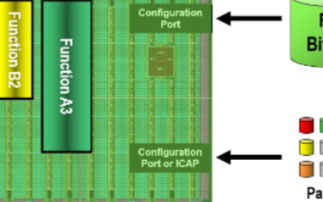

可重構設計是指利用可重用的軟、硬件資源,根據不同的應用需求,靈活地改變自身體系結構的設計方法。FPGA器件可多次重復配置邏輯的特性使可重構系統成為可能,使系統兼具靈活、便捷、硬件資源可復用等性能

2011-05-27 10:22:36

較低的單位成本。

性能和功耗 :由于ASIC是針對特定應用定制的,因此其性能和功耗通常優于FPGA。然而,隨著技術的進步,一些高端FPGA也能達到與ASIC相當的性能水平。

可擴展性 :FPGA的可

2024-02-22 09:54:36

使用FPGA可以提供定制化的硬件加速方案。通過將算法映射到FPGA的硬件邏輯上,可以實現遠超軟件實現的性能提升。

2024-07-29 15:45:40

是90nm的1.2 V器件,與先前產品相比可降低靜態和動態功耗,且FPGA制造商采用不同的設計技術進一步降低了功耗,平衡了成本和性能。這些90nm器件都改變了門和擴散長度,優化了所需晶體管的開關速率

2015-02-09 14:58:01

嗨,我目前正在尋找一個平臺,它可以將相機的輸入提供給FPGA,在那里我可以進行一些硬件加速圖像處理。我需要一個能夠以像素為單位輸入FPGA的camrea,然后FPGA可以處理像素。我已經找到

2020-04-14 10:05:14

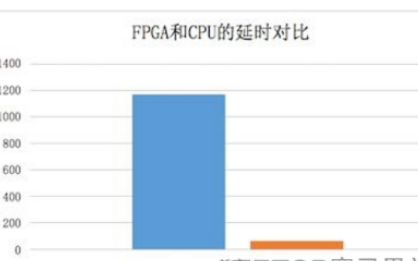

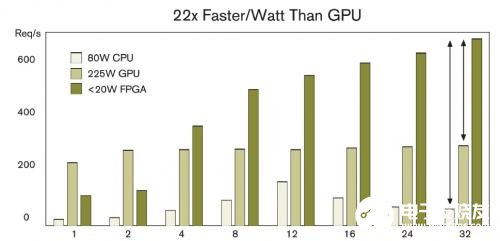

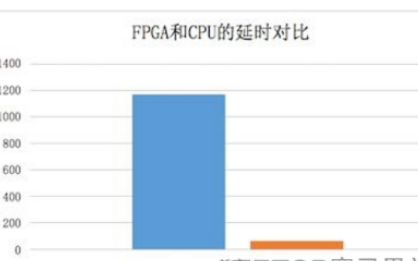

提升至通用CPU服務器的30倍以上。同時,與已經深入人心的高性能計算的代表GPU相比,FPGA具有硬件可編程、低功耗、低延時的特性,代表了高性能計算的未來發展趨勢。而在人工智能(AI)里面火熱的深度學習

2017-04-15 16:17:41

1. 如何實現FPGA局部動態加載。2. pcie部分不變,實現部分程序加載。3. 目前是通過JTAG線,通過PCIE加載的FPGA程序。4. 現在是想通過更改bin文件,不通過JTAG的方式加載。

2021-03-08 09:32:33

的Enpirion的ED8101P0xQI單相數字控制器,可實現對FPGA的多種遠程監視和低功耗特性。 5.提前規劃電源樹,整體布局優化系統功耗 系統硬件設計會影響設計的復雜程度、周期和成本,因此,盡早規劃

2018-10-23 16:33:09

,允許采用動態電壓和頻率調節技術來降低系統整體實際功耗。提供可選擇的1.2V和1.5V的I/O和核電壓,以方便用戶平衡設計的性能和功耗之間的關系。IGLOO的時鐘結構可以沒有副作用的對全局信號和局部信號進行門控制。另外IGLOO的RAM模塊具有LP和F*F端口來控制RAM本身的靜態功耗。

2020-05-13 08:00:00

硬件加速模塊需要四個時鐘,分別為clk_l , clk_r , clk_c , clk_n 。

clk_l : 整個硬件加速模塊為了最大化的節約時間成本而采用了類似處理器的流水線設計,具體上將每一層

2025-10-23 07:28:15

得Morph-IC-II成為必須透過 USB下載新軟件以重新動態配置硬件功能的理想應用選擇。此外,除了提高應用的靈活性,透過USB重新配置硬件也可降低BOM成本, FPGA只需為最復雜的分離功能而不是所有功能來設定大小。

2019-07-03 08:29:05

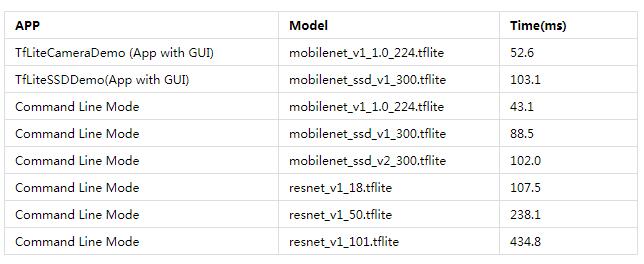

(NNAPI) ,充分調用神經網絡API進行硬件加速,使RK3399的AI運算性能大幅提升。適用基于主流模型架構衍生開發的各類應用,例如:商品識別、疲勞檢測等。 2分鐘視頻,一起了解下Android

2018-07-31 17:42:44

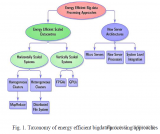

算法的軟件實現方式非常低效,所以業界對GNN的硬件加速有著非常迫切的需求。我們知道傳統的CNN(卷積神經網絡網絡)硬件加速方案已經有非常多的解決方案;但是,GNN的硬件加速尚未得到充分的討論和研究,在

2021-07-07 08:00:00

H.264解碼器中CABAC硬件加速器怎么實現?

2021-06-07 06:48:58

的記憶體資源可 以因硬件加速整合減少至少10%。 當然,從目的性來看,不管MCU有無整合FPU硬件加速單元,浮點運算需求使用MCU現有的運算能力也 能得出結果,只是前提是計算過程會耗用較多運算時間

2016-10-14 17:17:54

。 使用 MCUBoot 驗證兩個應用程序時,運行時間大約需要五秒鐘。

在 README.md 的 \"安全 \"一欄中寫道

與軟件實現相比,硬件加速加密技術將啟動時間縮短了四倍多

2024-05-29 08:17:06

%。 五、散熱系統 采用無風扇被動式散熱。 六、應用領域 FPGA硬件加速。 七、接口測試軟件DDR4 數據速率2400Mb/s IP測試。 PCIe 3.0 x8 IP測試。 程序加載測試。

2019-10-25 16:00:50

項目名稱:圖像目標識別FPGA硬件加速試用計劃:申請理由 本人供職于一家AI公司,現在在使用FPGA硬件加速相關目標檢測算法的端側實現(鑒黃/司機行為識別),公司已經有非常成熟的軟件算法以及GPU

2019-01-09 14:51:09

hardware_accelerator_done; // 硬件加速器完成信號(假設)

// FPGA內部處理函數

always @(posedge clk or posedge reset) begin

2024-02-22 09:49:01

我想進入硬件加速。什么板對此有好處,為什么?

2019-10-10 07:00:38

大幅提升。eFPGA方案下SoC可實現高效運行,一方面迅速更新升級以支持新接口標準,另一方面可快速接入新功能以應對細分化市場需求。3、更節能:SoC設計嵌入eFPGA技術可在提高總性能的同時降低總功耗

2021-07-04 08:30:00

大幅提升。eFPGA方案下SoC可實現高效運行,一方面迅速更新升級以支持新接口標準,另一方面可快速接入新功能以應對細分化市場需求。3、更節能:SoC設計嵌入eFPGA技術可在提高總性能的同時降低總功耗

2021-07-04 08:30:00

(FPGA)來構建硬件加速電路,來提升計算CNN的性能。

其中 ASIC 具備高性能、低功耗等特點,但 ASIC 的設計周期長,制造成本高,而 GPU 的并行度高,計算速度快,具有深度流水線結構,非常

2023-06-20 19:45:12

散熱。六、應用領域FPGA硬件加速。七、接口測試軟件DDR4 數據速率2400Mb/s IP測試。PCIe 3.0 x8 IP測試。程序加載測試。北京太速科技有限公司在線客服:QQ:448468544公司網站:www.orihard.com聯系電話:***

2018-07-27 16:49:30

。 紋波:≤10%。 五、散熱系統 采用無風扇被動式散熱。 六、應用領域 FPGA硬件加速。 七、接口測試軟件DDR4 數據速率2400Mb/s IP測試。 PCIe 3.0 x8 IP測試。 程序加載測試。

2018-08-22 17:31:55

從工藝選擇到設計直至投產,設計人員關注的重點是以盡可能低的功耗獲得最佳性能。Altera在功耗和性能上的不斷創新,那其28nm高端FPGA如何實現功耗和性能的平衡?具體有何優勢?

2019-09-17 08:18:19

本文提出的通過微處理器加FPGA結合串行菊花鏈實現可重構的方式,實現了動態可重構FPGA結構設計的一種應用。

2021-05-10 06:22:19

,GPU和GDDR之間的數據交換非常頻繁。而DDR內存專注于與CPU進行數據交換的效率,因此對于整體存取性能、低延遲更為看重,所以在CPU和傳統的FPGA中基本都是用DDR4。隨著硬件加速需求對于

2021-12-21 08:00:00

,其算法的軟件實現方式非常低效,所以業界對GNN的硬件加速有著非常迫切的需求。我們知道傳統的CNN(卷積神經網絡網絡)硬件加速方案已經有非常多的解決方案;但是,GNN的硬件加速尚未得到充分的討論和研究

2020-10-20 09:48:39

的功耗取決于FPGA芯片及硬件設計本身,很難有較大的改善。可以優化是第3部分功耗:設計動態功耗,而且這部分功耗占總功耗的90%左右,因此所以降低設計動態功耗是降低整個系統功耗的關鍵因素。上面也提到過功耗

2014-08-21 15:31:23

也因而開始轉向采用加速器來滿足低時延、高吞吐量的需求,同時保持合理的功耗水平。 賽靈思FPGA所提供的功耗效率讓加速器能部署于整個數據中心,而且可將單位功耗性能比提升10-20倍。百度優化的FPGA

2016-12-15 17:15:52

Gzip的CPU消耗,讓出來的CPU就可以用于處理更多請求和提升性能。然而目前業內各大公司接入層針對于Gzip采用硬件加速還是一片空白,阿里在接入層結合硬件加速技術卸載Gzip調研了幾套方案:方案一是

2018-06-04 17:07:55

的高性能FPGA計算加速卡。作為基于服務器的PCI Express數據采集、處理、存儲設備,該板卡可以實現2通道萬兆光纖網絡數據的高速采集、實時處理、實時記錄和寬帶回放,強大的FPGA處理性能,可以實現

2016-03-04 11:13:54

的高性能FPGA計算加速卡。作為基于服務器的PCI Express數據采集、處理、存儲設備,該板卡可以實現2通道萬兆光纖網絡數據的高速采集、實時處理、實時記錄和寬帶回放,強大的FPGA處理性能,可以實現

2016-03-11 11:07:39

的高性能FPGA計算加速卡。作為基于服務器的PCI Express數據采集、處理、存儲設備,該板卡可以實現2通道萬兆光纖網絡數據的高速采集、實時處理、實時記錄和寬帶回放,強大的FPGA處理性能,可以實現

2016-03-18 11:16:02

的高性能FPGA計算加速卡。作為基于服務器的PCI Express數據采集、處理、存儲設備,該板卡可以實現2通道萬兆光纖網絡數據的高速采集、實時處理、實時記錄和寬帶回放,強大的FPGA處理性能,可以實現

2016-03-25 11:34:03

的高性能FPGA計算加速卡。作為基于服務器的PCI Express數據采集、處理、存儲設備,該板卡可以實現2通道萬兆光纖網絡數據的高速采集、實時處理、實時記錄和寬帶回放,強大的FPGA處理性能,可以實現

2016-04-01 10:53:42

的高性能FPGA計算加速卡。作為基于服務器的PCI Express數據采集、處理、存儲設備,該板卡可以實現2通道萬兆光纖網絡數據的高速采集、實時處理、實時記錄和寬帶回放,強大的FPGA處理性能,可以實現

2016-04-11 14:45:24

的高性能FPGA計算加速卡。作為基于服務器的PCI Express數據采集、處理、存儲設備,該板卡可以實現2通道萬兆光纖網絡數據的高速采集、實時處理、實時記錄和寬帶回放,強大的FPGA處理性能,可以實現

2016-04-18 14:12:57

的高性能FPGA計算加速卡。作為基于服務器的PCI Express數據采集、處理、存儲設備,該板卡可以實現2通道萬兆光纖網絡數據的高速采集、實時處理、實時記錄和寬帶回放,強大的FPGA處理性能,可以實現

2016-04-27 11:51:14

提升小波的FPGA實現

2009-05-08 17:23:38 9

9 可編程邏輯芯片特別是FPGA的快速發展,使得新的芯片能夠根據具體應用動態地調整結構以獲得更好的性能,這類芯片稱為動態可重構FPGA芯片(DRFPGA)。然而,使用這類芯片構建的

2010-01-18 08:40:35 10

10 FPGA的全局動態可重配置技術主要是指對運行中的FPGA器件的全部邏輯資源實現在系統的功能變換,從而實現硬件的時分復用。提出了一種基于System ACE的全局動態可重配置設計方法,

2011-01-04 17:06:01 54

54 針對復雜算法中矩陣運算量大, 計算復雜, 耗時多, 制約算法在線計算性能的問題, 從硬件實現角度, 研究基于FPGA/Nios-Ⅱ的矩陣運算硬件加速器設計, 實現矩陣并行計算。首先根據矩陣運算

2011-12-06 17:30:41 89

89 針對調制樣式在不同環境下的變化,采用了FPGA部分動態可重構的新方法,通過對不同調制樣式信號的解調模塊的動態加載,來實現了不同環境下針對不同調制樣式的解調。這種方式比傳

2012-06-18 13:42:13 33

33 電子發燒友網核心提示: 獲獎的Nios II 嵌入式處理器C語言至硬件(C2H)加速編譯器將對時間要求較高的ANSI C函數轉換為FPGA中的硬件加速器,從而提高了性能。 特性: (1)ANSI/ISO C 代碼按鍵

2012-10-17 14:29:34 2394

2394

這是必然趨勢,肯定有人會通過云訪問 FPGA 硬件加速功能。 Bitfusion 既開發軟件,又設計硬件,并且與 Rackspace 協作共同創建專用于加速云計算的數據中心。這一理念與 FPGA

2017-02-08 19:48:30 467

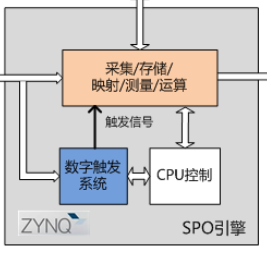

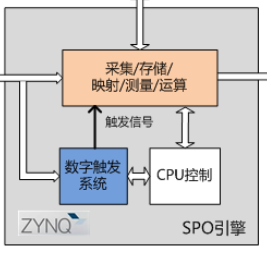

467 Xilinx Zynq-7000 全可編程 SoC (AP SoC) 系列集成 ARM處理器的軟件可編程性與 FPGA 的硬件可編程性,不僅可實現重要分析與硬件加速,同時還在單個器件上高度集成 CPU、DSP、ASSP 以及混合信號功能。

2017-11-07 14:37:52 8532

8532

的FPGA 快速動態重構方案, 實現了同一硬件平臺下多個FPGA 設計版本的在線動態配置和功能重構, 該技術已在工程中成功應用。

2017-11-22 07:55:01 1476

1476

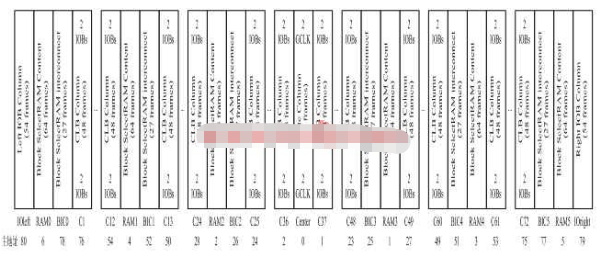

的應用。在主流的FPGA中,絕大多數都采用了SRAM來存放配置數據,稱為SRAM FPGA。這種FPGA的突出優點是可以進行多次配置。通過給FPGA加載不同的配置數據,即可令其實現不同的邏輯功能.FPGA這種可重配置的能力將給數字系統的設計帶來很大的方便。

2018-07-18 12:50:00 3395

3395

FPGA的不同配置電路功能,在不同時段執行不同的算法,實現了虛擬硬件可重構計算技術。這里提出的通過微處理器加FPGA結合串行菊花鏈實現可重構的方式,實現了動態可重構FPGA結構設計的一種應用。

2017-11-25 10:20:01 14505

14505

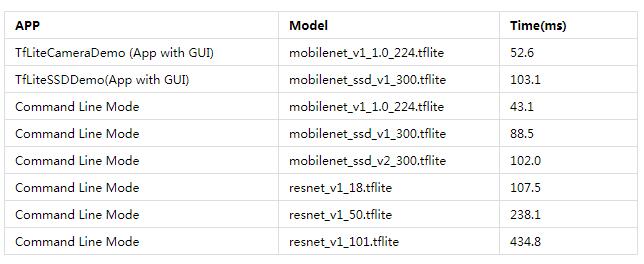

。該開發板加載了Linux Ubuntu操作系統,可以在CPU上運行現有的Python CNN架構如Caffe和Theano。本設計旨在用PYNQ加載的ZYNQ FPGA對于CNN核心計算進行硬件加速

2018-06-29 07:55:00 5289

5289

處理器內部集成的硬件加速器可以實現三種廣泛使用的信號處理操作:FIR(有限沖激響應)、IIR(無限沖激響應)和FFT(快速傅里葉變換)。硬件加速器減輕了核處理器的負擔,能潛在的提升處理器的計算吞吐率

2017-12-04 15:22:36 1766

1766 (Field Programming Gate Array, FPGA)。可重構系統非常適合于那些對功耗有嚴格要求或者計算密集的應用,因為此類應用在FPGA上實現的功耗要大大低于在處理器上實現的功耗

2018-07-11 11:20:00 2549

2549

高性能硬件加速的資產模擬與FPGA

2018-01-30 16:14:29 15

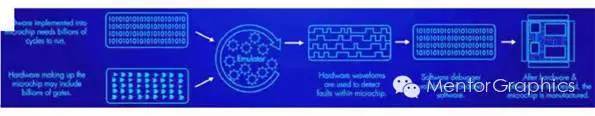

15 使用完全脫節。本白皮書將解釋說明,使用真實的有效載荷為何對于準確估算功耗和執行優化任務而言至關重要。之后,我們將會展示Veloce~客戶如何使用硬件加速仿真來實現可靠性高得多的使用模型,并且利用這一模型,可以更可靠地

2018-03-01 11:42:42 0

0 。采用英特爾 Arria 10 GX FPGA 的英特爾可編程加速卡是該系列中的第一張卡,可輕松插入任何基于英特爾至強處理器的服務器,在提升性能的同時,將復雜的數據密集型應用的功耗降至最低,包括 AI 推理、視頻流分析和數據庫加速等。

2018-05-18 06:31:00 2687

2687

硬件編程,可將性能提升至通用CPU服務器的30倍以上。同時,與已經深入人心的高性能計算的代表GPU相比,FPGA具有硬件可編程、低功耗、低延時的特性,代表了高性能計算的未來發展趨勢。 而在人工智能(AI)里面火熱的深度學習領域,企業同樣可以將FPGA用于深度學習的

2018-05-29 13:44:24 5789

5789

在近日舉行的2018上海世界移動大會期間,中國電信、英特爾、聯想與賽特斯聯合發布了基于FPGA的一系列vBRAS解決方案,包括vBRAS IPv6方案、vBRAS P4方案、vBRAS FPGA硬件加速解決方案。

2018-08-14 16:20:36 1377

1377 FPGA有多種配置/加載方式。粗略可以分為主動和被動兩種。主動加載是指由FPGA控制配置流程,被動加載是指FPGA僅僅被動接收配置數據。

2018-10-05 10:12:00 19146

19146 本教程討論基于Xilinx FPGA的Memcached硬件加速器的技術細節,該硬件加速器可為10G以太網端口提供線速Memcached服務。

2018-11-27 06:41:00 4243

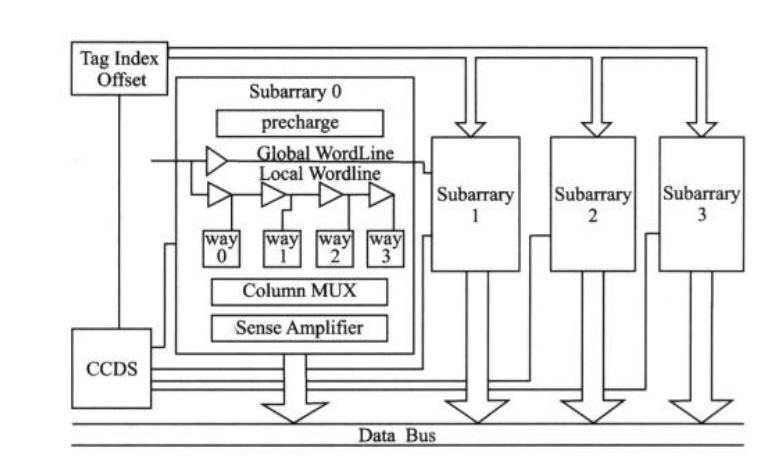

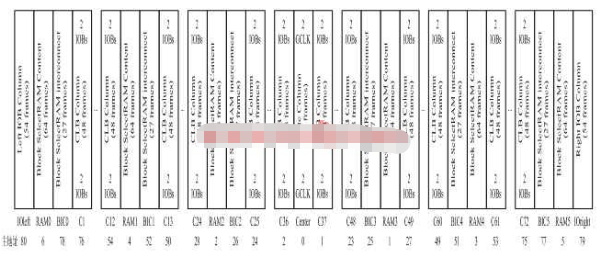

4243 FPGA 動態局部可重構技術中基于三態緩沖器( Tri2state Buffer ,TBUF) 總線宏結構的基礎上,采用Xilinx ISE FPGA Editor 可視化的方法實現總線宏的設計,并借助可重構硬件平臺———XCV800 驗證板,通過設計動態可重構實驗,論證總線宏設計的正確性。

2018-12-14 14:27:35 3

3 FPGA是加速許多類型計算工作負載的出色平臺,特別是那些數據通路適用于大規模并行運算的工作負載。FPGA可以通過在硬件中實現重要的計算密集算法塊來減少傳統處理器,從而大幅減少延遲和(通常更重要的)功耗。

2018-12-22 14:12:39 858

858 和網絡加速應用而設計的,并基于Speedster22i FPGA系列相同的高性能架構,采用Speedcore作為硬件加速器的方案被廣泛應用到數據中心和通信基礎設施等領域。據了解,eFPGA IP授權業務

2018-12-23 16:29:40 5164

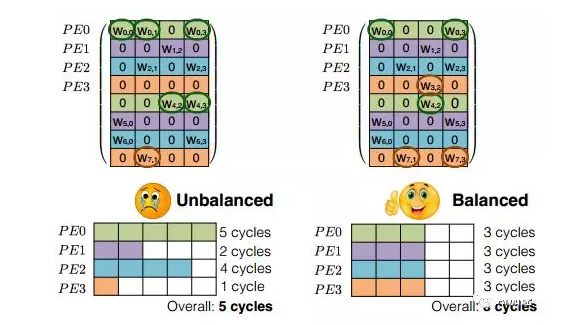

5164 網上對于FPGACNN加速的研究已經很多了,神經網絡的硬件加速似乎已經滿大街都是了,這里我們暫且不討論誰做的好誰做的不好,我們只是根據許許多多的經驗來總結一下實現硬件加速,需要哪些知識,考慮哪些因素。

2019-02-14 14:25:46 1546

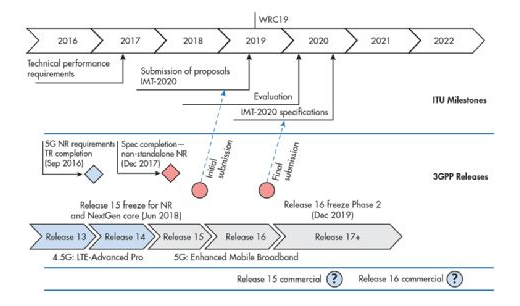

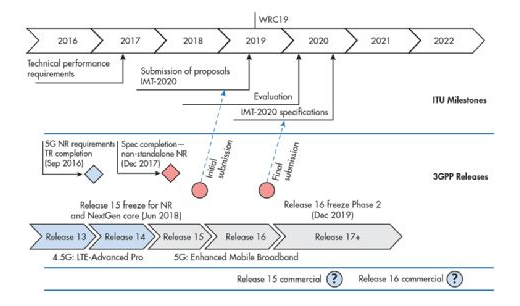

1546 我們考慮如何通過具有高性能CPU子系統和包括FPGA可重編程加速硬件處理單元的SoC架構來成功應對5G的獨特需求。

2019-04-28 15:50:24 1622

1622

本文從硬件加速的視角考察深度學習與FPGA,指出有哪些趨勢和創新使得這些技術相互匹配,并激發對FPGA如何幫助深度學習領域發展的探討。

2019-06-28 17:31:46 7493

7493 硬件加速仿真可以實現寄存器傳輸級(RTL)和現代SoC設計門級的最佳功耗分析。只有硬件加速仿真才有處理大量邏輯以及產生針對所有元素的切換活動的獨有能力。

2019-10-11 17:54:29 5793

5793

Long-short term memory,簡稱LSTM,被廣泛的應用于語音識別、機器翻譯、手寫識別等。LSTM涉及到大量的矩陣乘法和向量乘法運算,會消耗大量的FPGA計算資源和帶寬。為了實現硬件加速,提出了稀疏LSTM。

2019-08-24 10:32:35 3449

3449

Firefly-RK3399/AIO-3399J Android8.1固件支持Android Neural Networks API (NNAPI) ,充分調用神經網絡API進行硬件加速,使RK3399的AI運算性能大幅提升。適用基于主流模型架構衍生開發的各類應用,例如:商品識別、疲勞檢測等。

2019-11-01 15:47:12 2582

2582

工藝由三星研發,與如今大多數半導體芯片采用的bulk CMOS工藝有些類似,但優勢更為顯著,能在顯著降低器件尺寸和功耗的同時,大幅提升性能和穩定性。

2020-07-03 14:05:43 2819

2819 FPGA加速卡采用CAPI接口設計,通過CAPI接口與P&P服務器緊密集成;應用于大數據分析、密碼解算、圖像圖片處理等領域,實現百倍的加速比;

2020-07-07 16:16:12 16

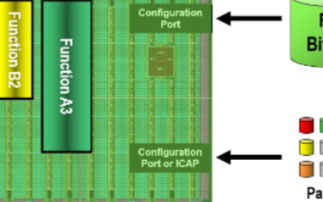

16 應用FPGA動態部分重構功能使硬件設計更加靈活,可用于硬件的遠程升級、系統容錯和演化硬件以及通信平臺設計等。動態部分重構可以通過兩種方法實現:基于模塊化設計方法(Module-Based

2020-07-29 17:10:33 2815

2815

降低了50%,芯片面積減少了65%,同時保留了Speedcore eFPGA IP的原有功能,將可編程硬件加速功能帶到廣泛的高性能計算、網絡和存儲應用中。Achronix將于9月26日參加在圣克拉拉市

2020-08-07 15:41:06 937

937 功耗是我們關注的設計焦點之一,優秀的器件設計往往具備低功耗特點。在前兩篇文章中,小編對基于Freez技術的低功耗設計以及FPGA低功耗設計有所介紹。為增進大家對低功耗的了解,以及方便大家更好的實現低功耗設計,本文將對FPGA具備的功耗加以詳細闡述。如果你對低功耗具有興趣,不妨繼續往下閱讀哦。

2021-02-14 17:50:00 7165

7165 一種基于FPGA動態可重構的圖像融合算法。該方法對小波分解后的圖像低頻子帶采用平均融合算子處理,在高頻子帶的融合中依據小波系數樹狀結構特點,提出了一種新的自適應融合方法,最后經過小波逆變換得到融合

2021-02-02 17:12:59 8

8 硬件加速器提升下一代SHARC處理器的性能

2021-04-23 13:06:32 6

6 所謂FPGA動態可重構技術,就是要對基于SRAM編程技術的FPGA實現全部或部分邏輯資源的動態功能變換。根據實現重構的面積不同,動態可重構技術又可分為全局重構和局部重構。

2021-07-05 15:41:29 4214

4214

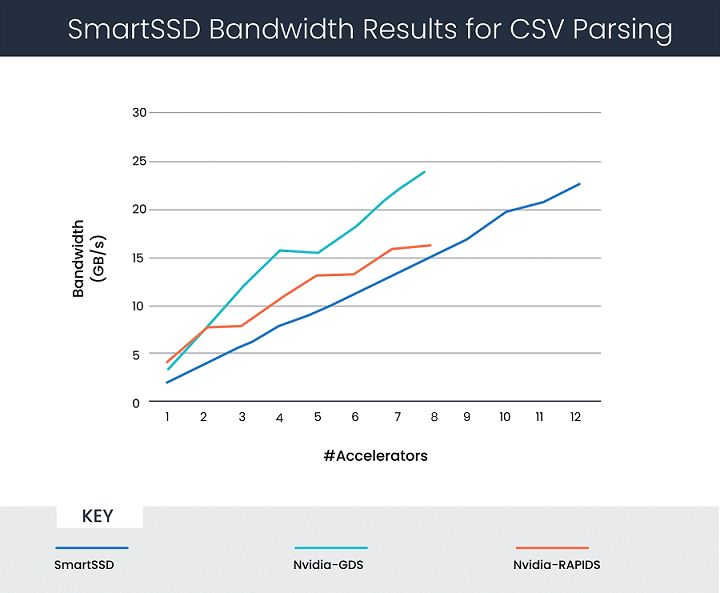

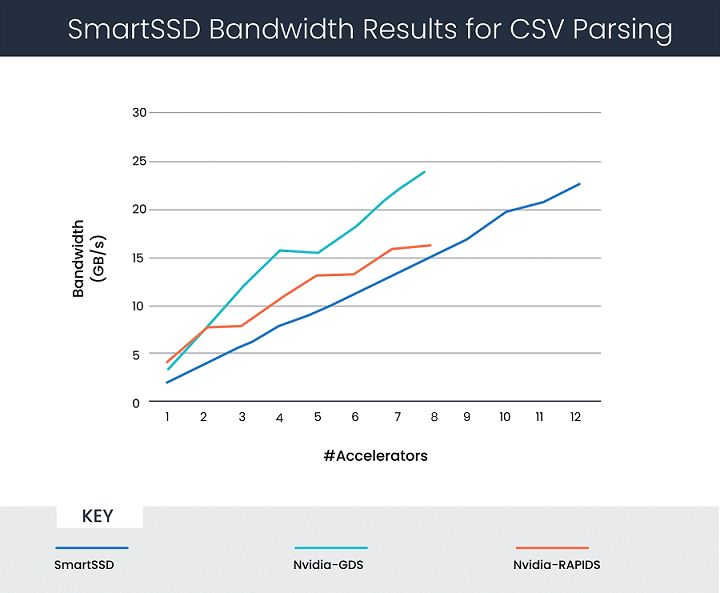

為了提升計算基礎設施的性能,并緊跟數據分析與 AI 不斷攀升的需求,眾多企業將硬件加速視為主要的解決方案。在大多數情況下,先進的可編程硬件(主要是指 GPU 和 FPGA)是加速的主要方式。通過

2021-08-13 17:45:31 8145

8145 為了提升計算基礎設施的性能,并緊跟數據分析與 AI 不斷攀升的需求,眾多企業將硬件加速視為主要的解決方案。在大多數情況下,先進的可編程硬件(主要是指 GPU 和 FPGA)是加速的主要方式。通過使用這種先進的硬件,企業正在贏得計算優勢;然而,對于編程難度,他們仍然存在合理的擔憂。

2022-08-02 08:03:36 2798

2798

在開發一個加速程序的之前,有一個很重要的步驟:正確設計程序架構。開發人員需要明確軟件應用程序中哪一部分是需要硬件加速的,并且它多少的并行量,以保證硬件加速器件(FPGA)能完美發揮其作用。本文將分為5個步驟來介紹

2022-08-02 10:33:07 986

986

該項目基于AMD Xilinx Varium C1100 FPGA加速卡,為 Filecoin 區塊鏈應用中的Poseidon哈希算法提供了一套完整的硬件加速方案。

2022-08-19 10:25:02 3510

3510 點擊上方 藍字 關注我們 ? FPGA 高級設計之實現功耗優化 與ASICs(Application Specific Integrated Circuits)比較,相似的邏輯功能,用FPGA來實現

2023-05-19 13:50:02 2284

2284 FPGA可重構技術就是通過上位機控制在FPGA運行過程中加載不同的Bitstream文件,FPGA芯片根據文件內的不同邏輯將內部的資源全部或部分進行重新配置以達到多種功能任務動態切換的目標,從而提高了使用FPGA進行開發的靈活度。

2023-08-04 10:08:05 1236

1236 FPGA 芯片在數據中心領域主要用于硬件加速,在云服務器廠商中已有廣泛部署。數據中心使用 FPGA 芯片代替傳統的 CPU 方案后,處理其自定義算法時可實現顯著的加速效果。因此近年來,微軟 Azure、亞馬遜 AWS、阿里云的服務器上都開始部署 FPGA 加速器用于運算加速。

2023-11-16 09:55:46 1482

1482

FPGA算法的優點在于它們可以提供高度的定制化和靈活性,使得算法可以根據實際需求進行優化和調整。此外,FPGA還可以實現硬件加速,提供比傳統處理器更高的計算性能和吞吐量。因此,FPGA算法在許多領域中被廣泛應用,包括嵌入式系統、高性能計算和實時信號處理等。

2024-01-15 16:03:24 3667

3667 思想是利用專門的硬件資源,如GPU或專用的解碼芯片,來分擔原本由CPU承擔的解碼任務。這種方式不僅可以大幅提高解碼速度,還能降低CPU的負載,從而實現更流暢的播放效果。 硬件加速的優勢 高效性能 :硬件解碼器通常具有更高的解碼速度

2024-02-21 14:40:48 2004

2004

FPGA(現場可編程門陣列)加速深度學習模型是當前硬件加速領域的一個熱門研究方向。以下是一些FPGA加速深度學習模型的案例: 一、基于FPGA的AlexNet卷積運算加速 項目名稱

2024-10-25 09:22:03 1856

1856 隨著人工智能技術的飛速發展,對計算性能的需求也日益增長。FPGA(現場可編程門陣列)作為一種高性能、低功耗、可靈活編程的硬件平臺,正逐漸在 AI 領域嶄露頭角,展現出獨特的優勢,為 AI 應用的落地

2025-01-06 17:37:10 2318

2318 ? 再來看一篇FPGA的綜述,我們都知道微軟包括國內的云廠商其實都在數據中心的服務器中部署了FPGA,所以這篇論文就以數據中心的視角,來看下FPGA這個硬件加速器。 還是一樣,想要論文原文的可以私信

2025-01-14 10:29:31 1303

1303

產品實拍圖 利用硬件加速提升通信協議安全性,核心是通過 專用硬件模塊或可編程硬件 ,承接軟件層面難以高效處理的安全關鍵操作(如加密解密、認證、密鑰管理等),在提升性能的同時,通過硬件級隔離、防篡改等

2025-08-27 09:59:06 782

782

驗證硬件加速是否真正提升通信協議的安全性,需從 安全功能正確性、抗攻擊能力增強、安全性能適配、合規一致性 等核心維度展開,結合實驗室測試與真實場景驗證,避免 “硬件參與即安全提升” 的表面判斷。以下

2025-08-27 10:16:58 929

929

電子發燒友App

電子發燒友App

評論