再來看一篇FPGA的綜述,我們都知道微軟包括國內(nèi)的云廠商其實都在數(shù)據(jù)中心的服務(wù)器中部署了FPGA,所以這篇論文就以數(shù)據(jù)中心的視角,來看下FPGA這個硬件加速器。

還是一樣,想要論文原文的可以私信我。

由于論文不長,我們就直接把原始論文翻譯出來,而不是跟之前一樣只總結(jié)部分內(nèi)容。

摘要

數(shù)據(jù)流特征的日益動態(tài)化,給研究帶來了更多挑戰(zhàn)。數(shù)據(jù)中心的計算復(fù)雜度、存儲、能源和安全等方面的資源消耗正處于 intense 的研究焦點之下。本文旨在回顧通過部署現(xiàn)場可編程門陣列(FPGA 設(shè)備)來提高數(shù)據(jù)中心 operational 效率的方法。由于數(shù)據(jù)中心對高性能計算的需求巨大,本文解決了在處理數(shù)據(jù)方面的問題,盡管傳統(tǒng)方案仍然存在挑戰(zhàn)。本文還回顧了支持 FPGA 在數(shù)據(jù)中心中取得積極進(jìn)展的關(guān)鍵使能技術(shù),如大數(shù)據(jù)和云計算,以及它們所面臨的挑戰(zhàn)。本文匯編并介紹了研究人員提出的 novel 架構(gòu),并對基于 FPGA 的數(shù)據(jù)中心數(shù)據(jù)管理進(jìn)行了詳細(xì)分析,為研究人員提供了更多有前景的研究方向。

1. 引言

數(shù)據(jù)中心是一種物理計算設(shè)施,用于存儲關(guān)鍵應(yīng)用程序和數(shù)據(jù),并用于共享計算應(yīng)用程序。數(shù)據(jù)中心的主要組件是交換機、路由器、防火墻、服務(wù)器和存儲介質(zhì)。在現(xiàn)代,多個數(shù)據(jù)中心通過邊緣、私有和公共云連接。在當(dāng)今的情況下,數(shù)據(jù)中心在企業(yè)資源規(guī)劃、客戶關(guān)系管理、大數(shù)據(jù)、機器學(xué)習(xí)和人工智能方面發(fā)揮著重要作用。數(shù)據(jù)中心的infrastructure經(jīng)歷了三個主要的時代:第一個時代是從大型機到 X-86 服務(wù)器,第二個時代是infrastructure的虛擬化,而現(xiàn)在是云、混合云和云原生。在過去十年中,計算負(fù)載從 10 萬增加到數(shù)百萬;所需的存儲容量從 PB 級增加到 EB 級,網(wǎng)絡(luò)容量所需的速度也朝著 Pbps 級方向增加。因此,技術(shù)擴展對功率/熱密度、中央處理器 (CPU) 性能、異構(gòu)計算(即低功耗下的高性能)的需求非常迫切。現(xiàn)在是時候從應(yīng)用程序加速、處理器卸載、性能/功耗和軟件定義開發(fā)的角度重新定義數(shù)據(jù)中心網(wǎng)絡(luò)架構(gòu),以實現(xiàn)規(guī)模擴展。

A. 數(shù)據(jù)中心中的 FPGA

為了填補數(shù)據(jù)中心的計算空白,人們認(rèn)為現(xiàn)場可編程門陣列 (FPGA) 將發(fā)揮主導(dǎo)作用,其市場價值預(yù)計將大幅上升。現(xiàn)在的 FPGA 具有高速連接、存儲塊和信號處理塊。除此之外,還提供 USB 3.0、SATA 3.0、DDR4 控制器,以實現(xiàn)高速數(shù)據(jù)處理。此外,借助內(nèi)置的 ARM 處理器,可以實現(xiàn)實時處理,該處理器具有浮點和內(nèi)存管理功能。顯然,最新的 FPGA 部署了應(yīng)用處理器單元、實時處理單元和多媒體處理單元。此外,它們還具有復(fù)雜的加密算法、高速外設(shè)和收發(fā)器。上面討論的功能都集成在 FPGA 中。Xilinx 開發(fā)了專用的自適應(yīng)加速器卡硬件模塊 ALVEO,用于數(shù)據(jù)中心相關(guān)應(yīng)用。同樣,英特爾開發(fā)了 Agilex 和 Stratix 10 FPGA 系列,用于支持四核 ARM Cortex-A53 處理器的高性能加速應(yīng)用。強烈建議對下一代計算的芯片制造工藝進(jìn)行必要的更改,尤其是在數(shù)據(jù)中心應(yīng)用中。全球大多數(shù)著名的數(shù)據(jù)中心都使用可再生能源和超環(huán)路網(wǎng)絡(luò)設(shè)施來運營,以提供高效的電信數(shù)據(jù)和基于云的服務(wù)。

II. 數(shù)據(jù)中心大數(shù)據(jù)處理方案的演進(jìn)

使用無源光網(wǎng)絡(luò),可以通過協(xié)同流調(diào)度來管理大數(shù)據(jù),并進(jìn)行資源優(yōu)化。作者還考慮了改變大數(shù)據(jù)的流量模式,并使用 MapReduce 在以交換機為中心的設(shè)計中路由數(shù)據(jù)包。無源光網(wǎng)絡(luò)還用于以服務(wù)器為中心的應(yīng)用,為數(shù)據(jù)中心網(wǎng)絡(luò)提供可靠的高速骨干架構(gòu)。為了使用戶能夠在異構(gòu)數(shù)據(jù)中心中完美地利用 FPGA 加速器,Kchris 等人開發(fā)了一種集成的多功能加速器。圖 1 顯示了在數(shù)據(jù)中心應(yīng)用中發(fā)揮重要作用的節(jié)能大數(shù)據(jù)處理方案的詳細(xì)分類。

B. 案例研究:用于數(shù)據(jù)處理的可重構(gòu)設(shè)備

硬件加速器

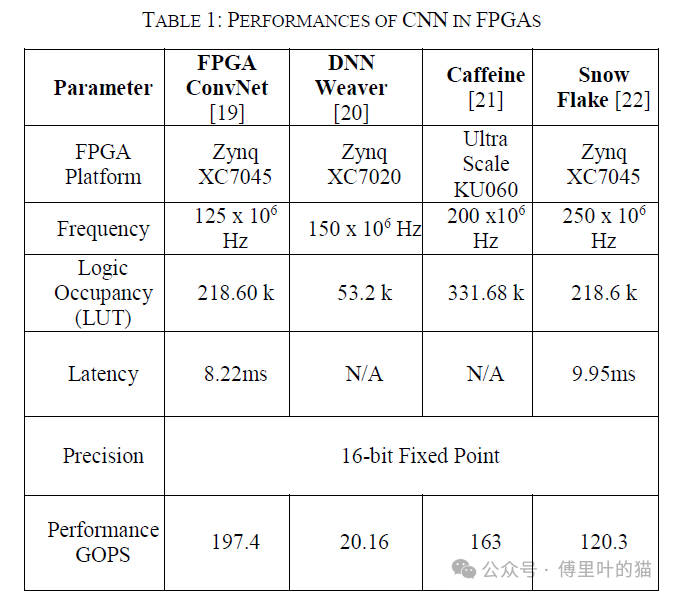

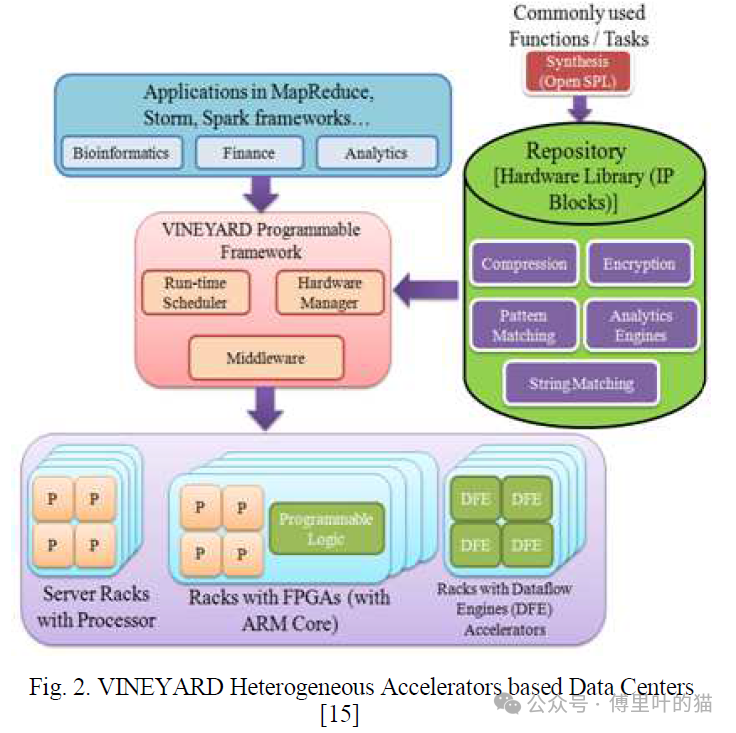

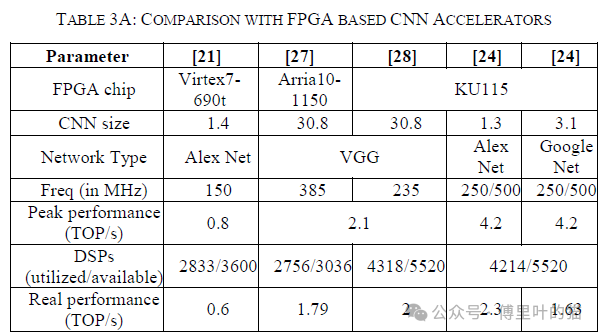

谷歌、微軟和亞馬遜已經(jīng)更新了部署 FPGA 的數(shù)據(jù)中心,以增強后端的機器學(xué)習(xí)。FPGA 為節(jié)能可編程硬件架構(gòu)提供了一種很有前景的替代方案。FPGA 的可重構(gòu)能力允許在數(shù)據(jù)中心的不同環(huán)境下實現(xiàn)高性能、低功耗和高吞吐量。表 1 列出了 CNN 在 FPGA 中的性能。基于全方位、基于加速器的異構(gòu)集成數(shù)據(jù)中心的 VINEYARD .

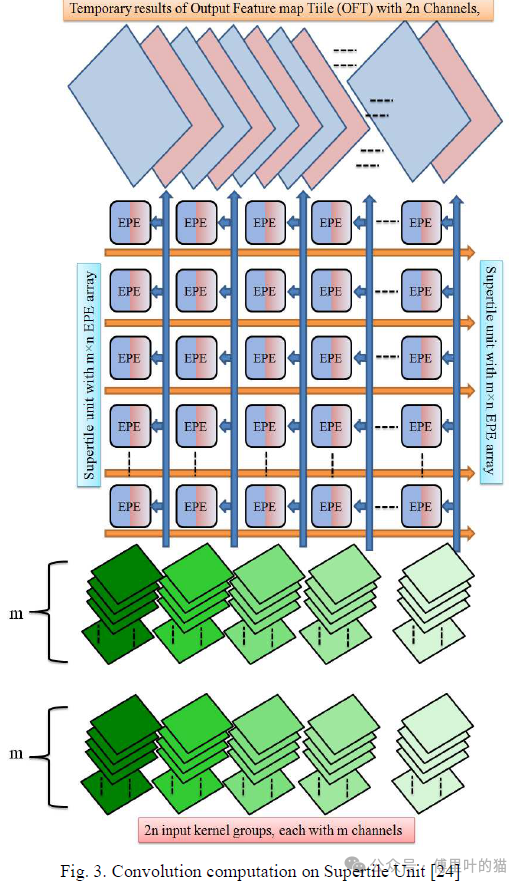

如圖 2 所示,它為具有粗粒度和細(xì)粒度可編程加速器的低能耗數(shù)據(jù)中心提供了一個單一平臺。基于 FPGA 的加速與超片概念是為 CNN 設(shè)計的,用于在數(shù)據(jù)中心中執(zhí)行各種不同的視頻和圖像相關(guān)推理任務(wù)。圖 3 顯示了超片單元上的卷積計算。在此設(shè)計中,對基本增強處理單元 (EPE) 進(jìn)行了放大和修改,使其成為超片單元,以提高不同種類卷積過程的交錯類型任務(wù)調(diào)度的性能。ConvNet、DNN Weaver、Caffeine 和 Snow Flake CNN 在 Zynq 和 Kintex FPGA 設(shè)備中實現(xiàn)。這些結(jié)果表明,所實現(xiàn)的 CNN 的工作頻率高達(dá) 250 MHz,延遲為 8.22 毫秒,并且能夠在 FPGA 中執(zhí)行 197.4 GOPS(每秒千兆次運算),如表 1 所示。

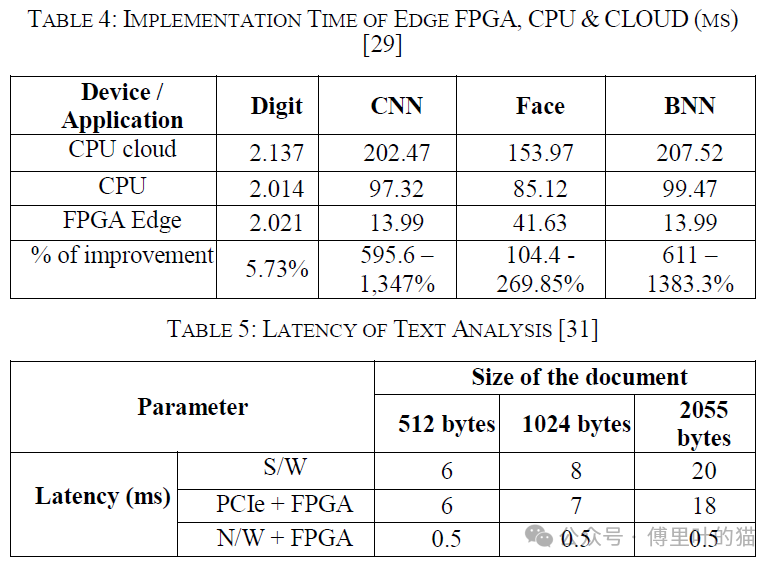

微軟自 2015 年起就將 FPGA 集成到 Bing 中,以加速數(shù)據(jù)搜索。它由 PCI Express 交換機中的 6 個 Virtex 6 組成。該 FPGA 加速器卡安裝在 Supermicro-Super-Server 中,用于 48(根據(jù)需要)節(jié)點服務(wù)器 pod,連接到 10 Gb 每秒以太網(wǎng)通信端口的 4 個節(jié)點。它已擴展到 1632 個節(jié)點集群。圖 2 顯示了 FPGA 查詢延遲行為。FPGA 的采用將搜索性能提高了 2 倍。吞吐量增加,延遲減少了 29%,與 X86 iron 相比,降低了成本(高達(dá) 30%)和功耗。可以將計算密集型任務(wù)轉(zhuǎn)發(fā)到附近的邊緣節(jié)點。具有 FPGA 的硬件可定制邊緣計算提高了性能并節(jié)省了能源。使用此方法通過卸載實現(xiàn)了基于計算機視覺的移動應(yīng)用程序,這分別為邊緣設(shè)備和移動設(shè)備提供了 16.2% 和 29.5% 的能效。如表 4 和表 5 所示,響應(yīng)時間也大大減少了。

最近,CESNET(捷克 NREN)演示了基于 Virtex Ultra Scale+ FPGA 的 NFB-200G2QL 加速器可在單個 NIC 卡中實現(xiàn) 200 Gbps 吞吐量的網(wǎng)絡(luò)數(shù)據(jù)傳輸。在此環(huán)境上進(jìn)行的現(xiàn)代基準(zhǔn)測試模擬提供的性能是完整軟件模擬的兩倍。

C. 高性能計算

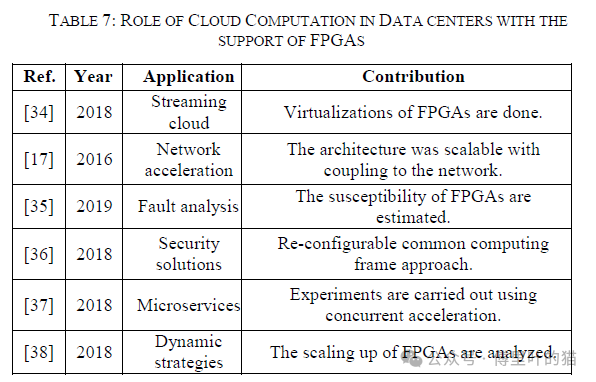

本節(jié)主要強調(diào)了將基于云的服務(wù)與基于 FPGA 的數(shù)據(jù)中心架構(gòu)相集成的重要性,以及基于云網(wǎng)絡(luò)的數(shù)據(jù)處理任務(wù)的動機。表 7 突出顯示了 FPGA 支持的云計算在數(shù)據(jù)中心中的各種作用。

在 FPGA 上移植應(yīng)用程序并不是適用于數(shù)據(jù)中心或云應(yīng)用程序中使用的所有類型和配置的 FPGA 的即插即用任務(wù)。為數(shù)據(jù)中心開發(fā)的 FPGA 虛擬化可用于與領(lǐng)域無關(guān)的用戶設(shè)計進(jìn)行交互。顯然,虛擬化 FPGA 是為數(shù)據(jù)中心中的流式云應(yīng)用程序開發(fā)的,并將結(jié)果與使用 FPGA 設(shè)計的傳統(tǒng)虛擬機進(jìn)行了比較。即使 FPGA 中軟錯誤的物理發(fā)生頻率不高,也需要測試 FPGA 的魯棒性。尤其是在采用了超過 100,000 個 FPGA 節(jié)點的大規(guī)模數(shù)據(jù)中心中,需要確保可靠性以避免數(shù)據(jù)損壞。對基于 FPGA 的云計算節(jié)點進(jìn)行故障分析,以估計 FPGA 在云計算中對軟錯誤的敏感性。對 FPGA 結(jié)構(gòu)代理和多 FPGA 結(jié)構(gòu)的設(shè)計進(jìn)行了動態(tài)策略分析,并對 FPGA 的擴展進(jìn)行了分析,觀察到吞吐量、性能和延遲方面的改進(jìn)。

D. 高性能計算

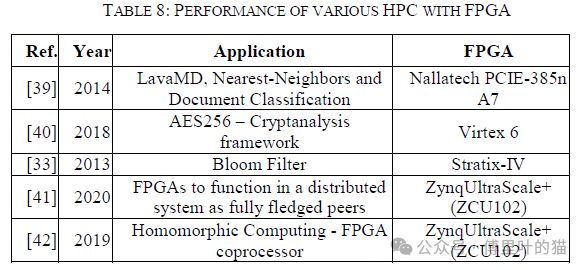

隨著智能設(shè)備、自動駕駛汽車和互聯(lián)工廠的發(fā)展,它們將生成大量需要處理的數(shù)據(jù)。高性能計算用于利用分布式計算資源來解決復(fù)雜問題,其中包含大約 TB 甚至 ZB 的大型數(shù)據(jù)集,這些數(shù)據(jù)集需要實時處理。此類高性能計算通常由 CPU 和 GPU 執(zhí)行。表 8 突出顯示了 FPGA 在 HPC 中最重要的作用。

與 CPU 和 GPU 相比,F(xiàn)PGA 在某些應(yīng)用中的性能優(yōu)于 CPU 和 GPU:

線性代數(shù)方程的求解速度比 CPU 快 19 倍。地球物理的 3D 卷積比 CPU 快 70 倍,比 CPU 快 14 倍。分子動力學(xué)的求解速度比 NAMD CPU 快 80 倍。用于生物信息學(xué)的基本局部比對搜索工具 (BLAST) 的求解速度比并行優(yōu)化的 CPU 快 5 倍。用于氣候建模的全球大氣方程比 CPU 快 19 倍,比 GPU 快 7 倍。FPGA 可配置用于具有高速計算的數(shù)據(jù)壓縮應(yīng)用程序,并將其集成到虛擬化環(huán)境中。

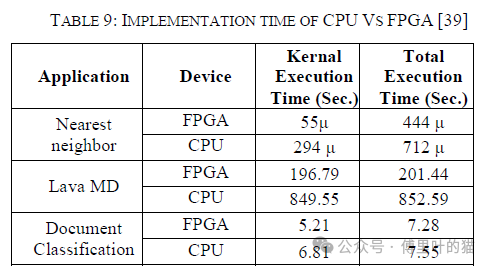

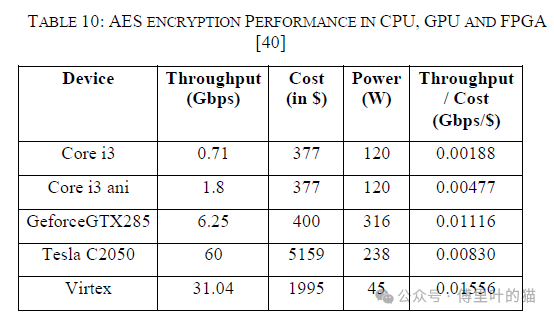

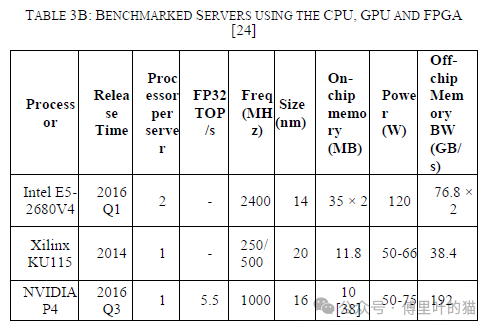

此外,在沒有任何通信開銷的情況下,F(xiàn)PGA 可以配置為提供具有更好硬件加速的微服務(wù)。使用帶有 OpenCL 編譯器的 Nallatech FPGA 實現(xiàn)了兩個 HPC 應(yīng)用程序,例如最近鄰和 Lava MD(分子動力學(xué))以及文檔分類。與 Xeon 類型的處理器相比,此硬件架構(gòu)產(chǎn)生的結(jié)果快 4.3 倍、5.3 倍和 1.3 倍。FPGA 實現(xiàn)的功耗也降低了。表 9 顯示了上述應(yīng)用程序的實現(xiàn)時間。在 FPGA、CPU 和 GPU 上演示了 AES256。基于 FPGA 的密碼分析在成本、功耗和吞吐量方面的性能優(yōu)于 GPU 和 CPU,如表 9 和表 10 所示。

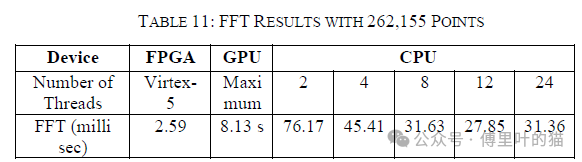

基于 ZU102 FPGA 的配置與純軟件數(shù)據(jù)傳輸相比,延遲降低了 25%。此外,在相同配置上進(jìn)行 HPC 矩陣乘法的吞吐量提高了 10%。FPGA 可以配置為協(xié)處理器,因此與英特爾 i5 處理器相比,它可以使同態(tài)加密算法的速度提高 13 倍。表 11 列出了 FFT 實現(xiàn)的結(jié)果。它證實了基于 FPGA 的實現(xiàn)具有更高的吞吐量,并且由于模塊之間通過互連進(jìn)行高速數(shù)據(jù)傳輸而降低了延遲。

因此,可以將 FPGA 集成到特定應(yīng)用任務(wù)、計算密集型任務(wù)、內(nèi)存訪問結(jié)構(gòu)等中,以改善延遲、吞吐量和執(zhí)行速度。

III. 未來研究趨勢、挑戰(zhàn)和機遇

隨著數(shù)據(jù)量的增加,數(shù)據(jù)中心必須移動更多的數(shù)據(jù),它們面臨著來自不同方向的重大挑戰(zhàn)。盡管列出的問題并不代表所有基于 FPGA 的數(shù)據(jù)中心中尚未解決的研究趨勢,但它們對通過高速計算執(zhí)行以數(shù)據(jù)為中心的功能(如持久性、數(shù)據(jù)縮減、數(shù)據(jù)安全、數(shù)據(jù)過濾、數(shù)據(jù)分析等)具有長期影響。因此,F(xiàn)PGA 數(shù)據(jù)中心預(yù)計將與 CPU 進(jìn)行協(xié)同調(diào)度,包括異構(gòu)云數(shù)據(jù)中心管理、深度神經(jīng)網(wǎng)絡(luò)加速、通道攻擊管理、FPGA 調(diào)度、虛擬化和漏洞分析。

IV. 結(jié)論和未來范圍

芯片制造技術(shù)和 FPGA 的進(jìn)步至關(guān)重要,它們在增強數(shù)據(jù)中心數(shù)據(jù)管理性能方面發(fā)揮著至關(guān)重要的作用。CPU 和傳統(tǒng)計算資源面臨著許多與數(shù)據(jù)流的動態(tài)特性相關(guān)的問題,這些問題涉及在數(shù)據(jù)中心云網(wǎng)絡(luò)中處理數(shù)據(jù)流。FPGA 集群架構(gòu)、云計算、硬件加速方面的創(chuàng)新可用于實現(xiàn)數(shù)據(jù)的快速處理并適應(yīng)其動態(tài)流特性。

-

FPGA

+關(guān)注

關(guān)注

1662文章

22469瀏覽量

638083 -

加速器

+關(guān)注

關(guān)注

2文章

841瀏覽量

40185 -

數(shù)據(jù)中心

+關(guān)注

關(guān)注

18文章

5719瀏覽量

75161

原文標(biāo)題:數(shù)據(jù)中心中的FPGA硬件加速器

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術(shù)江湖】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

Arm CPU推動數(shù)據(jù)中心業(yè)務(wù)正加速發(fā)展

FPGA硬件加速卡設(shè)計原理圖:1-基于Xilinx XCKU115的半高PCIe x8 硬件加速卡 PCIe半高 XCKU115-3-FLVF1924-E芯片

1分鐘帶你了解數(shù)據(jù)中心供電架構(gòu) #電子元器件 #數(shù)據(jù)中心 #供電架構(gòu)

派恩杰SiC器件在數(shù)據(jù)中心中的應(yīng)用

常用硬件加速的方法

軟硬件協(xié)同技術(shù)分享 - 任務(wù)劃分 + 自定義指令集

硬件加速模塊的時鐘設(shè)計

Cadence 借助 NVIDIA DGX SuperPOD 模型擴展數(shù)字孿生平臺庫,加速 AI 數(shù)據(jù)中心部署與運營

如何驗證硬件加速是否真正提升了通信協(xié)議的安全性?

Microchip推出Adaptec? SmartRAID 4300 系列加速器 提供安全的可擴展 NVMe? RAID 存儲解決方案

PCIe協(xié)議分析儀在數(shù)據(jù)中心中有何作用?

大型數(shù)據(jù)中心中的差分晶體振蕩器應(yīng)用與頻率匹配方案解析

數(shù)據(jù)中心中的FPGA硬件加速器

數(shù)據(jù)中心中的FPGA硬件加速器

評論