使用 C 語言的OpenCL 2a并行編程擴(kuò)展來補(bǔ)充基于 FPGA 的 CNN 加速應(yīng)用程序的開發(fā)。適用于卷積神經(jīng)網(wǎng)絡(luò)的 FPGA 器件的一個(gè)示例是英特爾可編程解決方案集團(tuán) (PSG)的Arria 10系列器件,其正式名稱為Altera。

2022-08-02 15:13:16 3248

3248

現(xiàn)場可編程門陣列(FPGA)具有低功耗、高性能和靈活性的特點(diǎn)。FPGA神經(jīng)網(wǎng)絡(luò)加速的研究正在興起,但大多數(shù)研究都基于國外的FPGA器件。為了改善國內(nèi)FPGA的現(xiàn)狀,提出了一種新型的卷積神經(jīng)網(wǎng)絡(luò)加速

2023-08-21 10:30:01 3740

3740

本設(shè)計(jì)中,計(jì)劃實(shí)現(xiàn)對文件的壓縮及解壓,同時(shí)優(yōu)化壓縮中所涉及的信號處理和計(jì)算密集型功能,實(shí)現(xiàn)對其的加速處理。本設(shè)計(jì)的最終目標(biāo)是證明在充分并行化的硬件體系結(jié)構(gòu) FPGA 上實(shí)現(xiàn)該算法時(shí),可以大大提高該算

2025-07-10 11:09:34 2197

2197

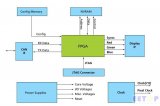

本文描述了ADC和FPGA之間LVDS接口設(shè)計(jì)需要考慮的因素,包括LVDS數(shù)據(jù)標(biāo)準(zhǔn)、LVDS接口數(shù)據(jù)時(shí)序違例解決方法以及硬件設(shè)計(jì)要點(diǎn)。

2025-07-29 10:01:26 5141

5141

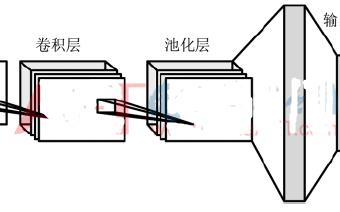

近來卷積神經(jīng)網(wǎng)絡(luò)(CNN)的研究十分熱門。CNN發(fā)展的一個(gè)瓶頸就是它需要非常龐大的運(yùn)算量,在實(shí)時(shí)性上有一定問題。而FPGA具有靈活、可配置和適合高并行度計(jì)算的優(yōu)點(diǎn),十分適合部署CNN。 快速開始

2020-11-09 17:28:59 2979

2979

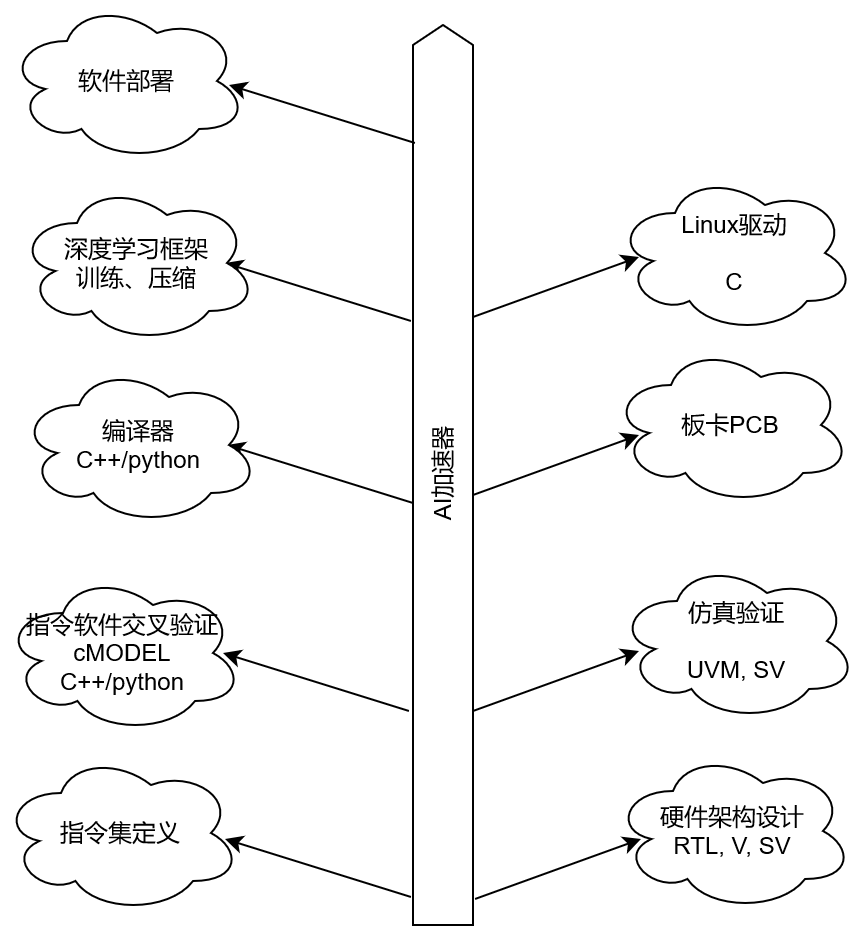

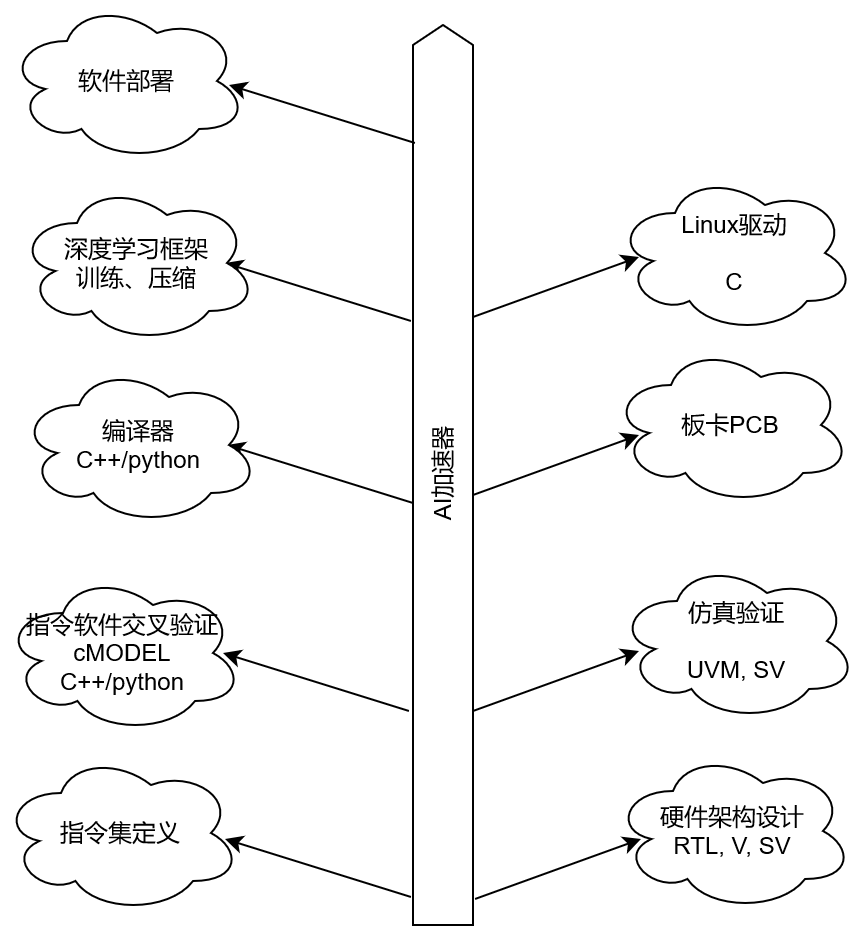

前言 做深度學(xué)習(xí)加速器已經(jīng)兩年了,從RTL設(shè)計(jì)到仿真驗(yàn)證,以及相應(yīng)的去了解了Linux驅(qū)動,深度學(xué)習(xí)壓縮方法等等。今天來捋一捋AI加速器都涉及到哪些領(lǐng)域,需要哪些方面的知識。可以用于AI加速

2020-10-10 16:25:43 4278

4278

是管腳的分配也必須在設(shè)計(jì)代碼出來之前完成。所以,管腳的分配更多的將是依賴人,而非工具,這個(gè)時(shí)候就更需要考慮各方面的因素。 綜合起來主要考慮以下的幾個(gè)方面: 1 、 FPGA 所承載邏輯的信號流向。 IC

2012-08-11 10:27:54

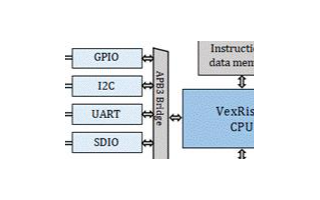

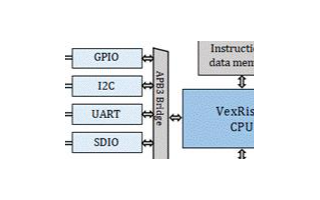

FPGA實(shí)現(xiàn)SDIO訪問時(shí),需要注意以下幾個(gè)關(guān)鍵問題和細(xì)節(jié):

初始化過程:

SDIO總線的初始化是確保FPGA與SD卡能夠正常通信的第一步。這包括設(shè)置時(shí)鐘頻率、配置數(shù)據(jù)傳輸模式以及校驗(yàn)協(xié)議等

2024-06-27 08:38:12

控制這些開關(guān),從而定義FPGA內(nèi)部的信號路徑。

FPGA的工作原理主要涉及以下步驟:

設(shè)計(jì)描述 :首先,用戶需要使用硬件描述語言(如VHDL或Verilog)來描述他們想要實(shí)現(xiàn)的數(shù)字系統(tǒng)。這個(gè)描述稱為

2024-01-26 10:03:55

考慮如何解決計(jì)算需求的增長,而FPGA作為一種可編程的加速硬件彼時(shí)進(jìn)入了大家的視野。有了解決計(jì)算需求的想法后,需要通過實(shí)踐驗(yàn)證FPGA實(shí)際的能力。騰訊的QQ、微信業(yè)務(wù),用戶每天產(chǎn)生的圖片數(shù)量都是數(shù)億級別

2017-04-15 16:17:41

FPGA上的PCIe接口應(yīng)用是一個(gè)復(fù)雜的任務(wù),需要考慮多個(gè)方面的問題以確保系統(tǒng)的穩(wěn)定性和性能。以下是在FPGA的PCIe接口應(yīng)用中需要注意的關(guān)鍵問題:

硬件資源和內(nèi)部架構(gòu) :

FPGA的型號和尺寸

2024-05-27 16:17:41

時(shí)候就更需要考慮各方面的因素。

綜合起來主要考慮以下的幾個(gè)方面:1、 FPGA所承載邏輯的信號流向。IC 驗(yàn)證中所選用的 FPGA一般邏輯容量都非常大,外部的管腳數(shù)量也相當(dāng)?shù)呢S富,這個(gè)時(shí)候就必須考慮

2024-01-10 22:40:14

FPGA管腳分配需要考慮的因素 FPGA 管腳分配需要考慮的因素 在芯片的研發(fā)環(huán)節(jié),FPGA 驗(yàn)證是其中的重要的組成部分,如何有效的利用FPGA 的資源,管腳分配也是必須考慮的一個(gè)重要問題。一般較好

2012-08-11 11:34:24

依賴人,而非工具,這個(gè)時(shí)候就更需要考慮各方面的因素。 綜合起來主要考慮以下的幾個(gè)方面: 1、 FPGA所承載邏輯的信號流向。 IC 驗(yàn)證中所選用的 FPGA一般邏輯容量都非常大,外部的管腳數(shù)量也相當(dāng)

2017-03-25 18:46:25

FPGA管腳分配需要考慮的因素.pdf

2012-08-20 19:23:04

/*2017.3.12 zc in xiandian核心是有一個(gè)n位的寄存器Fo=clk*K/2^N; k是步進(jìn)值,Fo是想要的頻率作用:更加精準(zhǔn)的分頻程序 而且不需要考慮奇偶分頻,只需要知道你要分

2017-03-12 21:50:52

USB 芯片和軟件廠商飛特蒂亞(FTDI)公司發(fā)布一款靈活而強(qiáng)大的開發(fā)平臺 Morph-IC-II,可加速基于FPGA的應(yīng)用與制作,并簡化先進(jìn)邏輯電路設(shè)計(jì)中整合高速480Mbit/s USB通訊作業(yè)

2019-07-03 08:29:05

算法的軟件實(shí)現(xiàn)方式非常低效,所以業(yè)界對GNN的硬件加速有著非常迫切的需求。我們知道傳統(tǒng)的CNN(卷積神經(jīng)網(wǎng)絡(luò)網(wǎng)絡(luò))硬件加速方案已經(jīng)有非常多的解決方案;但是,GNN的硬件加速尚未得到充分的討論和研究,在

2021-07-07 08:00:00

PCB設(shè)計(jì)的可制造性分為哪幾類?PCB設(shè)計(jì)時(shí)考慮的內(nèi)容有哪些?

2021-04-21 06:16:30

TF之CNN:CNN實(shí)現(xiàn)mnist數(shù)據(jù)集預(yù)測 96%采用placeholder用法+2層C及其max_pool法+隱藏層dropout法+輸出層softmax法+目標(biāo)函數(shù)cross_entropy法+

2018-12-19 17:02:40

在TensorFlow中實(shí)現(xiàn)CNN進(jìn)行文本分類(譯)

2019-10-31 09:27:55

我是新手,想上傳附件,請問“以下內(nèi)容只有回復(fù)后才可以瀏覽”要怎樣設(shè)置?請懂得的老師指導(dǎo),在此先謝了![em64]

2009-11-10 14:09:51

,如有錯(cuò)誤還望大佬們指出,我馬上改正。

目錄和進(jìn)度

目前閱讀到第一章,先更新到第一章的內(nèi)容吧

卷積神經(jīng)網(wǎng)絡(luò)

運(yùn)算子系統(tǒng)的設(shè)計(jì)

儲存子系統(tǒng)的設(shè)計(jì)

架構(gòu)優(yōu)化技術(shù)

安全與防護(hù)

神經(jīng)網(wǎng)絡(luò)加速器的實(shí)現(xiàn)

2023-09-16 11:11:01

首先感謝電子發(fā)燒友論壇提供的書籍和閱讀評測的機(jī)會。

拿到書,先看一下封面介紹。這本書的中文名是《AI加速器架構(gòu)設(shè)計(jì)與實(shí)現(xiàn)》,英文名是Accelerator Based on CNN Design

2023-09-17 16:39:45

實(shí)現(xiàn)了一種I/O流水線接口,該接口具有I/O連接加速器的典型性能。FPGA/PowerPC/APU接口FPGA允許硬件設(shè)計(jì)工程師利用單芯片上的處理器、解碼邏輯、外設(shè)和協(xié)處理器實(shí)現(xiàn)一個(gè)完整的計(jì)算系統(tǒng)

2015-02-02 14:18:19

項(xiàng)目名稱:圖像目標(biāo)識別FPGA硬件加速試用計(jì)劃:申請理由 本人供職于一家AI公司,現(xiàn)在在使用FPGA硬件加速相關(guān)目標(biāo)檢測算法的端側(cè)實(shí)現(xiàn)(鑒黃/司機(jī)行為識別),公司已經(jīng)有非常成熟的軟件算法以及GPU

2019-01-09 14:51:09

使用硬件加速器來進(jìn)一步提升性能。我寫的這個(gè)簡化的代碼只是為了幫助理解FPGA如何可能參與AI計(jì)算的過程。在實(shí)際的FPGA AI加速項(xiàng)目中,還需要考慮如何有效地處理數(shù)據(jù)流、優(yōu)化內(nèi)存訪問、并行化計(jì)算單元以及處理

2024-02-12 16:18:43

。對應(yīng)數(shù)學(xué)模型的輸出。

多層感知器(MLP):

單層的感知器只能解決一些簡單的線性問題,面對復(fù)雜的非線性問題束手無策,考慮到輸入信號需要經(jīng)過多個(gè)神經(jīng)元處理后,最后得到輸出,所以發(fā)展出來了多層感知器,引入

2023-08-18 06:56:34

代碼加速和代碼轉(zhuǎn)換到硬件協(xié)處理器的方法如何采用FPGA協(xié)處理器實(shí)現(xiàn)算法加速?

2021-04-13 06:39:25

為你的FPGA設(shè)計(jì)加加速,NIC、Router、Switch任意實(shí)現(xiàn)

優(yōu)秀的IC/FPGA開源項(xiàng)目(二)-NetFPGA

《優(yōu)秀的IC/FPGA開源項(xiàng)目》是新開的系列,旨在介紹單一項(xiàng)目,會比《優(yōu)秀

2023-11-01 16:27:44

了解完以下內(nèi)容,再學(xué)ARM也不遲 01文章來源聲明本文是從互聯(lián)網(wǎng)整理而來,主要針對ARM初學(xué)者,幫助初學(xué)者了解ARM相關(guān)名詞、概念。02ARM簡介1.ARM是一門技術(shù),也是一個(gè)公司,只賣知識產(chǎn)權(quán),不

2017-08-27 16:15:11

條;而arm芯片寄存器較多,指令集也多,要掌握它需要耐心和時(shí)間,所以,為了簡化嵌入式軟件的編程工作量,生產(chǎn)公司把寄存器的操作封裝成函數(shù),這就是固件函數(shù)庫。學(xué)習(xí)時(shí)建議遵循以下步驟:先學(xué)習(xí)GPIO,再學(xué)習(xí)串口,中斷,定時(shí)器,flash等,再熟悉具體的外設(shè)操作,如果還有需要再學(xué)習(xí)跑操作系統(tǒng)。

2017-09-29 09:04:43

條;而arm芯片寄存器較多,指令集也多,要掌握它需要耐心和時(shí)間,所以,為了簡化嵌入式軟件的編程工作量,生產(chǎn)公司把寄存器的操作封裝成函數(shù),這就是固件函數(shù)庫。學(xué)習(xí)時(shí)建議遵循以下步驟:先學(xué)習(xí)GPIO,再學(xué)習(xí)串口,中斷,定時(shí)器,flash等,再熟悉具體的外設(shè)操作,如果還有需要再學(xué)習(xí)跑操作系統(tǒng)。

2017-10-17 09:58:03

設(shè)計(jì)GTXGTH收發(fā)器電源設(shè)計(jì)1.概述Xilinx 7系列FPGA GTX/GTH收發(fā)器是模擬電路,當(dāng)設(shè)計(jì)和實(shí)現(xiàn)PCB設(shè)計(jì)需要特殊考慮和注意。這其中涉及器件管腳功能、傳輸線阻抗和布線、供電設(shè)計(jì)濾波、器件選擇、PCB布線和層疊設(shè)計(jì)相關(guān)內(nèi)容。2.管腳描述和設(shè)計(jì)指導(dǎo)2.1 GTX/GTH收發(fā)器管腳描述

2021-11-11 07:42:37

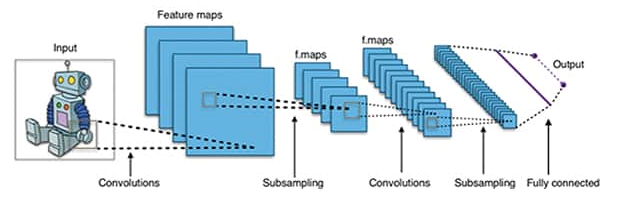

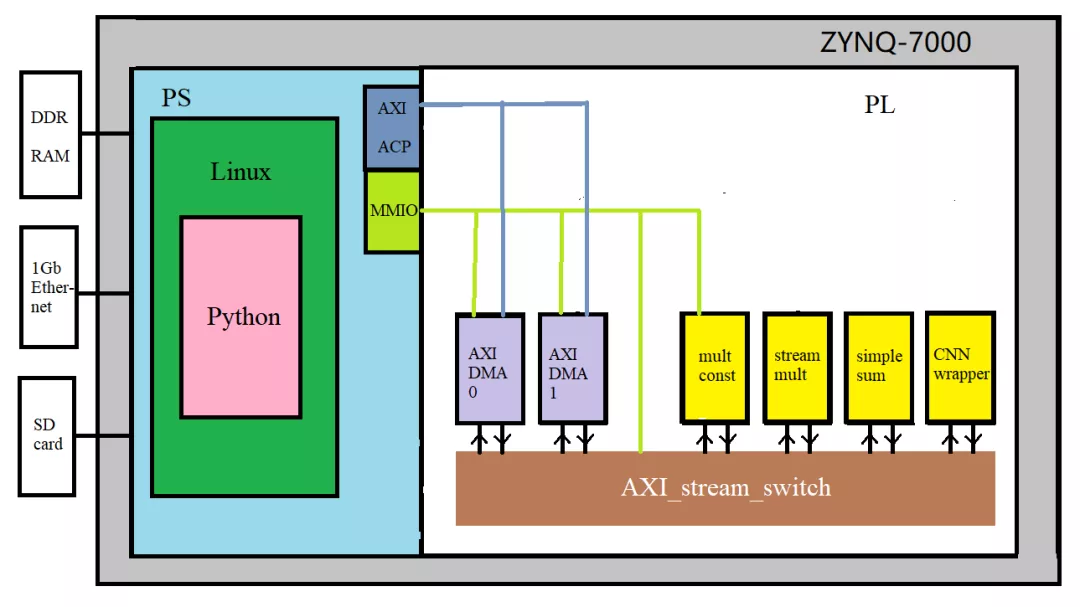

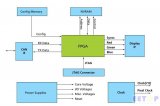

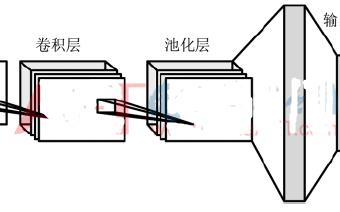

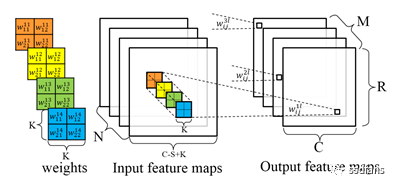

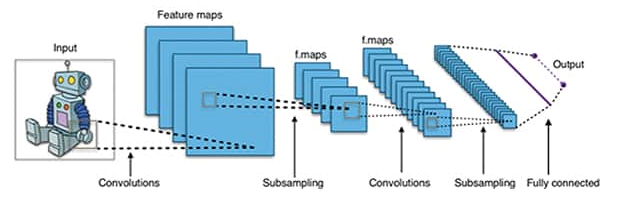

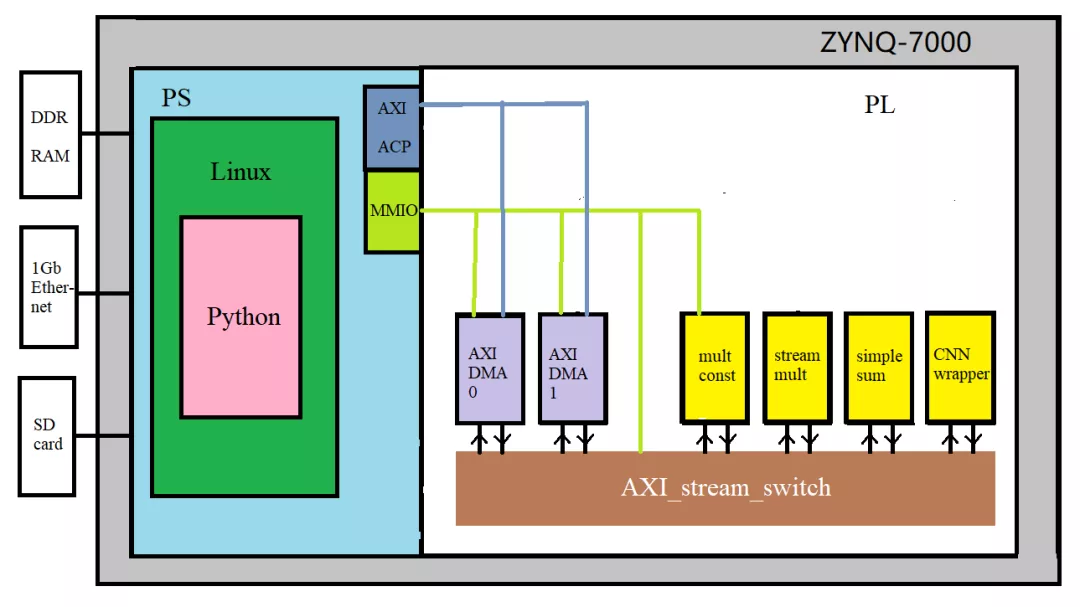

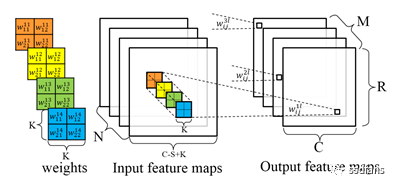

硬件加速,最典型的架構(gòu)就是將需要加速的大運(yùn)算量邏輯部署到FPGA上,而將流程控制的邏輯部署到arm上。典型的ZYNQ SoC結(jié)構(gòu)如圖1。 CNN簡介 CNN全稱卷積神經(jīng)網(wǎng)絡(luò),包括卷積層

2021-01-15 17:09:15

是動態(tài)交互類內(nèi)容,跨網(wǎng)鏈接不夠穩(wěn)定會存在風(fēng)險(xiǎn),需要全站加速保障每一筆交易。如今,大部分站點(diǎn)也都想要尋求更安全高效的網(wǎng)絡(luò)鏈路和內(nèi)容分發(fā)途徑了。全站加速和其他CDN技術(shù)和云產(chǎn)品融合,支持全鏈路HTTPS

2018-06-12 16:26:20

有沒有正在做壓電發(fā)電的大神,小弟正在做一個(gè)自供電電源 ,想要實(shí)現(xiàn)的是不需要外部供電,可以實(shí)現(xiàn)給低功耗的系統(tǒng)供電,通過壓電材料所發(fā)的電能來實(shí)現(xiàn),目前需要大神指導(dǎo),來進(jìn)行理論計(jì)算,算出理論值和實(shí)際值做比較,由于涉及的學(xué)科太多,理論分析一直沒什么進(jìn)展,求大神指導(dǎo)。。。。。。。。。

2014-11-28 09:39:11

在選購加速度傳感器的時(shí)候,需要考慮什么?模擬輸出 vs 數(shù)字輸出:這個(gè)是最先需要考慮的。這個(gè)取決于你系統(tǒng)中和加速度傳感器之間的接口。一般模擬輸出的電壓和加速度是成比例的,比如2.5V對應(yīng)0g的加速

2012-02-02 15:31:55

流水線結(jié)構(gòu)和很強(qiáng) 的并行處理能力,還擁有低功耗、配置方便靈活的特性,可以根據(jù)應(yīng)用需要來編程定制硬 件,已成為研究實(shí)現(xiàn) CNN 硬件加速的熱門平臺。

綜上所述,使用功耗低、并行度高的 FPGA 平臺加速

2023-06-20 19:45:12

內(nèi)容簡介:掌握FPGA的編程仿真,實(shí)現(xiàn)數(shù)控圓弧插補(bǔ)的程序設(shè)計(jì)。插補(bǔ)程序設(shè)計(jì)除考慮幾何關(guān)系,還需要考慮速度的變化。

2013-04-23 09:32:46

細(xì)胞神經(jīng)網(wǎng)絡(luò)(CNN)是一種能實(shí)時(shí)、高速并行處理信號的大規(guī)模非線性模擬電路,具有易于VLSI實(shí)現(xiàn)、能高速并行處理信息的優(yōu)點(diǎn),因此CNN非常適合用于仿生眼中的圖像信息處理[6],在這里將簡單回顧一下

2009-09-19 09:35:15

FPGA 上實(shí)現(xiàn)卷積神經(jīng)網(wǎng)絡(luò) (CNN)。CNN 是一類深度神經(jīng)網(wǎng)絡(luò),在處理大規(guī)模圖像識別任務(wù)以及與機(jī)器學(xué)習(xí)類似的其他問題方面已大獲成功。在當(dāng)前案例中,針對在 FPGA 上實(shí)現(xiàn) CNN 做一個(gè)可行性研究

2019-06-19 07:24:41

基于FPGA的嵌入式系統(tǒng)能夠充當(dāng)微處理器的系統(tǒng),那么我們就必須要學(xué)習(xí)NIOS II (SOPC)系統(tǒng)設(shè)計(jì),而且在設(shè)計(jì)之時(shí)系統(tǒng)應(yīng)包括以下內(nèi)容,這是因?yàn)槲⑻幚砥骱?b class="flag-6" style="color: red">FPGA之間的區(qū)別就是FPGA上電時(shí)不包含任何邏輯(基于SDRAM工藝所致),我們需要系統(tǒng)運(yùn)行之前來配置FPGA處理器。(1)JTAG接口支持FPGA配置以

2021-12-21 07:12:52

單片機(jī)(Cortex-M內(nèi)核,無操作系統(tǒng))可以跑深度學(xué)習(xí)嗎? ——Read Air 2019.8.20Xu_CNN框架待處理:1.需要設(shè)計(jì)一個(gè)可讀寫的消息棧 ()2.函數(shù)的類型參數(shù)使用結(jié)構(gòu)體傳入 (已實(shí)現(xiàn))3.動態(tài)...

2021-12-09 08:02:27

MIMRTX1064(SDK2.13.0)的KWS demo中放置了ds_cnn_s.tflite文件,提供demo中使用的模型示例。在 read.me 中,聲明我可以找到腳本,但是,該文檔中的腳本

2023-04-19 06:11:51

的仿真形式 Quartus] Quartus II調(diào)用Modelsim的兩種仿真形式為:1、RTL級仿真;2、Gate-level仿真。 以下內(nèi)容均經(jīng)過資料查證,詳細(xì)如下:

2020-05-13 07:00:00

訓(xùn)練一個(gè)神經(jīng)網(wǎng)絡(luò)并移植到Lattice FPGA上,通常需要開發(fā)人員既要懂軟件又要懂?dāng)?shù)字電路設(shè)計(jì),是個(gè)不容易的事。好在FPGA廠商為我們提供了許多工具和IP,我們可以在這些工具和IP的基礎(chǔ)上做

2020-11-26 07:46:03

隨著互聯(lián)網(wǎng)用戶的快速增長,數(shù)據(jù)體量的急劇膨脹,數(shù)據(jù)中心對計(jì)算的需求也在迅猛上漲。同時(shí),人工智能、高性能數(shù)據(jù)分析和金融分析等計(jì)算密集型領(lǐng)域的興起,對計(jì)算能力的需求已遠(yuǎn)遠(yuǎn)超出了傳統(tǒng)CPU處理器的能力所及。

2019-10-23 07:17:09

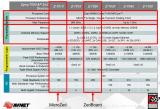

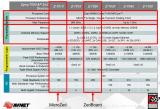

使用奇異值分解(SVD) 降低矩陣秩來減少權(quán)重和乘法的數(shù)量硬件架構(gòu)優(yōu)化1、循環(huán)優(yōu)化2、數(shù)據(jù)流3、層間融合降低復(fù)雜性的卷積實(shí)現(xiàn),例如FFT和Winograd等方法3.1 FPGA用于CNN網(wǎng)絡(luò)加速如表1

2023-02-08 15:26:46

,其算法的軟件實(shí)現(xiàn)方式非常低效,所以業(yè)界對GNN的硬件加速有著非常迫切的需求。我們知道傳統(tǒng)的CNN(卷積神經(jīng)網(wǎng)絡(luò)網(wǎng)絡(luò))硬件加速方案已經(jīng)有非常多的解決方案;但是,GNN的硬件加速尚未得到充分的討論和研究

2020-10-20 09:48:39

你好,美好的一天 我正在開始研究高頻率的RFID系統(tǒng),我想做一個(gè)簡單的讀者設(shè)計(jì)。 我正在考慮使用ST95HF或CR95HF芯片組,因?yàn)樗鼈兌际亲x寫器類型 是否有任何建議要考慮主機(jī)的標(biāo)簽和微控制器

2019-07-16 16:12:14

FPGA設(shè)計(jì)者使用Altera FPGA,也可能即使使用xilinx FPGA ,但還未閱讀過UG949,我想這都沒關(guān)系,一起看下當(dāng)前FPGA設(shè)計(jì)流程以及重點(diǎn)考慮的方方面面。

2019-10-11 07:04:21

設(shè)計(jì)師如果想要開發(fā)出帶高效觸摸屏界面的游戲機(jī)需要考慮什么因素?

2021-04-13 06:16:17

ASIC、FPGA和DSP的應(yīng)用領(lǐng)域呈現(xiàn)相互覆蓋的趨勢,使設(shè)計(jì)人員必須在軟件無線電結(jié)構(gòu)設(shè)計(jì)中重新考慮器件選擇策略問題。從可編程性、集成度、開發(fā)周期、性能和功率五個(gè)方面探究,你會發(fā)現(xiàn)軟件無線電設(shè)計(jì)中選擇ASIC、FPGA和DSP時(shí)需要考慮哪些因素?

2019-08-16 07:51:25

在芯片的研發(fā)環(huán)節(jié),FPGA 驗(yàn)證是其中的重要的組成部分,如何有效的利用FPGA 的資源,管腳分配也是必須考慮的一個(gè)重要問題。一般較好的方法是在綜合過程中通過時(shí)序的一些約

2010-06-24 17:43:35 29

29 購買音頻會議系統(tǒng)需要注意哪些問題?

在購買音頻會議系統(tǒng)時(shí)有以下幾點(diǎn)是需要我們考慮的:

1、考慮到原音的還

2010-02-21 09:12:09 846

846 當(dāng)前,AI因?yàn)槠?b class="flag-6" style="color: red">CNN(卷積神經(jīng)網(wǎng)絡(luò))算法出色的表現(xiàn)在圖像識別領(lǐng)域占有舉足輕重的地位。基本的CNN算法需要大量的計(jì)算和數(shù)據(jù)重用,非常適合使用FPGA來實(shí)現(xiàn)。上個(gè)月,Ralph Wittig

2016-05-24 11:48:21 9962

9962 本文主要介紹了在FPGA開發(fā)過程中管腳分配時(shí)需要考慮的一些實(shí)際因素,減少后續(xù)開發(fā)過程中發(fā)生一些細(xì)節(jié)性的錯(cuò)誤。

2016-05-25 10:01:13 18

18 當(dāng)前,AI因?yàn)槠?b class="flag-6" style="color: red">CNN(卷積神經(jīng)網(wǎng)絡(luò))算法出色的表現(xiàn)在圖像識別領(lǐng)域占有舉足輕重的地位。基本的CNN算法需要大量的計(jì)算和數(shù)據(jù)重用,非常適合使用FPGA來實(shí)現(xiàn)。

2016-05-26 10:16:06 1642

1642 AI因?yàn)槠?b class="flag-6" style="color: red">CNN(卷積神經(jīng)網(wǎng)絡(luò))算法出色的表現(xiàn)在圖像識別領(lǐng)域占有舉足輕重的地位。基本的CNN算法需要大量的計(jì)算和數(shù)據(jù)重用,非常適合使用FPGA來實(shí)現(xiàn)。上個(gè)月,Ralph Wittig(Xilinx

2016-07-28 12:13:18 2643

2643 SuperVessel將包括賽靈思SDAccel開發(fā)環(huán)境,支持用C、C++和OpenCL實(shí)現(xiàn)FPGA加速 All Programmable 技術(shù)和器件的全球領(lǐng)先企業(yè)賽靈思公司與IBM公司今天聯(lián)合宣布

2017-02-08 16:06:08 494

494 基于FPGA的通用CNN加速器整體框架如下,通過Caffe/Tensorflow/Mxnet等框架訓(xùn)練出來的CNN模型,通過編譯器的一系列優(yōu)化生成模型對應(yīng)的指令;同時(shí),圖片數(shù)據(jù)和模型權(quán)重?cái)?shù)據(jù)按照優(yōu)化規(guī)則進(jìn)行預(yù)處理以及壓縮后通過PCIe下發(fā)到FPGA加速器中

2017-10-27 14:09:58 10618

10618

出于以下幾個(gè)原因,你可能會考慮使用FPGA來實(shí)現(xiàn)DSP解決方案。首先是為了提高性能,盡管今天的DSP處理器很快,并對許多DSP應(yīng)用來說很有用,但仍有一些應(yīng)用要求性能再進(jìn)一步提升,而FPGA提供了更高

2017-11-06 11:47:52 0

0 CNN已經(jīng)廣泛用于圖像識別,因?yàn)樗苣7律镆曈X神經(jīng)的行為獲得很高識別準(zhǔn)確率。最近,基于深度學(xué)習(xí)算法的現(xiàn)代應(yīng)用高速增長進(jìn)一步改善了研究和實(shí)現(xiàn)。特別地,多種基于FPGA平臺的深度CNN加速器被提出

2017-11-17 13:31:01 8767

8767 實(shí)現(xiàn)成本低,但是在數(shù)據(jù)沖突較高時(shí)會導(dǎo)致查表性能急速下降;硬件TCAM方法具有優(yōu)良的時(shí)間特性,但其價(jià)格昂貴、耗能巨大。目前,隨著基于現(xiàn)場可編程門陣列FPGA的異構(gòu)計(jì)算技術(shù)的高速發(fā)展,利用系統(tǒng)已經(jīng)提供的FPGA資源對基于軟件實(shí)現(xiàn)的Hash表結(jié)構(gòu)進(jìn)行加速成

2017-11-27 14:46:24 0

0 剛好在知乎上看到這個(gè)問題?如何用FPGA加速卷積神經(jīng)網(wǎng)絡(luò)CNN,恰巧我的碩士畢業(yè)設(shè)計(jì)做的就是在FPGA上實(shí)現(xiàn)CNN的架構(gòu),在此和大家分享。 先說一下背景,這個(gè)項(xiàng)目的目標(biāo)硬件是Xilinx的PYNQ

2018-06-29 07:55:00 5289

5289

近日KORTIQ公司推出了一款Xilinx FPGA的CNN加速器IP——AIScale,它能夠利用實(shí)現(xiàn)訓(xùn)練好的CNN網(wǎng)絡(luò),比如行業(yè)標(biāo)準(zhǔn)的ResNet、AlexNet、Tiny Yolo和VGG-16等,并將它們進(jìn)行壓縮輸出二進(jìn)制描述文件,可以部署到Xilinx全系列可編程邏輯器件上。

2018-01-09 08:45:41 10579

10579

許多工程師認(rèn)為,只要定義了 FPGA 的功能,工作就算完成了。但實(shí)際上將 FPGA 插入 PCB 時(shí)也會面臨一系列挑戰(zhàn)。 對于許多工程師和項(xiàng)目經(jīng)理來說,在 FPGA 中實(shí)現(xiàn)功能并實(shí)現(xiàn)時(shí)序收斂是主要目

2018-01-12 11:49:44 3000

3000

商湯科技算法平臺團(tuán)隊(duì)和北京大學(xué)高能效實(shí)驗(yàn)室聯(lián)合提出一種基于 FPGA 的快速Winograd算法,可以大幅降低算法復(fù)雜度,改善 FPGA 上的 CNN 性能。

2018-02-07 11:52:06 10225

10225

OpenCL 軟件開發(fā)套件來編程的、獨(dú)立的英特爾 Arria 10 FPGA 加速器,從而展示對卷積神經(jīng)網(wǎng)絡(luò) (CNN) 對象分類的 FPGA 加速能力。FPGA 接口和 IP 構(gòu)建在 BVLC

2018-07-31 09:04:00 1897

1897 Kortiq提供易于使用,可擴(kuò)展且小巧的CNN加速器。

該設(shè)備支持所有類型的CNN,并動態(tài)加速網(wǎng)絡(luò)中的不同層類型。

2018-11-23 06:28:00 3804

3804 在設(shè)計(jì)可編程門陣列(FPGA)電路時(shí),必須極端重視電源問題,從而使最終產(chǎn)品能在所有可能的條件下無缺陷工作并處于最優(yōu)狀態(tài)。FPGA 電路電源有兩項(xiàng)需考慮的問題: FPGA 電路上電要求和電路功耗分析。這篇文章針對這兩方面的要求,討論您可能遇到的問題,以及解決方案。

2019-05-31 14:39:13 3104

3104 自行科技通過多年CNN與FPGA自主研發(fā)經(jīng)驗(yàn),開發(fā)出業(yè)內(nèi)最具性價(jià)比的FPGA加速設(shè)計(jì)方案。會中,她表示,FPGA加速設(shè)計(jì)需要算法工程師和FPGA工程師共同參與。

2019-07-26 16:59:11 4841

4841 您需要以下內(nèi)容 -

2019-08-08 09:49:39 3864

3864 在廠商的大力推動下,如今的小間距LED已經(jīng)成為了大屏顯示領(lǐng)域的后起之秀,自然也就成為了諸多行業(yè)用戶的熱門選擇之一。不過,鑒于小間距LED行業(yè)剛剛崛起不久,應(yīng)用規(guī)模有限,大多數(shù)行業(yè)用戶對其了解于廠商宣傳,而為了提升自身的品牌影響力,廠商打出了五花八門的概念,這無疑讓行業(yè)用戶的認(rèn)知更加困難。選購小間距LED都應(yīng)用注意哪些要素才能確保應(yīng)用高效?

2019-11-20 15:39:03 1262

1262 隨著近些年深度學(xué)習(xí)的迅速發(fā)展和廣泛的應(yīng)用,卷積神經(jīng)網(wǎng)絡(luò)(CNN)已經(jīng)成為檢測和識別領(lǐng)域最好的方法,它可以自動地從數(shù)據(jù)集中學(xué)習(xí)提取特征,而且網(wǎng)絡(luò)層數(shù)越多,提取的特征越有全局性。通過局部連接和權(quán)值共享

2020-07-15 21:00:05 3285

3285

目前在做FPGA移植加速CNN卷積神經(jīng)網(wǎng)絡(luò)Inference相關(guān)的學(xué)習(xí),使用的是Xilinx公司的ZYNQ-7000系列的FPGA開發(fā)板,該博客為記錄相關(guān)學(xué)習(xí)內(nèi)容,如有問題歡迎指教。

2020-12-25 17:34:37 4

4 目前在做FPGA移植加速CNN卷積神經(jīng)網(wǎng)絡(luò)Inference相關(guān)的學(xué)習(xí),使用的是Xilinx公司的ZYNQ-7000系列的FPGA開發(fā)板,該博客為記錄相關(guān)學(xué)習(xí)內(nèi)容,如有問題歡迎指教。前面已經(jīng)介紹了

2020-12-25 17:34:36 23

23 PipeCNN可實(shí)現(xiàn)性 PipeCNN論文解析:用OpenCL實(shí)現(xiàn)FPGA上的大型卷積網(wǎng)絡(luò)加速 2.1 已實(shí)現(xiàn)的PipeCNN資源消耗 3. 實(shí)現(xiàn)大型神經(jīng)網(wǎng)絡(luò)的方法 4. Virtex-7高端FPGA概覽、7

2021-04-19 11:12:02 3242

3242

MATLAB實(shí)現(xiàn)卷積神經(jīng)網(wǎng)絡(luò)CNN的源代碼

2021-04-21 10:15:36 16

16 FPGA的ROM實(shí)現(xiàn)(qt嵌入式開發(fā)編程)-該文檔為FPGA的ROM實(shí)現(xiàn)簡介資料,講解的還不錯(cuò),感興趣的可以下載看看…………………………

2021-07-30 08:58:50 5

5 我們在選擇氣體檢測儀時(shí)既要考慮自己的條件還需要考慮以下的情況。

2021-08-27 10:41:53 1134

1134 設(shè)計(jì) GTXGTH收發(fā)器電源設(shè)計(jì)1.概述Xilinx 7系列FPGA GTX/GTH收發(fā)器是模擬電路,當(dāng)設(shè)計(jì)和實(shí)現(xiàn)PCB設(shè)計(jì)需要特殊考慮和注意。這其中涉及器件管腳功能、傳輸線阻抗和布線、供電設(shè)計(jì)濾波、器件選擇、PCB布線和層疊設(shè)計(jì)相關(guān)內(nèi)容。2.管腳描述和設(shè)計(jì)指導(dǎo)2.1 GTX/GTH收發(fā)器管腳描述

2021-11-06 19:51:00 35

35 出快速便捷的解決方案。

在為 FPGA 供電時(shí)需要考慮若干電源設(shè)計(jì)方面的問題,比如:

增加了輸出電壓軌數(shù)量

需要為電軌設(shè)置設(shè)定點(diǎn)精度

需要優(yōu)化設(shè)計(jì)中的無源板面布局才能實(shí)現(xiàn)極低的紋波噪聲

需要

2021-11-23 15:43:43 1670

1670 電子學(xué)報(bào)第七期《一種可配置的CNN協(xié)加速器的FPGA實(shí)現(xiàn)方法》

2021-11-18 16:31:06 15

15 經(jīng)過了前面的開胃菜,項(xiàng)目正式開始。一步步講解這個(gè)模型怎么玩起來的。從C 到 matlab 到 FPGA ,三個(gè)平臺聯(lián)合起來完成這個(gè) 由 RTL 實(shí)現(xiàn) CNN 的項(xiàng)目。

2022-03-15 17:13:24 3087

3087 本文重點(diǎn)解釋如何使用硬件轉(zhuǎn)換卷積神經(jīng)網(wǎng)絡(luò)(CNN),并特別介紹使用帶CNN硬件加速器的人工智能(AI)微控制器在物聯(lián)網(wǎng)(IoT)邊緣實(shí)現(xiàn)人工智能應(yīng)用所帶來的好處。 AI應(yīng)用通常需要消耗大量能源,并以

2023-05-16 01:05:03 1905

1905 因?yàn)?b class="flag-6" style="color: red">CNN的特有計(jì)算模式,通用處理器對于CNN實(shí)現(xiàn)效率并不高,不能滿足性能要求。 因此,近來已經(jīng)提出了基于FPGA,GPU甚至ASIC設(shè)計(jì)的各種加速器來提高CNN設(shè)計(jì)的性能。

2023-06-14 16:03:43 3135

3135

要選出物美價(jià)廉的網(wǎng)線,可以考慮以下幾個(gè)方面: 確定需求:在購買網(wǎng)線之前,需要明確自己的需求。例如,需要傳輸?shù)乃俾省?b class="flag-6" style="color: red">需要支持的網(wǎng)絡(luò)協(xié)議、需要連接的設(shè)備數(shù)量等。這些因素都會影響網(wǎng)線的選擇。 選擇合適

2023-11-17 10:50:13 1643

1643 嵌入式主板時(shí)必須注意以下幾點(diǎn)考慮。1.考慮主板上的操作系統(tǒng)工業(yè)機(jī)器控制所需的控制系統(tǒng)和設(shè)備以及相關(guān)事項(xiàng)不盡相同,但在近幾年的市場中,我國嵌入式主板的發(fā)展實(shí)力日益增強(qiáng),

2023-11-22 17:39:07 1048

1048

卷積神經(jīng)網(wǎng)絡(luò)(CNN)是深度學(xué)習(xí)領(lǐng)域中一種特別適用于圖像識別任務(wù)的神經(jīng)網(wǎng)絡(luò)結(jié)構(gòu)。它通過模擬人類視覺系統(tǒng)的處理方式,利用卷積、池化等操作,自動提取圖像中的特征,進(jìn)而實(shí)現(xiàn)高效的圖像識別。本文將從CNN的基本原理、構(gòu)建過程、訓(xùn)練策略以及應(yīng)用場景等方面,詳細(xì)闡述如何利用CNN實(shí)現(xiàn)圖像識別。

2024-07-03 16:16:16 3448

3448 選擇工控機(jī)時(shí),需要考慮的問題主要有以下幾個(gè)方面:

2024-07-26 10:11:15 624

624 FPGA(現(xiàn)場可編程門陣列)加速深度學(xué)習(xí)模型是當(dāng)前硬件加速領(lǐng)域的一個(gè)熱門研究方向。以下是一些FPGA加速深度學(xué)習(xí)模型的案例: 一、基于FPGA的AlexNet卷積運(yùn)算加速 項(xiàng)目名稱

2024-10-25 09:22:03 1856

1856 1D-CNN,還有哪些神經(jīng)網(wǎng)絡(luò)算法可以在FPGA上加速? A :以下是一個(gè)基于 FPGA 的一維卷積神經(jīng)網(wǎng)絡(luò)(1D-CNN)算法加速實(shí)現(xiàn)的案例,僅供參考: 項(xiàng)目案例概述: 該項(xiàng)目旨在通過 FPGA 實(shí)現(xiàn) 1D-CNN 的加速,以提高對一維序列數(shù)據(jù)的處理速度。項(xiàng)目先使用 Python 代碼實(shí)現(xiàn)訓(xùn)練和推

2024-12-07 10:05:27 1296

1296 度傳感器前,下面小編帶你來考慮究竟有哪些困難:您要測量或測試的動態(tài)范圍是多少?高g值測試的結(jié)果難以預(yù)測,需要仔細(xì)考慮必要的傳感器滿量程范圍。使用加速度傳感器時(shí),您需

2025-10-20 14:14:45 313

313

電子發(fā)燒友App

電子發(fā)燒友App

評論