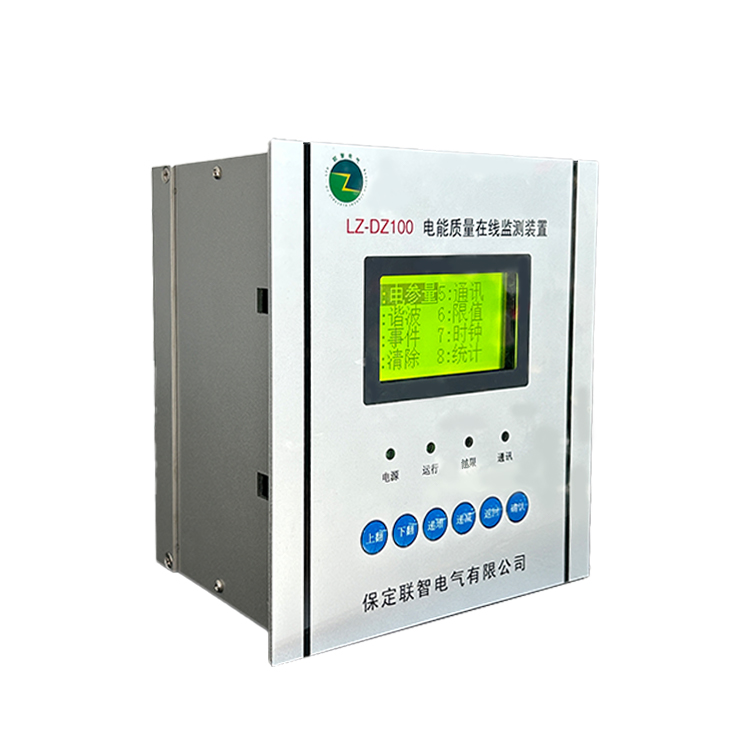

產(chǎn)品實(shí)拍圖

產(chǎn)品實(shí)拍圖

利用硬件加速提升通信協(xié)議安全性,核心是通過專用硬件模塊或可編程硬件,承接軟件層面難以高效處理的安全關(guān)鍵操作(如加密解密、認(rèn)證、密鑰管理等),在提升性能的同時(shí),通過硬件級(jí)隔離、防篡改等特性增強(qiáng)安全性(而非僅依賴軟件防護(hù))。其本質(zhì)是 “將安全計(jì)算從通用 CPU 卸載到專用硬件”,既解決軟件處理安全操作的性能瓶頸,又規(guī)避軟件層可能存在的漏洞(如內(nèi)存泄露、側(cè)信道攻擊風(fēng)險(xiǎn))。

一、硬件加速提升通信協(xié)議安全性的核心應(yīng)用場(chǎng)景

通信協(xié)議的安全性依賴加密算法(對(duì)稱 / 非對(duì)稱)、哈希校驗(yàn)、證書驗(yàn)證、密鑰存儲(chǔ)、流量過濾等環(huán)節(jié),硬件加速可針對(duì)性優(yōu)化這些場(chǎng)景:

| 安全環(huán)節(jié) | 軟件處理痛點(diǎn) | 硬件加速價(jià)值 |

|---|---|---|

| 對(duì)稱加密(AES) | 高吞吐場(chǎng)景(如 5G / 數(shù)據(jù)中心)下 CPU 占用高 | 硬件并行處理,吞吐提升 10-100 倍 |

| 非對(duì)稱加密(RSA/ECC) | 密鑰生成 / 簽名驗(yàn)證耗時(shí),影響協(xié)議握手 | 專用電路降低延遲(如 ECC 簽名從 ms 級(jí)到 μs 級(jí)) |

| 哈希運(yùn)算(SHA-256) | 大數(shù)據(jù)量完整性校驗(yàn)占用 CPU 資源 | 硬件流水線處理,減少 CPU 負(fù)載 |

| 密鑰存儲(chǔ)與管理 | 軟件存儲(chǔ)易被竊取(如內(nèi)存 dump 攻擊) | 硬件隔離存儲(chǔ)(如 SE/TPM),防物理篡改 |

| TLS/DTLS 協(xié)議卸載 | 協(xié)議握手、加密解密占用 CPU 核心 | 智能網(wǎng)卡 / NPU 直接處理 TLS 流量,CPU 專注業(yè)務(wù) |

| 側(cè)信道攻擊防護(hù) | 軟件難以規(guī)避時(shí)序 / 功耗泄露 | 硬件級(jí)恒定時(shí)間運(yùn)算(Constant-Time) |

二、常用硬件加速方案及落地方法

不同硬件方案的靈活性、性能、成本差異較大,需結(jié)合通信協(xié)議場(chǎng)景(如嵌入式設(shè)備、數(shù)據(jù)中心、工業(yè)通信)選擇,以下是主流方案及應(yīng)用方式:

1. 專用安全芯片(ASIC/ASSP):高吞吐、低功耗,適合固定場(chǎng)景

原理:通過定制化硬件電路實(shí)現(xiàn)特定安全算法(如 AES、ECC、SHA),不支持算法修改,但性能和功耗最優(yōu)。

典型場(chǎng)景:嵌入式通信(如物聯(lián)網(wǎng) LoRaWAN、工業(yè) Modbus-TCP)、移動(dòng)設(shè)備(手機(jī)基帶芯片)。

落地方法:

選擇集成安全模塊的通信芯片(如 TI 的 CC2652R(支持 AES-128 硬件加速)、高通驍龍基帶的 TLS 硬件卸載);

直接調(diào)用芯片驅(qū)動(dòng)提供的安全 API(如加密函數(shù)接口),避免軟件實(shí)現(xiàn)算法;

例如:LoRaWAN 協(xié)議的幀加密(AES-128-CTR)通過 ASIC 硬件處理,相比軟件實(shí)現(xiàn),功耗降低 50%,加密延遲從 100μs 降至 10μs。

2. 現(xiàn)場(chǎng)可編程門陣列(FPGA):靈活可編程,適合定制化場(chǎng)景

原理:通過可編程邏輯單元(LUT)搭建自定義安全電路,支持算法迭代(如從 SHA-256 升級(jí)到 SHA-3),兼顧性能與靈活性。

典型場(chǎng)景:工業(yè)通信(如 EtherCAT 安全協(xié)議)、邊緣計(jì)算網(wǎng)關(guān)(多協(xié)議兼容,如同時(shí)支持 TLS 1.3 和 OPC UA 安全層)。

落地方法:

基于 FPGA 開發(fā)工具(如 Xilinx Vivado、Intel Quartus),調(diào)用開源安全 IP 核(如 OpenCores 的 AES 核、ECC 核);

將通信協(xié)議的安全層邏輯(如 OPC UA 的證書驗(yàn)證、EtherCAT 的安全幀校驗(yàn))固化到 FPGA;

優(yōu)勢(shì):可針對(duì)特定協(xié)議優(yōu)化硬件邏輯(如工業(yè)協(xié)議的小數(shù)據(jù)包加密,減少硬件資源浪費(fèi)),同時(shí)抵御側(cè)信道攻擊(通過硬件級(jí)時(shí)序均衡設(shè)計(jì))。

3. 安全協(xié)處理器(TPM/SE/HSM):強(qiáng)隔離,聚焦密鑰安全

原理:獨(dú)立于主 CPU 的專用硬件模塊,提供密鑰隔離存儲(chǔ)、硬件級(jí)身份認(rèn)證、防篡改能力,是通信協(xié)議 “根信任” 的核心。

分類與場(chǎng)景:

TPM(可信平臺(tái)模塊):PC / 服務(wù)器標(biāo)配(如 Intel PTT、AMD fTPM),用于存儲(chǔ) TLS 客戶端證書私鑰,避免私鑰被軟件竊取;

SE(安全元件):嵌入式設(shè)備(如物聯(lián)網(wǎng)傳感器、SIM 卡),存儲(chǔ) LoRaWAN 的 DevEUI 密鑰、NB-IoT 的認(rèn)證密鑰;

HSM(硬件安全模塊):數(shù)據(jù)中心級(jí)(如 Thales HSM),用于 SSL/TLS 服務(wù)器的根密鑰管理、大規(guī)模證書簽名。

落地方法:

在通信協(xié)議的密鑰協(xié)商階段(如 TLS 握手、5G AKA 認(rèn)證),調(diào)用 TPM/SE/HSM 的密鑰生成 / 簽名接口,不將私鑰暴露到主內(nèi)存;

例如:TLS 服務(wù)器的 RSA 私鑰存儲(chǔ)在 HSM 中,握手時(shí)的簽名操作由 HSM 完成,主 CPU 僅處理協(xié)議幀轉(zhuǎn)發(fā),既防私鑰泄露,又降低 CPU 負(fù)載。

4. 智能網(wǎng)卡(Smart NIC)/DPU:協(xié)議卸載,聚焦數(shù)據(jù)中心場(chǎng)景

原理:在網(wǎng)卡中集成處理器(如 ARM 核心)和安全加速模塊,直接處理通信協(xié)議的安全層(如 TLS/DTLS),實(shí)現(xiàn) “CPU 零占用” 的安全傳輸。

典型場(chǎng)景:數(shù)據(jù)中心間的 HTTP/3(QUIC)通信、云原生環(huán)境的容器間加密通信。

落地方法:

部署支持 TLS 卸載的智能網(wǎng)卡(如 NVIDIA BlueField DPU、Intel E810 網(wǎng)卡);

通過網(wǎng)卡驅(qū)動(dòng)或軟件定義網(wǎng)絡(luò)(SDN)工具(如 Open vSwitch),將 TLS 流量引導(dǎo)至網(wǎng)卡硬件處理;

效果:數(shù)據(jù)中心內(nèi) TLS 流量的處理吞吐從 10Gbps(軟件)提升至 100Gbps(硬件),CPU 占用率從 80% 降至 5% 以下。

5. GPU:并行加速,適合大規(guī)模加密計(jì)算場(chǎng)景

原理:利用 GPU 的 thousands 級(jí)并行計(jì)算核心,加速批量安全操作(如大規(guī)模 TLS 證書驗(yàn)證、區(qū)塊鏈通信的簽名驗(yàn)證)。

典型場(chǎng)景:邊緣云的多設(shè)備接入認(rèn)證(如同時(shí)驗(yàn)證 1000 + 物聯(lián)網(wǎng)設(shè)備的 TLS 證書)、P2P 通信的批量哈希校驗(yàn)。

落地方法:

使用 CUDA(NVIDIA)或 OpenCL 框架,開發(fā)并行化的安全算法(如基于 GPU 的 AES 批量加密、SHA-256 并行計(jì)算);

例如:邊緣網(wǎng)關(guān)驗(yàn)證 1000 個(gè)物聯(lián)網(wǎng)設(shè)備的 TLS 客戶端證書,軟件實(shí)現(xiàn)需 10s,GPU 加速后僅需 0.5s。

三、實(shí)施步驟:從需求到落地的全流程

明確安全與性能需求

先定義通信協(xié)議的核心安全目標(biāo)(如是否需防側(cè)信道攻擊、密鑰是否需硬件隔離)和性能指標(biāo)(如加密吞吐、握手延遲、CPU 占用率上限),例如:

物聯(lián)網(wǎng)傳感器:需低功耗(<10mA)、AES-128 加密,選擇集成 SE 的 MCU;

數(shù)據(jù)中心 TLS 網(wǎng)關(guān):需 100Gbps 吞吐、TLS 1.3 卸載,選擇 Smart NIC/DPU。

選擇硬件加速方案

根據(jù)需求匹配硬件類型,參考以下對(duì)比表:

| 硬件類型 | 性能 | 靈活性 | 成本 | 適用場(chǎng)景 |

|---|---|---|---|---|

| ASIC/ASSP | ★★★★★ | ★☆☆☆☆ | 中高 | 固定協(xié)議(如 LoRaWAN、5G NR) |

| FPGA | ★★★★☆ | ★★★★☆ | 高 | 定制化工業(yè)協(xié)議、邊緣網(wǎng)關(guān) |

| TPM/SE/HSM | ★★☆☆☆ | ★★☆☆☆ | 低 - 高 | 密鑰存儲(chǔ)、身份認(rèn)證 |

| Smart NIC/DPU | ★★★★★ | ★★★☆☆ | 高 | 數(shù)據(jù)中心 TLS/QUIC 卸載 |

| GPU | ★★★☆☆ | ★★★☆☆ | 中 | 批量安全計(jì)算(如證書驗(yàn)證) |

協(xié)議棧集成與驅(qū)動(dòng)適配

底層:通過硬件廠商提供的 SDK / 驅(qū)動(dòng)(如 FPGA 的 IP 核驅(qū)動(dòng)、TPM 的 TSS 2.0 協(xié)議棧),將硬件加速能力暴露為標(biāo)準(zhǔn)化接口(如 OpenSSL 引擎、Linux Crypto API);

上層:修改通信協(xié)議棧代碼,調(diào)用硬件加速接口,例如:

將 TLS 協(xié)議棧(如 OpenSSL)的加密引擎切換為 “硬件加速引擎”(如 OpenSSL + Intel QAT 引擎);

在物聯(lián)網(wǎng)協(xié)議(如 MQTT-SN)的代碼中,替換軟件 AES 函數(shù)為 SE 芯片的 AES API。

安全性與性能驗(yàn)證

安全性驗(yàn)證:通過工具檢測(cè)硬件加速是否抵御特定攻擊(如用 Side Channel Attack Toolkit 檢測(cè)側(cè)信道漏洞、用 Hashcat 測(cè)試密鑰是否可被暴力破解);

性能驗(yàn)證:用通信協(xié)議評(píng)估工具(如 Wireshark、iPerf3)測(cè)試優(yōu)化前后的指標(biāo)(如 TLS 握手延遲、加密吞吐、CPU 占用率)。

四、關(guān)鍵注意事項(xiàng)

避免 “重性能、輕安全”:硬件加速的核心目標(biāo)是 “在提升性能的同時(shí)增強(qiáng)安全性”,而非僅追求速度。例如:部分低成本 ASIC 可能未做側(cè)信道防護(hù),需優(yōu)先選擇通過安全認(rèn)證(如 FIPS 140-3)的硬件。

兼容性與可擴(kuò)展性:選擇支持主流協(xié)議標(biāo)準(zhǔn)(如 TLS 1.3、AES-NI)的硬件,避免綁定特定廠商;同時(shí)預(yù)留升級(jí)空間(如 FPGA 可迭代算法、Smart NIC 支持新協(xié)議卸載)。

軟硬件協(xié)同設(shè)計(jì):硬件負(fù)責(zé) “計(jì)算密集型安全操作”(如加密、簽名),軟件負(fù)責(zé) “邏輯密集型安全策略”(如訪問控制、異常檢測(cè)),例如:Smart NIC 處理 TLS 加密,軟件層通過防火墻規(guī)則過濾惡意 TLS 流量。

通過以上方法,可在不犧牲通信協(xié)議安全性的前提下,解決軟件處理安全操作的性能瓶頸,尤其適合高吞吐、低延遲、高安全需求的場(chǎng)景(如 5G、物聯(lián)網(wǎng)、數(shù)據(jù)中心通信)。

審核編輯 黃宇

-

通信協(xié)議

+關(guān)注

關(guān)注

28文章

1093瀏覽量

42237 -

硬件加速

+關(guān)注

關(guān)注

0文章

33瀏覽量

11435

發(fā)布評(píng)論請(qǐng)先 登錄

FPGA硬件加速卡設(shè)計(jì)原理圖:1-基于Xilinx XCKU115的半高PCIe x8 硬件加速卡 PCIe半高 XCKU115-3-FLVF1924-E芯片

Xilinx FPGA串行通信協(xié)議介紹

常用硬件加速的方法

硬件加速模塊的時(shí)鐘設(shè)計(jì)

如何利用X-Ray技術(shù)提升鋰電池安全性與穩(wěn)定性

分布式能源并網(wǎng)的通信協(xié)議有哪些?

有哪些技術(shù)可以提高邊緣計(jì)算設(shè)備的安全性?

如何評(píng)估通信協(xié)議優(yōu)化對(duì)數(shù)據(jù)傳輸效率的提升效果?

有哪些方法可以確保硬件加速與通信協(xié)議的兼容性?

如何在保證數(shù)據(jù)安全的前提下優(yōu)化通信協(xié)議?

宏集分享 | 集中告警管理如何提升設(shè)施安全性?

如何利用硬件加速提升通信協(xié)議的安全性?

如何利用硬件加速提升通信協(xié)議的安全性?

評(píng)論