誤解和謊言可以歪曲人們對硬件加速仿真的認知。這些錯誤認知包括:

1.硬件加速器是幕后的驗證工具,僅用于需要更為嚴謹調試的最復雜的設計

在20世紀80年代末和90年代初硬件加速器剛出現時,這種說法的確沒錯。不過,在跨入21世紀之后,也就是過去15年來,情況全然不同。這一轉變有賴于幾次技術改進和創新。新架構、新功能和簡化的使用方法推動了硬件加速器在半導體行業各個領域的部署應用,從處理器/圖形擴展到網絡、多媒體、存儲、汽車和航空航天。

如今,硬件加速器被用于任何規模和任何類型的設計。它們可以驗證硬件、集成硬件和嵌入式軟件,也可以驗證嵌入式軟件和整個片上系統 (SoC) 設計。

2.項目團隊因為使用硬件仿真加速器編譯項目時間過長而避免使用硬件仿真加速器。在硬件仿真加速器上,建立設計平臺和調試硬件仿真加速器硬件耗費了太多精力,和結果相比,得不償失

同樣,這一說法在多年前沒錯,現在卻并非如此了。編輯技術的進步簡化并提高了被測設計(DUT)到硬件加速器的映射。DUT準備、編輯以及硬件加速器上映射設計的過程曾非常耗時,現在已從數個月縮短為幾天時間。如果設計復雜度較低或屬于新的復雜設計的衍生,甚至只需一天。

3.硬件加速器的購置和維護成本高昂

過去確實如此,如今不全然是這樣。考慮到現代硬件加速器的驗證功能和靈活性,其購置成本簡直不值一提。硬件加速器是迄今為止功能最多的驗證引擎。它具備解決最復雜的調試情景所需的性能和能力,通常包括嵌入式軟件內容。只要想想,90年代初每個門需耗費5美元,如今單位成本大約為每個門幾美分甚至更少。

雖然聽起來很奇怪,但是以周期為基礎來計算,工具的多用性使硬件加速仿真成為最廉價的驗證解決方案。

持有的成本也大幅下降。由應用工程師團隊“在幕后”操作和維護硬件加速器的時代已一去不復返。產品的可靠性得到大幅提高,降低了幾個數量級的維護成本。此外,其易用性也讓它的用途簡單明了。

4.硬件加速仿真僅用于電路內仿真 (ICE) 模式

需要了解的是,在ICE模式中,DUT被映射到硬件加速器之中,被目標系統所驅動,和最終流片出的芯片一致。這就是推動硬件加速仿真概念形成和發展的部署模式,換言之,就是通過物理目標系統產生的真實世界的激勵來測試DUT。

雖然很多用戶仍采用這一模式,但這并不是部署硬件加速器的唯一方式。除了ICE,硬件加速器還可用于多種仿真加速模式。此外,還可以通過PLI接口使用基于軟件的測試平臺驅動硬件加速器,雖然由于硬件加速受限而未得到廣泛應用,但仍可用于縮短從軟件仿真切換至硬件加速仿真的設計調用耗時。或者通過基于事務的接口(TBX或TBA)驅動硬件加速器,硬件加速系數達到與ICE相當的水平之后,這些接口的應用越來越普及,至少對于目前某些硬件加速器是這樣。將可綜合的測試平臺與DUT一起映射到硬件加速器內部之后,硬件加速器便可用于獨立模式(SAA)。它們還可以加快存儲于板上或密切關聯的內存的嵌入式軟件的驗證。此外,硬件加速器還可同時用于上述多個目的。

5.在基于事務的硬件加速模式中,硬件加速仿真毫無用處

人們對硬件加速器仍存在一種普遍的誤解,即基于事務的方法不起作用,或者與ICE相比性能有限。這一概念源于20世紀90年代末的IKOS系統并且起了作用。Mentor Graphics在收購IKOS之后改進和推動了這一技術發展,命名為TBX,作為ICE的一種可行的替代方案。

新興的仿真公司EVE(Emulation Verification Engineering)在創建時就采用硬件加速仿真作為主要部署模式。我曾在這家公司擔任過總經理和營銷副總裁。Mentor和EVE都證明了:基于事務的硬件加速模式不僅能起作用,其執行速度還能與ICE匹敵,甚至更快。

基于事務的硬件加速的另一個獨特優勢在于能夠創建一個運行DUT的虛擬測試環境,支持特殊用例分析、假設分析等ICE無法實現的功能,例如Mentor Graphics的VirtuaLAB實施。VirtuaLAB在虛擬環境中將整個目標系統制成模型,例如 USB、以太網或HDMI。

6.硬件加速器將替代HDL仿真器

這個說法不僅錯誤,而且永遠不會發生。硬件描述語言(HDL)仿真器能夠快速設置和編輯,并且具備固有的優勢——靈活而全面的設計調試功能,使其成為業內獨一無二的最佳驗證工具,但其有一個重大的局限性:在設計規模擴大到某個程度,尺寸達到數億個門時,它們會“筋疲力盡”,性能下降。硬件加速器正是在這個時候發揮作用。

假定設計規模會繼續擴大,而HDL仿真器對大規模設計的執行速度不會提高,那么硬件加速器將成為唯一可行的系統級設計驗證手段。仿真器將繼續用于知識產權(IP)和模塊級。

您可能會問,那多機仿真呢?

在多機仿真中,大規模DUT不會分解成小塊并分布到大量PC中,使一個工作站執行一小塊DUT。這種方法已被重復嘗試了25年多了,但結果并不盡如人意。

相反,多機仿真中的每個工作站會執行同一個設計的副本,和設計的大小相同。每份設計副本由功能完善且獨立的不同測試平臺執行。因此,設計規模仍起決定性作用。帶有大規模驗證平臺的多機仿真被用于回歸測試是非常流行的。

仿真器與硬件加速器的使用比率可能是80%比20%。據我估計,這個比例會在十年后反轉,變成20%比80%。

7.硬件加速仿真和FPGA原型除了名稱有別,本質并無不同。FPGA原型能夠并且將取代硬件加速器

這是個錯誤的說法。雖然硬件加速器可以使用FPGA器件(事實上有一些硬件加速器確實使用了FPGA器件),但這兩種是截然不同的工具。

FPGA原型的設計旨在實現盡可能最高的執行速度。在芯片設計的過程中,通常每一種驗證原型會針對特定的設計加速而作優化。它們犧牲了DUT映射工作、DUT調試功能(限制到最低,常常毫無用處)以及調整靈活性和多用性。它們可用于芯片成功流片之前的嵌入式軟件驗證以及最終系統驗證。

除了采用了基于定制的處理器、定制的片上硬件加速器和商用FPGA的技術,硬件加速器擁有的幾個特性將其與FPGA原型電路板或系統區別開來。例如:

硬件加速器和FPGA原型系統在DUT映射和編輯耗時方面有著天壤之別,一個以天計算,一個以月計算。

硬件加速器針對硬件調試,因此支持100%的設計可見性,不要求探針編輯。不同的硬件加速器在這個關鍵性能上存在差異,但是和FPGA相比,這些差異微不足道。

硬件加速器可用于幾個操作模式,支持從硬件驗證和硬件/軟件集成到固件/操作系統測試和系統驗證的一系列驗證目標。此外,它們還可用于多電源域設計驗證,并且可以產生支持功率估算的切換活動。

硬件加速器還是多用戶/多任務引擎。FPGA原型系統僅由一個用戶使用,一次處理一個任務。

上文所述已說明了 FPGA 原型不會取代硬件加速器的原因。

8.硬件加速器必須安裝在一個地點,不能遠程使用,例如作為數據中心資源使用

早期的硬件加速器確實如此,如今已不再是這樣。目前,所有的硬件加速器都可以遠程訪問。但是,在ICE模式中,這種方法太繁瑣,在硬件加速器上傳不同設計時需要人為監督來安裝和切換速率適配器。事實上,ICE模式的多用戶或多任務非常不利于遠程訪問部署。

盡管如此,ICE模式的多用戶、遠程訪問(TBX/TBA或SAA)和大規模配置是硬件加速仿真數據中心的基礎。顯然,高效且順利的操作需要管理軟件,這就是各種硬件加速器實施的不同之處。

9.硬件加速仿真不支持SoC中的嵌入式軟件驗證,這意味著該手段無法實現硬件/軟件協同驗證

事實完全相反。硬件加速仿真是能夠執行這項艱巨任務的唯一工具。

為驗證嵌入式軟件在底層硬件上(帶單個或多個CPU的SoC)的交互,包括固件和操作系統,驗證工程師需要以下三種要素:

周期精確的設計呈現,以跟蹤SoC中任何地方的錯誤。硬件加速器可以提供最準確的設計呈現(在這方面和真實芯片相比只是缺少了硅晶片)。

可達到數百個千赫或兆赫的極高執行速度,越快越好。硬件加速器可以實現這個速度。

硬件設計完全可見。硬件加速器提供了100%的設計可見性,雖然不同硬件加速器的訪問速度不同。

10.功率估算是一項關鍵的驗證任務,但硬件加速仿真沒有能力分析SoC的功耗

這又是一個錯誤的說法。功耗分析基于設計內部所有元素的切換活動跟蹤。設計呈現得更細致,分析就更為準確。遺憾的是,更高的粒度水平意味著會消耗更多的硬件加速器資源,從而降低其靈活性,阻礙其做出能夠改善功耗的重大設計變更。最好是從架構層級實現這一分析。

硬件加速仿真可以實現寄存器傳輸級(RTL)和現代SoC設計門級的最佳功耗分析。只有硬件加速仿真才有處理大量邏輯以及產生針對所有元素的切換活動的獨有能力。

11.所有硬件加速器都是一樣的

今天,所有硬件加速器有很多共同特性,都能夠執行任務。不過,在特定模式下,有些硬件加速器會優勝于其他硬件加速器。

從架構的角度來看,硬件加速器之間的區別在于技術基礎。以下是來自三個主要EDA供應商的三種商用產品:

基于定制處理器的架構:由IBM制定,是自1997年后經過驗證的技術,在2000-2010十年間占主導地位。優勢包括快速編輯、良好的可擴展性、在ICE模式下執行速度快、獲得來自全面的速度橋接目錄的支持,以及卓越的調試功能。缺點是在TBA模式下的執行速度有限、功耗大,并且物理尺寸比基于同等設計容量的商用FPGA的硬件加速器更大。

定制的片上硬件加速器架構:片上硬件加速器架構由一家名為Meta Systems的法國新興公司在上世紀90年代中期率先設計出來,基于高度優化的定制FPGA,這種FPGA包含能夠快速編輯的互連網絡,并且可以實現“設計即正確”的編輯。設計可視化在硅片上實現,提供100%的可見性,不要求探針編輯和快速的波形跟蹤。它有幾個缺點:需要多個工作站進行快速編輯;相比基于同等設計容量的商用FPGA的硬件加速器而言,速度更慢,物理尺寸更大。

基于商用FPGA的架構:首次使用時間是20世紀90年代,因為幾個缺點而不及基于定制處理器的架構。過去10年,超大的新一代商用FPGA幫助克服了舊的商用FPGA的很多弱點,其物理尺寸和功耗在同等設計容量的架構中均屬最小值。與其他兩種架構相比,它可以獲得更快的執行速度。最大的一個缺點是在至少1,000萬門或更低的設計中,其編輯速度低于其他兩種架構。這種設計完全可見的實現以犧牲較高的硬件仿真速度為代價。

這三種架構都具備可擴展性,能夠處理任何設計規模,小至IP模塊,大到超過十億門級的整個系統。它們支持多用戶,其中,基于定制處理器的架構可以容納最多的用戶。它們還支持所有部署模式和驗證目標。

-

寄存器

+關注

關注

31文章

5612瀏覽量

130198 -

加速器

+關注

關注

2文章

839瀏覽量

40165

發布評論請先 登錄

FPGA硬件加速卡設計原理圖:1-基于Xilinx XCKU115的半高PCIe x8 硬件加速卡 PCIe半高 XCKU115-3-FLVF1924-E芯片

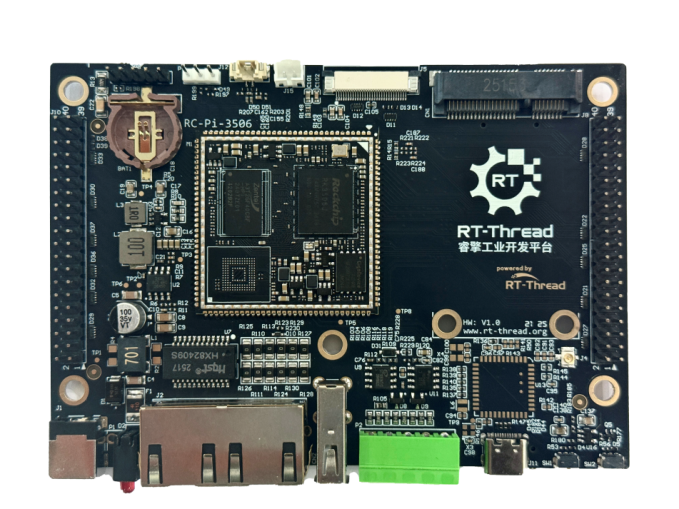

一文掌握瑞芯微RK系列NPU算子支持全景:覆蓋6大平臺,新增硬件加速算子,嵌入式AI開發不踩坑

長距傳輸,安全無憂——探秘NPB 2.0中的硬件MACsec技術

【產品介紹】Modelsim:HDL語言仿真軟件

常用硬件加速的方法

軟硬件協同技術分享 - 任務劃分 + 自定義指令集

硬件加速模塊的時鐘設計

CICC2033神經網絡部署相關操作

睿擎SDK V1.5.0重磅升級:EtherCAT低抖動,AMP虛擬網卡,LVGL硬件加速,多核調試等性能大幅提升|產品動態

硬核加速,軟硬協同!混合仿真賦能RISC-V芯片敏捷開發

如何驗證硬件加速是否真正提升了通信協議的安全性?

有哪些方法可以確保硬件加速與通信協議的兼容性?

如何利用硬件加速提升通信協議的安全性?

推動硬件輔助驗證平臺增長的關鍵因素

大規模硬件仿真系統的編譯挑戰

分享硬件加速仿真的 11 個謬論介紹和說明

分享硬件加速仿真的 11 個謬論介紹和說明

評論