概述

此項目解釋了如何在FPGA上使用resizer IP來調整圖像的大小。其中對比了兩種圖像大小調整的解決方案的運算速度,其中之一為使用Python Image Library通過軟件算法實現圖像大小調整,另一種使用Xilinx xfopencv library實現了在FPGA上硬件加速的圖像大小調整。

初始化

1. 首先在SD卡內配置Pynq-Z2最新鏡像PYNQ image v2.5并燒錄在其中

2. 根據pynq.io上的官方指南配置環境

(https://pynq.readthedocs.io/en/latest/getting_started/pynq_z2_setup.html)

根據數字編號依次連接并點亮板卡,最后在板卡出現BTN0~BTN3同時點亮閃爍一次后為開機完成狀態。

3. 在筆記本電腦上配置網絡,使得無線網卡的上網功能與Pynq-Z2連接的以太網網口共享,以做到Pynq-Z2同時能夠上網。

4. 借用Xshell或者開源軟件PuTTY對于Pynq-Z2端口進行SSH獲得其新ip口,此時其一般會被重定向至192.168.137.X。此時在瀏覽器內登錄此ip即可通過Jupyter Notebook與Pynq-Z2板卡通信。

5. 在Jupyter Notebook中新建terminal并ping 182.61.200.6驗證與百度的連接是否正常上述驗證完成后即為Pynq-Z2板卡與網絡的基礎通信功能與配置完成。

快速開始

在Jupyter Notebook的Terminal中輸入以下指令:

sudo pip3 install --upgrade git+

https://github.com/xilinx/pynq-helloworld.git

更新在Pynq-Z2內所有Packages并從github下載本次項目的代碼。

(更新需要耐心等待一定時間。)

(項目Github文件及其詳細代碼請點擊查看原文)

案例測試

1. 最終會在Files文件夾下生成名為helloworld/的文件夾,點開此文件夾可以看到兩個Jupyter Notebook文件(.ipynb)。

2. 其中resizer_PS.ipynb的軟件方案采用了Python內建的Python Imaging Library通過軟件上的算法實現完成對于一張640*360的sample圖像壓縮為原圖像的四分之一大小(320*180)。此軟件方案通過PIL庫加載與重置圖像的大小,用numpy庫存儲圖像的像素矩陣,用IPython.display在Jupyter notebook中顯示圖像。

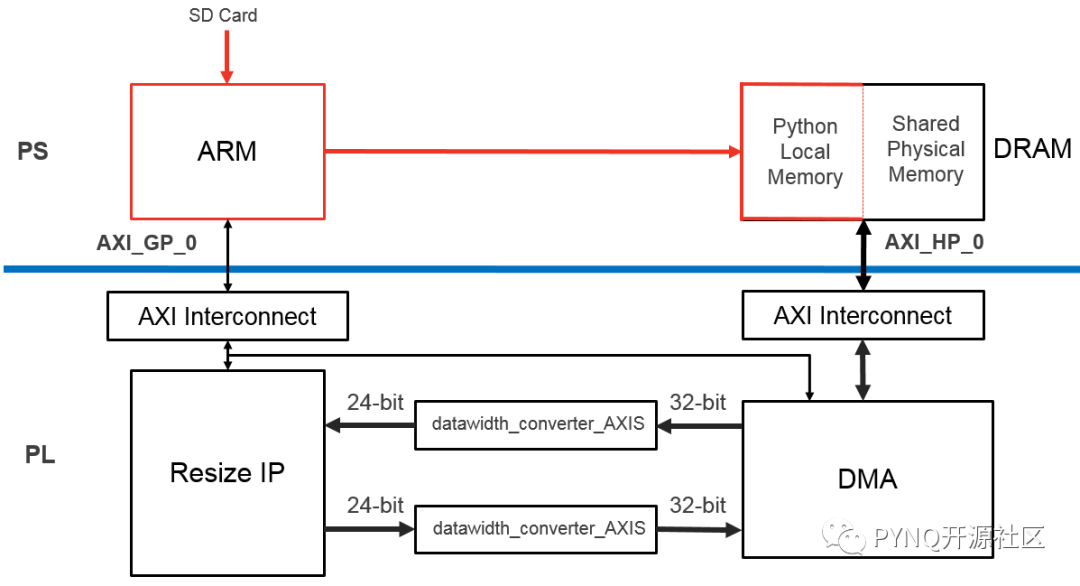

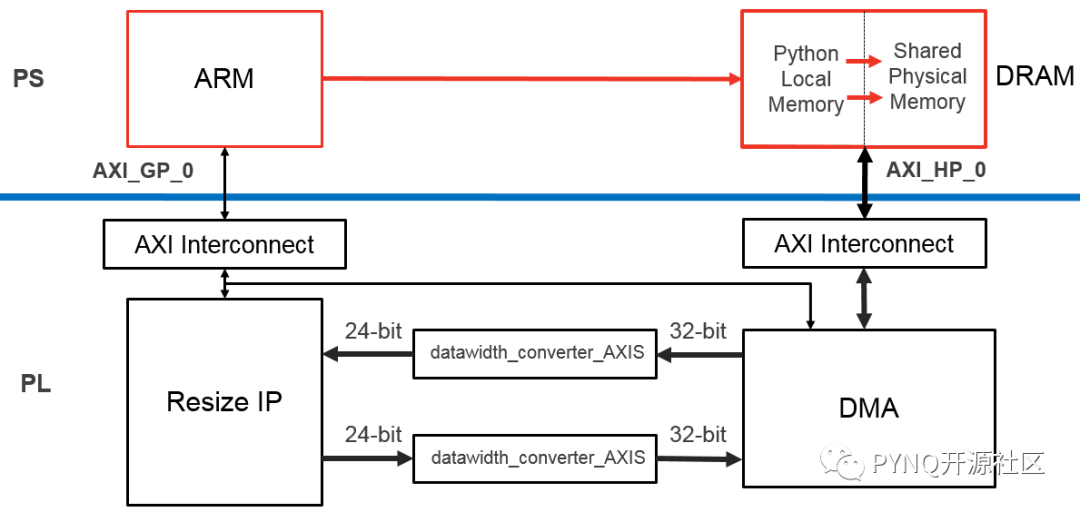

3. 而resizer_PL.ipynb的FPGA硬件方案并沒有直接在ARM核中單純采用算法借用Python本地的內存進行運算后直接返回。而是先將圖片數據通過ARM核從SD卡中讀入,再以數據流的形式通過Python的本地內存的DRAM形式傳入共享的物理內存中。

最后,在縮小圖片的演示最后我們可以看到PS方案得到的最快單次圖像處理為24.1ms,而在PL方案中最快單次圖像處理僅僅為8.95ms,在此實際圖像案例上處理圖像的時間效率上縮小了接近2.7倍。如果放至更多張更高像素的圖片,相信此圖像處理方案會有著較大優勢。

-

FPGA

+關注

關注

1660文章

22412瀏覽量

636284 -

圖像處理

+關注

關注

29文章

1342瀏覽量

59512 -

Xilinx

+關注

關注

73文章

2200瀏覽量

131129 -

python

+關注

關注

57文章

4876瀏覽量

90029

發布評論請先 登錄

FPGA硬件加速卡設計原理圖:1-基于Xilinx XCKU115的半高PCIe x8 硬件加速卡 PCIe半高 XCKU115-3-FLVF1924-E芯片

FPGA和GPU加速的視覺SLAM系統中特征檢測器研究

常用硬件加速的方法

硬件加速模塊的時鐘設計

睿擎SDK V1.5.0重磅升級:EtherCAT低抖動,AMP虛擬網卡,LVGL硬件加速,多核調試等性能大幅提升|產品動態

如何驗證硬件加速是否真正提升了通信協議的安全性?

有哪些方法可以確保硬件加速與通信協議的兼容性?

如何利用硬件加速提升通信協議的安全性?

【米爾MYC-YM90X安路飛龍DR1開發板】HMI人機界面開發

基于FPGA的壓縮算法加速實現

推動硬件輔助驗證平臺增長的關鍵因素

FPGA硬件加速的圖像大小調整案例分析

FPGA硬件加速的圖像大小調整案例分析

評論