隨著現代電子系統的不斷發展,時鐘管理成為影響系統性能、穩定性和電磁兼容性(EMI)的關鍵因素之一。在FPGA設計中,PLL因其高精度、靈活性和可編程性而得到廣泛應用,本文將深入探討PLL技術在FPGA中的動態調頻與展頻功能應用。

2025-06-20 11:51:12 2360

2360

對FPGA設計中常用的復位設計方法進行了分類、分析和比較。針對FPGA在復位過程中存在不可靠復位的現象,提出了提高復位設計可靠性的4種方法,包括清除復位信號上的毛刺、異步復位同步釋放、采用專用全局

2014-08-28 17:10:03 9365

9365 本文描述了復位的定義,分類及不同復位設計的影響,并討論了針對FPGA和CPLD的內部自復位方案。

2016-07-11 14:33:49 7289

7289

最近看advanced fpga 以及fpga設計實戰演練中有講到復位電路的設計,才知道復位電路有這么多的門道,而不是簡單的外界信號輸入系統復位。

2020-09-01 15:37:07 2079

2079

: ① 首先,上電后肯定是要復位一下,不然仿真時會出現沒有初值的情況; ② 最好有個復位的按鍵,在調試時按一下復位鍵就可以全局復位了; ③ 也許是同步復位,也許是異步復位,不同的工程師可能有不同的方案。 但

2020-11-18 17:32:38 6564

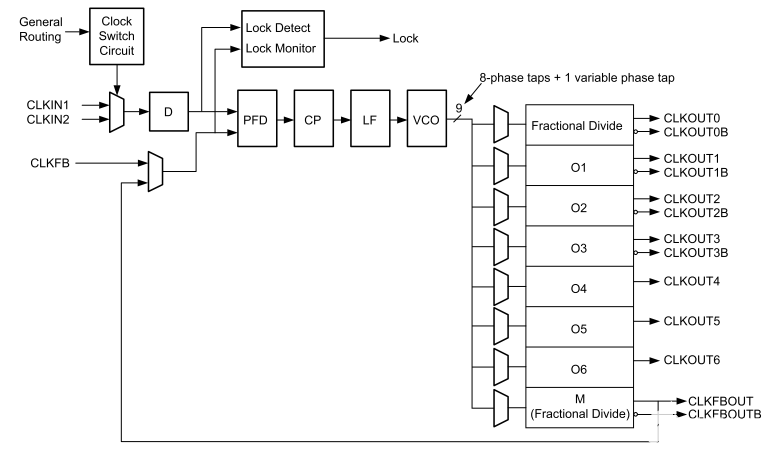

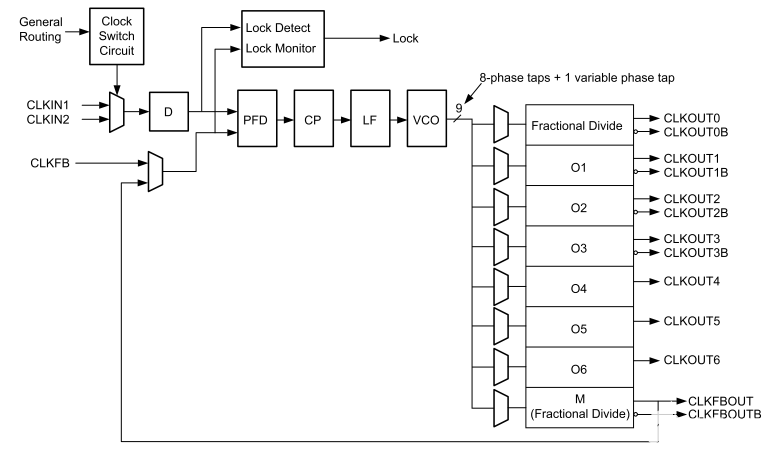

6564 PLL(phase-locked loop),即鎖相環。是FPGA中的重要資源。由于一個復雜的FPGA系統往往需要多個不同頻率,相位的時鐘信號。所以,一個FPGA芯片中PLL的數量是衡量FPGA芯片

2021-01-22 09:41:11 5920

5920

在FPGA設計中,復位電路是非常重要的一部分,它能夠確保系統從初始狀態開始啟動并保證正確運行。本文將分別介紹FPGA中三種常用復位電路:同步復位、異步復位和異步復位同步釋放,以及相應的Verilog代碼示例。

2023-05-14 14:44:49 3405

3405

在FPGA設計中,當復位整個系統或功能模塊時,需要將先關寄存器被清零或者賦初值,以保證整個系統或功能運行正常。在大部分的設計中,我們經常用“同步復位”或“異步復位”直接將所有的寄存器全部復位,這部分可能大家都習以為常。但實際上,是否需要每個寄存器都進行復位呢?這是一個值得探討的問題。

2023-05-14 14:49:19 3131

3131

上文XILINX FPGA IP之Clocking Wizard詳解說到時鐘IP的支持動態重配的,本節介紹通過DRP進行MMCM PLL的重新配置。

2023-06-12 18:24:03 16812

16812

針對異步復位、同步釋放,一直沒搞明白在使用同步化以后的復位信號時,到底是使用同步復位還是異步復位?

2023-06-21 09:59:15 2281

2281

TJ375已經支持PLL的動態配置。打開PLL在Advance Settings中的Dynamic Reconfiguration中勾選Enable就可以了。最大可以支持85組配置參數。動態配置框圖

2025-07-14 18:14:01 3113

3113

。輸入 PLL1 參考時鐘設置為 100MHz。 問題是由于更改DLYDIV_SEL 是重新配置PLL,是否必須遵循19.6.4.3 中定義的PLL 復位和重新配置流程?在更改 PLL

2023-04-18 08:25:33

Flash進行上電加載,在系統上電穩定后,FPGA器件首先需要足夠的時間用于配置加載操作,只有在這個過程結束之后,FPGA器件才能夠進入正常的用戶運行模式。而上電復位延時過短,等同于FPGA器件根本

2019-04-12 06:35:31

在配置PLL過程中,打開了megawizard plug-in manager后,下拉菜單中沒有IO這個選項,更別說選ATLPLL了,求問這是什么情況!PLL配置教程原帖http

2017-03-22 09:58:41

或Flash進行上電加載,在系統上電穩定后,FPGA器件首先需要足夠的時間用于配置加載操作,只有在這個過程結束之后,FPGA器件才能夠進入正常的用戶運行模式。而上電復位延時過短,等同于FPGA器件根本

2015-04-10 13:59:23

FPGA器件啟動后的配置加載時間,這樣才能夠確保FPGA運行后的復位初始化過程有效。因此,我們也可以來看看這個電路的設計是否滿足實際要求。(特權同學,版權所有)如圖3.19所示,這是器件手冊中關于上電配置

2015-04-24 08:17:00

系統誤復位。內部復位,FPGA上電配置完成后,由FPGA內部電路產生復位信號,復位信號與時鐘同步。通常內部復位的設計方法是:設計一個初始值為0X0000的SRL16,將其輸人接高電平,輸出作為復位信號

2021-06-30 07:00:00

PLL后復位問題怎么解決?

2021-05-08 08:48:55

如何用PLL對時鐘進行配置呢?PLL配置時鐘喚醒后還需要重新配置RCC嗎?

2021-11-22 06:30:33

你好,我想使用特定的FPGA(V5或V6)。在特殊條件下,FPGA應在復位或丟失與電源的連接后重新編程。這應該通過使用PROM自動完成。該舞會將在董事會中進行整合。現在我正在使用ML507 EV板

2020-06-10 10:24:51

;2.2)初始化配置中ENSM為TDD模式,初始化后查詢發現BBPLL和 RF Rx PLL都是Locked,但是Tx PLL不是Locked,配置狀態機進入 TDD Tx,頻譜出來的信號頻點不對

2018-08-22 09:19:41

。通過寫寄存器將AD9364狀態置為FDD狀態時(reg[0x017]=0x1A),發現FPGA內部PLL不能保持鎖定狀態了。 請教大家哪個寄存器的配置有問題會造成上述現象?附件1.png17.2 KB

2018-08-20 07:20:29

Altera可重配置PLL使用手冊在實際應用中,FPGA的工作時鐘頻率可能在幾個時間段內變動,對于與之相關的鎖相環(PLL),若PLL的輸入時鐘在初始設定的時鐘頻率的基礎上變化不太大時,PLL一般

2009-12-22 11:27:13

1. DSP上電復位配置什么? DSP的大、小端,自啟動(boot)模式,PCIe模式,網絡協處理器時鐘選擇需要在上電復位的時候選擇,怎么選擇? 依靠上電時候鎖定DSP Device

2020-12-14 16:01:54

輸出時鐘占空比不同的功能。保持默認:50。點擊Next。選擇輸入輸出端口,這里RESET為復位端口,高電平有效。LOCKED為輸出有效端口,此端口可以看到PLL輸出穩定的時間段。此界面配置輸入輸出抽頭

2023-04-06 16:04:21

,ADC值相差不大,但是采用PLL異步時鐘,復位后有概率ADC采樣值發生偏差(所以我懷疑復位后ADC時鐘出現了問題)。

補充:問題芯片具體是L431RCT6,我還有一塊L431CCT6的芯片,同樣的配置,同樣的代碼邏輯,ADC采樣值就很準確且穩定。

以下是時鐘樹與ADC配置(PLL時鐘)

2024-03-08 07:32:15

、5dBm正弦波,從CLKin1輸入。通過FPGA抓取芯片IO輸出的PLL_DLD信號。發現PLL1偶爾會失鎖,失鎖后大約0.16ms再鎖定;PLL2始終鎖定。請問PLL1失鎖的原因可能是什么,是否是配置不對。

2024-11-11 06:54:20

在使用中我發現在Autostart啟用時,將LMK61E07由100M配置為125M后實際輸出頻率為130M+。

在未啟用Autostart時復位PLL并重新置位Autostart或置位

2024-11-11 06:44:29

最近在使用STM32F407系列,當使用HSI時鐘后,PLL最高只能配置到42MHz,找了很多文檔也沒有介紹這方面的資料。如果超過42Mhz,就會發生跑飛的情況。我也試過配置到48MHz,也是會跑飛

2024-04-26 07:49:34

方法:1.生成hex文件,方法如下圖:2.生成的hex文件后綴為.hexout,改為.hex,然后把BOOT0插針短路,按鍵復位單片機,單片機串口連接電腦;3.使用STM32CubeProgrammer軟件固化FPGA程序,方法如圖:4.下載成功后,去掉BOOT0跳線帽,按鍵復位單片機

2021-11-26 07:32:14

進了STOP模式后,PLL停掉了,所以,如果開始的時鐘配置,用的是PLL,那么喚醒后,需要重新配置RCC。如果使用的是PLL,及時是用MSI作為時鐘源,放大出來的,比如4M的MSI,PLL放大到

2021-08-18 08:17:53

Xilinx FPGA入門連載24:PLL實例之基本配置 1 工程移植可以復制上一個實例sp6ex7的整個工程文件夾,更名為sp6ex8。然后在ISE中打開這個新的工程。 2 新建IP核文件

2019-01-21 21:33:40

`Xilinx FPGA入門連載17:PWM蜂鳴器驅動之復位與FPGA重配置功能特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm1 復位

2015-10-26 12:05:15

內部的各個功能模塊使用。 2 功能簡介如圖所示,本實例將用到FPGA內部的PLL資源,輸入FPGA引腳上的25MHz時鐘,配置PLL使其輸出4路分別為12.5MHz、25MHz、50MHz

2015-11-10 08:44:06

`Xilinx FPGA入門連載24:PLL實例之基本配置特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 工程移植可以復制上一個實例

2015-11-16 12:09:56

如題,ad9689的型號是2.6G,按照文檔81頁的配置方式將AD9689配置完成,讀取0x056f檢測AD的PLL鎖定,

工作的采樣率為2.2G,給AD的輸入時鐘是2.2G,給FPGA

2023-12-06 06:52:08

quartus中PLL的復位是高電平復位還是低電平復位,可不可以修改

2014-03-21 11:10:25

`PLL鎖相環介紹與簡單應用實驗目的:1.學會配置Altera提供的PLL IP核并進行仿真了解其接口時序2.利用參數化設計一個簡易的系統進行驗證已配置好的PLL實驗平臺:芯航線FPGA學習套件主板

2017-01-05 00:00:52

穩定后,FPGA器件首先需要足夠的時間用于配置加載操作,只有在這個過程結束之后,FPGA器件才能夠進入正常的用戶運行模式。而上電復位延時過短,等同于FPGA器件根本就沒有復位過程;當然了,如果上電復位

2016-07-25 15:19:04

的RC電路,也是連接到FPGA的專用輸入時鐘引腳,走內部全局時鐘網絡。 圖2.16 FPGA時鐘和復位電路FPGA上電復位時間需要大于FPGA器件啟動后的配置加載時間,這樣才能夠確保FPGA運行后的復位

2016-08-08 17:31:40

的效果。該實例的功能框圖如圖3.1所示。FPGA外部引腳的復位信號進入FPGA后,首先做了一次“異步復位,同步釋放”的處理,然后這個復位信號輸入到PLL模塊,在PLL模塊輸出時鐘有效后,它的鎖定信號

2016-09-09 18:29:24

`例說FPGA連載31:PLL例化配置與LED之PLL的IP核配置特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc 本實例使用了一個

2016-09-12 17:31:43

8.17所示,本實例將用到FPGA內部的PLL資源,輸入FPGA引腳上的25MHz時鐘,配置PLL使其輸出4路分別為12.5MHz、25MHz、50MHz和100MHz的時鐘信號,這4路時鐘信號又分

2018-04-19 19:00:56

`勇敢的芯伴你玩轉Altera FPGA連載63:PLL IP核創建于配置特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1i5LMUUD 可以復制上一個

2018-04-20 21:45:06

PLL 配置后是否按預期工作,我該怎么做。 EVAL 板上是否有任何測試點,我可以用它來進行測距和測試,或者我是否需要配置 ECO_OUT 以測量 160Mhz 頻率。 在 ECO_OUT 測試時,我只能看到 16Mhz 的脈沖。

您能提出測試方法嗎?

2024-05-20 07:07:59

_clk,把FPGA的系統時鐘50Mhz連接到pll_clk的inclk0,系統復位信號連接到pll_clk的areset,因為鎖相環是高電平復位,而輸入的系統復位信號sys_rst_n是低電平復位,所以在

2020-07-30 14:58:52

本人做課設,想用FPGA輸出一個方波作為時鐘信號,使用FPGA的是Altera公司的EP1C12Q240I7,配置芯片是EPCS4I8,我用QuartusII下載了程序之后,發現只有上電和手動復位后

2016-12-08 16:20:03

的IP核,通過這個IP核,我們可以配置一個PLL用于對FPGA外部輸入時鐘做各種分頻或倍頻處理。點擊Clocking Wizard后將彈出相應的配置頁面。圖 Clocking Wizard IP核

2019-09-06 08:13:18

C6713 PLL1、硬件外部有個復位鍵,RESET,PLL配置時有個和PLL_reset,這兩個是什么關系呢?沒什么聯系吧?2、PLL配置時,比如lock過程,需要有計時,等待PLL穩定,這個計時

2018-07-25 06:18:41

請問,想通過FPGA的PLL倍頻產生個500MHz的時鐘來使用,以此時鐘來做定時精密延遲,不知道PLL倍頻倍數有什么要求,比如好像有的器件支持不到500MHz,有沒有可推薦的器件呢

補充內容 (2017-1-4 09:26):

或者有大神用過類似能到500MHz的FPGA推薦么

2017-01-03 17:04:23

本文檔主要是以Altera公司的Stratix II系列的FPGA器件為例,介紹了其內嵌的增強型可重配置PLL在不同的輸入時鐘頻率之間的動態適應,其目的是通過提供PLL的重配置功能,使得不需要對

2010-11-02 15:17:24 27

27 在開始查找PLL的最佳配置之前,需要考慮的是如何才能為PLL找到配置。具體而言,我們應找到PLL針對給定參考振蕩器和所需輸出頻率所使用的所有可行配置。只有在確保獲得能夠滿足需

2012-11-22 10:34:32 7871

7871 FPGA Cyclone器件中PLL的配置方法

2016-02-23 11:04:13 5

5 在Xilinx 的FPGA器件中,全局的復位/置位信號(Global Set/Reset (GSR))(可以通過全局復位管腳引入)是幾乎絕對可靠的,因為它是芯片內部的信號。

2017-02-11 11:46:19 1232

1232

在FPGA設計中,復位起到的是同步信號的作用,能夠將所有的存儲元件設置成已知狀態。在數字電路設計中,設計人員一般把全局復位作為一個外部引腳來實現,在加電的時候初始化設計。全局復位引腳與任何其它輸入

2017-11-22 17:03:45 6340

6340

外電路編程FPGA或是編程Flash器件(包括EPCS和Flash),然后控制FPGA的配置復位引腳來復位整個FPGA,最后FPGA采用主串方式進行自我配置。另一種是,通過FPGA中的Nios CPU或是

2017-12-13 13:58:10 26639

26639

異步復位同步釋放 首先要說一下同步復位與異步復位的區別。 同步復位是指復位信號在時鐘的上升沿或者下降沿才能起作用,而異步復位則是即時生效,與時鐘無關。異步復位的好處是速度快。 再來談一下為什么FPGA設計中要用異步復位同步釋放。

2018-06-07 02:46:00 2563

2563 下面我們來看本實例如何配置一個PLL硬核IP,并將其集成到工程中。如圖8.18所示,在新建的工程中,點擊菜單“ToolsàMegaWizard Plug-In Manager”。

2018-04-24 11:30:02 7797

7797

對于xilinx 7系列的FPGA而言,flip-flop支持高有效的異步復/置位和同步復位/置位。對普通邏輯設計,同步復位和異步復位沒有區別,當然由于器件內部信號均為高有效,因此推薦使用高有效的控制信號,最好使用高有效的同步復位。輸入復位信號的低有效在頂層放置反相器可以被吸收到IOB中。

2018-07-13 09:31:00 7577

7577 在實際設計中,由于外部阻容復位時間短,可能無法使FPGA內部復位到理想的狀態,所以今天介紹一下網上流行的復位邏輯。

2018-08-07 09:17:18 12506

12506 FPGA的可靠復位是保證系統能夠正常工作的必要條件,本文對FPGA設計中常用的復位設計方法進行了分類、分析和比較,并針對各種復位方式的特點,提出了如何提高復位設計可靠性的方法。

2018-08-08 15:14:23 12709

12709 主設備可以為控制器,CPLD等等。當然FPGA也支持通過JTAG的方式進行程序下載,同時也可以通過JTAG進行FPGA時序抓取。 FPGA的配置過程包括以下幾方面:復位,程序加載,初始化,最后進入用戶

2018-11-18 18:05:01 831

831 一開始接觸到FPGA,肯定都知道”復位“,即簡單又復雜。簡單是因為初學時,只需要按照固定的套路——按鍵開關復位,見寄存器就先低電平復位一次,這樣一般情況可以解決99%的問題,甚至簡單的設計,就不可能有問題。

2019-02-17 10:49:53 8909

8909

FPGA設計中,層次結構設計和復位策略影響著FPGA的時序。在高速設計時,合理的層次結構設計與正確的復位策略可以優化時序,提高運行頻率。

2019-02-15 15:15:53 1270

1270 最近看 advanced fpga 以及 fpga 設計實戰演練中有講到復位電路的設計,才知道復位電路有這么多的門道,而不是簡單的外界信號輸入系統復位。 流程: 1. 異步復位: 優點:⑴大多數

2020-10-30 12:17:55 951

951 最近看 advanced fpga 以及 fpga 設計實戰演練中有講到復位電路的設計,才知道復位電路有這么多的門道,而不是簡單的外界信號輸入系統復位。

2020-12-22 12:54:00 13

13 本文檔的主要內容詳細介紹的是在FPGA上編寫通過SPI總線配置外部PLL芯片AD9518和ADC9268的程序免費下載。

2021-03-10 15:50:00 61

61 FPGA 主動方式:由 FPGA來主動輸出控制和同步信號給 FPGA的串行配置芯片(EPCS系列) ,配置芯片收到命令后,把配置數據發給 FPGA,完成配 置過程;在 AS模式下,FPGA必須

2021-04-06 15:33:02 8

8 針對異步復位、同步釋放,一直沒搞明白在使用同步化以后的復位信號時,到底是使用同步復位還是異步復位?

2021-04-27 18:12:10 5626

5626

在FPGA中配置PLL的步驟及使用方法

2021-05-28 10:01:17 21

21 基于FPGA的小波濾波抑制復位噪聲方法

2021-07-01 14:42:09 24

24 。 FPGA器件配置方式分三大類:主動配置、被動配置和JTAG配置。 主動配置:由FPGA器件引導配置操作過程。 被動配置:由計算機或控制器控制配置過程。上電后,控制器件或主控器把存儲在外部存儲器中的數據送入FPGA器件內,配置完成之后將對器件I/O和寄存器進行初始化。初始化完成后,進入用戶

2021-09-06 09:41:56 7483

7483 在FPGA上編寫的通過SPI總線配置外部PLL芯片AD9518和ADC9268的程序(開關電源技術與設計潘永雄.pdf)-在FPGA上編寫的通過SPI總線配置外部PLL芯片AD9518和ADC9268的程序,適合感興趣的人學習參考

2021-09-16 11:37:05 66

66 方法:1.生成hex文件,方法如下圖:2.生成的hex文件后綴為.hexout,改為.hex,然后把BOOT0插針短路,按鍵復位單片機,單片機串口連接電腦;3.使用STM32CubeProgrammer軟件固化FPGA程序,方法如圖:4.下載成功后,去掉BOOT0跳線帽,按鍵復位單片機

2021-11-18 20:06:02 18

18 項目場景:STM32下載后無法自動復位,需手動復位下載程序時,勾選reset and run后仍不可自動復位問題描述:STM32下載后無法自動復位,需手動復位下載程序時,勾選reset and run后仍不可自動復位原因分析:未知解決方案:取消勾選Enable即解決問題。...

2022-01-17 12:36:51 11

11 AGM FPGA 在配置成功時,PLL 已經完成鎖定,lock 信號已經變高;如果原設計中用 lock 信

號輸出實現系統 reset 的復位功能,就不能正確完成上電復位;同時,為了保證 PLL

2022-08-23 14:21:47 0

0 電子發燒友網站提供《EF3 PLL動態配置.pdf》資料免費下載

2022-09-27 10:26:04 1

1 電子發燒友網站提供《ELF2 FPGA PLL動態配置.pdf》資料免費下載

2022-09-26 15:13:06 1

1 有人說FPGA不需要上電復位電路,因為內部自帶上電復位信號。也有人說FPGA最好加一個上電復位電路,保證程序能夠正常地執行。不管是什么樣的結果,這里先把一些常用的FPGA復位電路例舉出來,以作公示。

2023-03-13 10:29:49 4846

4846 FPGA設計中幾乎不可避免地會用到復位信號,無論是同步復位還是異步復位。我們需要清楚的是復位信號對時序收斂、資源利用率以及布線擁塞都有很大的影響。

2023-03-30 09:55:34 1882

1882 本系列整理數字系統設計的相關知識體系架構,為了方便后續自己查閱與求職準備。在FPGA和ASIC設計中,對于復位這個問題可以算是老生常談了,但是也是最容易忽略的點。本文結合FPGA的相關示例,再談一談復位。

2023-05-12 16:37:18 6199

6199

在FPGA設計中,復位電路是非常重要的一部分,它能夠確保系統從初始狀態開始啟動并保證正確運行。

2023-05-22 14:21:08 1907

1907

有人說FPGA不需要上電復位電路,因為內部自帶上電復位信號。也有人說FPGA最好加一個上電復位電路,保證程序能夠正常地執行。不管是什么樣的結果,這里先把一些常用的FPGA復位電路例舉出來,以作公示。

2023-05-25 15:50:45 4510

4510

應用中得到廣泛采用。汽車場景中攝像頭系統的快速啟動時間要求就是很好的一個例子——車輛啟動后后視圖像在儀表板顯示屏上的顯示速度是最為突出的設計挑戰。 上電后,FPGA立即加載存儲于NOR器件中的配置比特流。傳輸完成后,FPGA轉換為活動(已配置)狀態。FP

2023-08-15 13:55:02 1338

1338

電子發燒友網站提供《使用STARTUPE3對并行NOR閃存進行配置后訪問的UltraScale FPGA應用說明.pdf》資料免費下載

2023-09-14 15:18:20 8

8 pll鎖相環的作用 pll鎖相環的三種配置模式? PLL鎖相環是現代電子技術中廣泛應用的一種電路,它的作用是將一個特定頻率的輸入信號轉換為固定頻率的輸出信號。PLL鎖相環的三種配置模式分別為

2023-10-13 17:39:48 5281

5281 FPGA(Field-Programmable Gate Array,現場可編程門陣列)中的復位操作是設計過程中不可或缺的一環,它負責將電路恢復到初始狀態,以確保系統的正確啟動和穩定運行。在FPGA設計中,復位方式主要分為同步復位和異步復位兩種。以下是對這兩種復位方式的詳細探討。

2024-07-17 11:12:21 3320

3320 電子發燒友網站提供《使用離散邏輯的可配置定時復位.pdf》資料免費下載

2024-09-03 10:16:26 1

1 電子發燒友網站提供《音頻設備的PLL和時鐘配置應用說明.pdf》資料免費下載

2024-09-14 10:38:29 0

0 每次在系統掉電之后,之前載入的程序將會丟失,系統上電后需要重新配置。設計者為了彌補這項缺陷,在FPGA芯片的旁邊都會設置一個flash(掉電不丟失)。

2024-10-24 18:13:41 1988

1988

在 FPGA 設計中,復位起到的是同步信號的作用,能夠將所有的存儲元件設置成已知狀態。在數字電路設計中,設計人員一般把全局復位作為一個外部引腳來實現,在加電的時候初始化設計。全局復位引腳與任何

2024-11-16 10:18:13 1804

1804

易靈思的FPGA在生成PLL的方式與別的廠家稍有區別,這與其的core和interface架構是相對應的。對于易靈思的FPGA來講,PLL,GPIO,MIPI,LVDS和DDR相對于core部分都是

2025-06-07 16:18:40 1205

1205

電子發燒友App

電子發燒友App

評論