Xilinx 復位準則:Xilinx FPGA復位策略

(1)盡量少使用復位,特別是少用全局復位,能不用復位就不用,一定要用復位的使用局部復位;

(2)如果必須要復位,在同步和異步復位上,則盡量使用同步復位,一定要用異步復位的地方,采用“異步復位、同步釋放”;

(3)復位電平選擇高電平復位;

(這里說明,由于 Altera 和 Xilinx 器件內部結構的不同,Altera 的 FPGA 推薦低電平復位)

一、異步復位同步釋放

針對異步復位、同步釋放,一直沒搞明白在使用同步化以后的復位信號時,到底是使用同步復位還是異步復位?

比如針對輸入的異步復位信號rst,使用本地時鐘clk將其同步化以后得到一個新的復位信號sys_rst,當使用sys_rst時,是將sys_rst作為同步復位信號還是異步復位信號?

always @(posedge clk or posedge rst) begin if(rst)begin rst_r0 《 = 1‘b1; rst_r1 《 = 1’b1; end else begin rst_r0 《 = 1‘b0; rst_r1 《 = rst_r0; end end assign sys_rst = rst_r1;

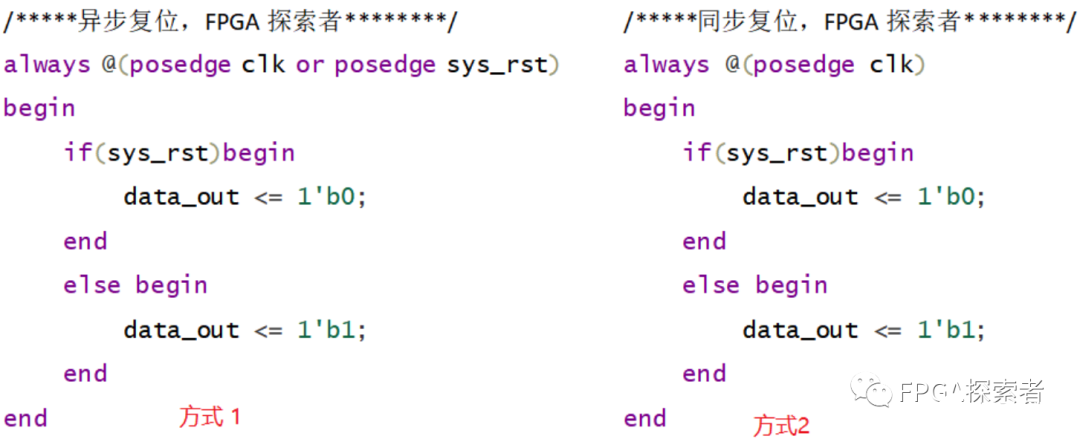

如下圖所示,選方式1還是方式2?

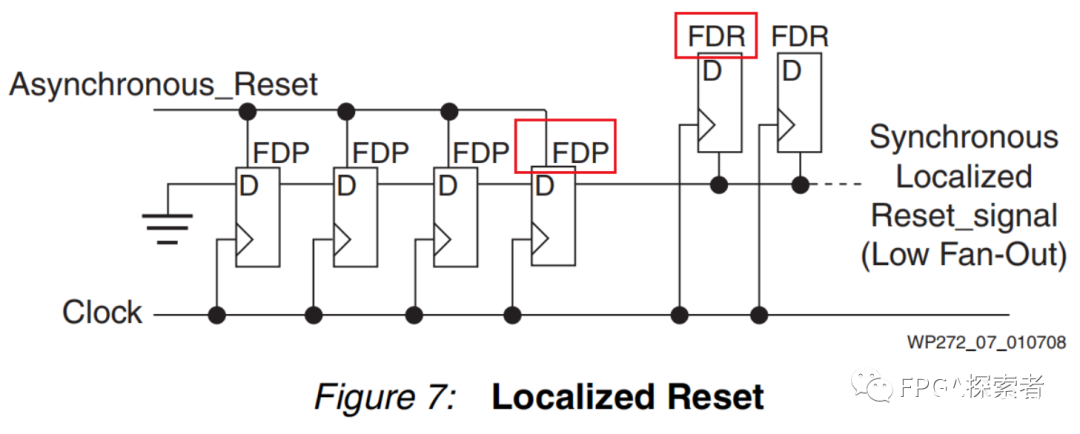

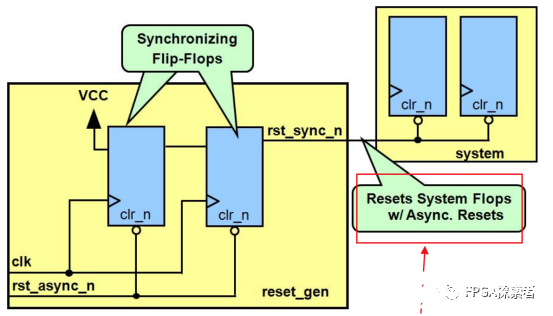

針對此問題查找了很多資料,網絡上多是將sys_rst繼續按照方式1異步復位使用,Xilinx復位白皮書wp272中提到的異步復位同步釋放 如圖所示:

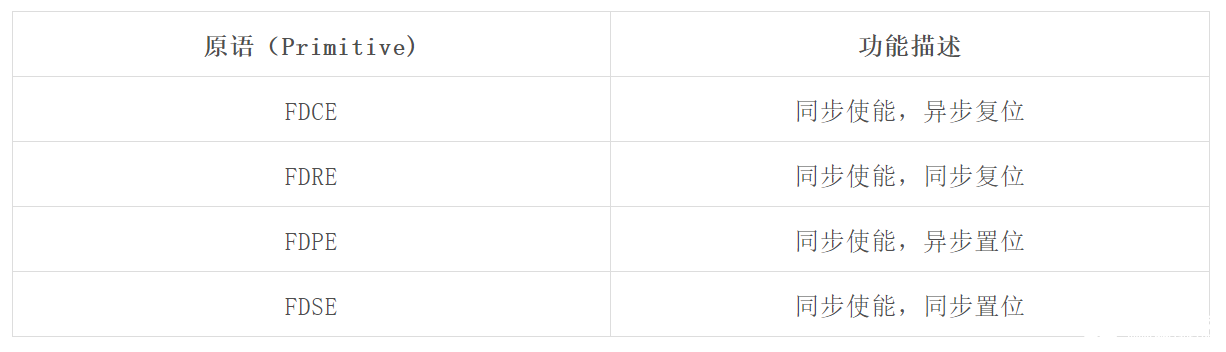

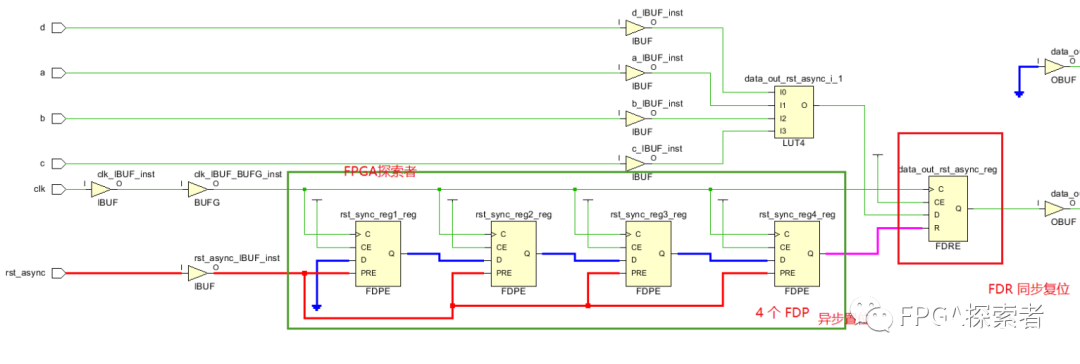

對于輸入的異步復位Asynchronous Reset,首先使用了4個觸發器來做同步(一般用2個即可,4個出現亞穩態的概率更小),觸發器類型為FDP(異步置位),同步化以后的復位信號去使用時綜合出的觸發器類型為FDR(同步復位),即在Xilinx中是將sys_rst按照方式2同步復位使用。

使用FDP異步置位的原因是因為Xilinx推薦高電平復位,當異步復位信號到來時,輸出復位電平“1”,即異步置位FDP,當復位消失后,D觸發器在每個時鐘邊沿輸出前一級觸發器的值,一定周期后,最后一級的FDP穩定輸出“0”。

使用Xilinx A7系列FPGA實現異步復位、同步釋放代碼,確定同步化后的復位使用情況。

二、Xilinx復位程序對比

1. 將同步化后的復位當作異步復位信號

/******FPGA探索者******/ always @(posedge clk or posedge rst_async) begin if(rst_async == 1’b1) begin rst_sync_reg1 《= 1‘b1; rst_sync_reg2 《= 1’b1; rst_sync_reg3 《= 1‘b1; rst_sync_reg4 《= 1’b1; end else begin rst_sync_reg1 《= 1‘b0; rst_sync_reg2 《= rst_sync_reg1; rst_sync_reg3 《= rst_sync_reg2; rst_sync_reg4 《= rst_sync_reg3; end end wire sys_rst; assign sys_rst = rst_sync_reg4; always @(posedge clk) begin if(sys_rst == 1’b1) begin data_out_rst_async 《= 1‘b0; end else begin data_out_rst_async 《= a & b & c & d; end end

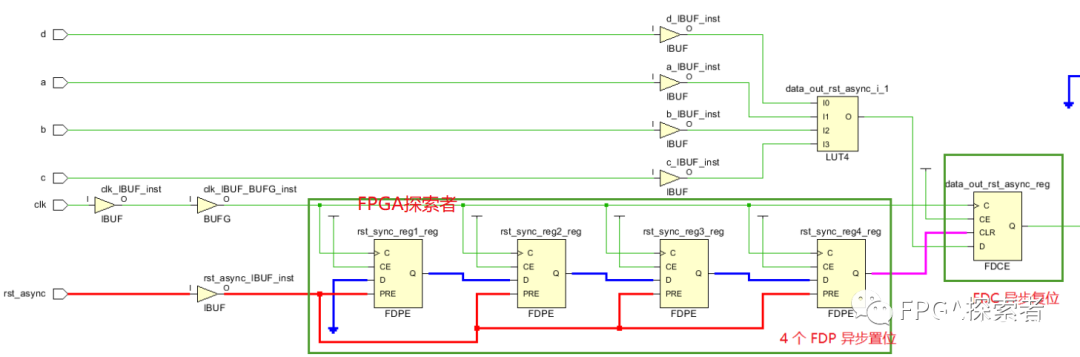

綜合并布局布線后的原理圖如圖所示,顯然,綜合后對sys_rst復位,將其作為異步復位綜合出FDCE同步使能異步復位(這里不考慮使能),和白皮書WP272給出的參考電路顯然不一致。

2. 將同步化后的復位當作同步復位信號

/******FPGA探索者******/ always @(posedge clk or posedge rst_async) begin if(rst_async == 1’b1) begin rst_sync_reg1 《 = 1‘b1; rst_sync_reg2 《 = 1’b1; rst_sync_reg3 《 = 1‘b1; rst_sync_reg4 《 = 1’b1; end else begin rst_sync_reg1 《 = 1‘b0; rst_sync_reg2 《 = rst_sync_reg1; rst_sync_reg3 《 = rst_sync_reg2; rst_sync_reg4 《 = rst_sync_reg3; end end wire sys_rst; assign sys_rst = rst_sync_reg4; always @(posedge clk) begin if(sys_rst == 1’b1) begin data_out_rst_async 《 = 1‘b0; end else begin data_out_rst_async 《 = a & b & c & d; end end

綜合并布局布線后的原理圖如圖所示,顯然,綜合后對sys_rst復位,將其作為同步復位綜合出FDRE同步使能異步復位(這里不考慮使能),和白皮書WP272給出的參考電路一致。

異步復位相比較同步復位,在Xilinx的FPGA中資源是一致的,異步復位的優勢在于復位信號一來就能檢測到,不需要保持至少一個時鐘周期才能在時鐘邊沿檢測到,通過仿真來驗證上述電路是否能實現異步復位一來就能檢測到。

三、仿真結果

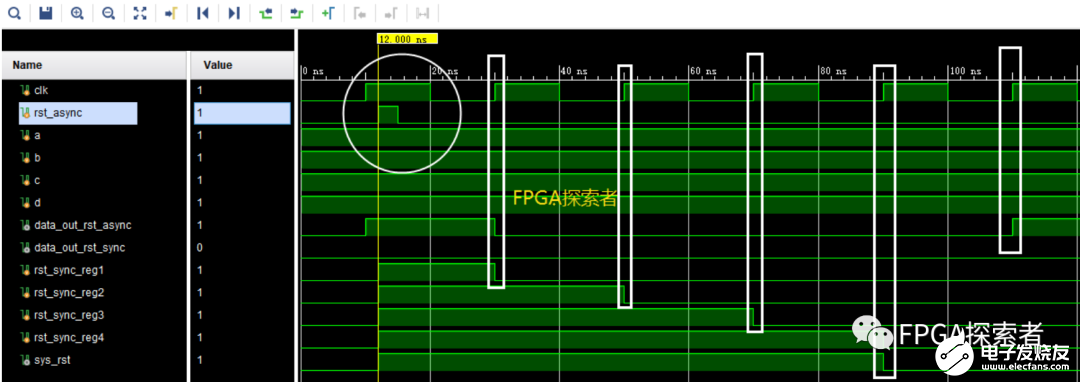

設置時鐘50MHz,時鐘周期20ns,給一個持續時間3ns的異步復位信號,且持續時間均不出現在時鐘上升沿檢測期間,可以看到:

(1)rst_async異步復位一旦給出,用于同步的4個寄存器rst_sync_reg1~4立刻輸出高電平“1”,在下一個時鐘上升沿檢測到同步復位并將輸出data_out_rst_async復位;

(2)異步復位信號釋放后,經過同步的sys_rst經過一定周期后在時鐘邊沿同步釋放;

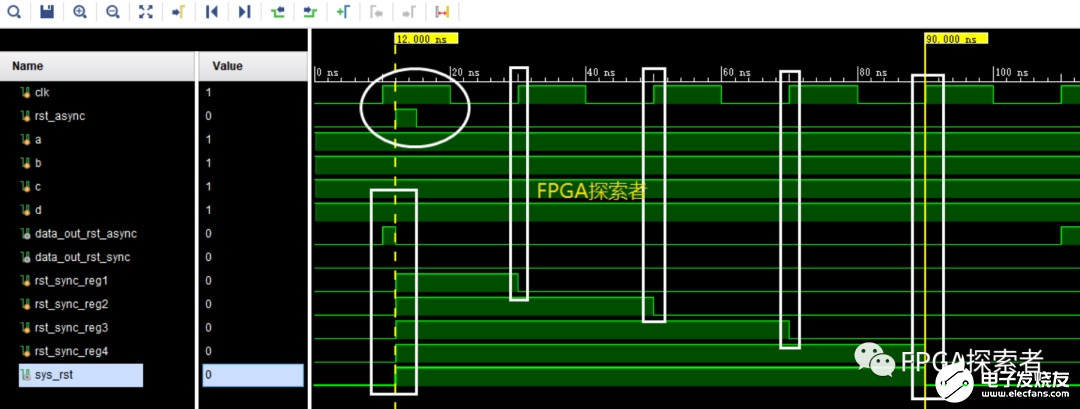

按照同樣的復位,將sys_rst看作異步復位,仿真結果如下,相比于上圖,區別在于異步復位信號rst_async一旦產生,輸出立刻復位,且同樣是同步釋放,好像這種處理才更符合異步復位、同步釋放。。。。。。

那么為什么Xilinx白皮書還是將sys_rst按照同步復位去做的呢?難道寫錯了?

綜合考慮可能有這樣的因素:

(1)當作同步復位的差別只在于復位時間會稍晚一些,要在時鐘的下一個邊沿檢測到,但是還是能夠識別到輸入的rst_async異步復位信號,所以從復位角度來說,都能夠后實現復位效果;

(2)根據Xilinx復位準則,我們知道同步復位相比異步復位有很多好處,具體參見:Xilinx FPGA 復位策略白皮書,既然兩者對后級復位沒有功能上的差別,那么優先選擇同步復位;

經過異步復位同步釋放處理后,相比于純粹的異步復位,降低了異步復位信號釋放導致亞穩態的可能性;相比同步復位,能夠識別到同步復位中檢測不到的復位信號(如上圖所示的rst_async在同步復位是檢測不到的);綜合兩者的優勢,異步復位同步釋放。

四、Altera復位

Altera還是把這個同步后的復位當作異步復位來用的,且推薦低電平復位。

從上面的分析來看,這里當作異步復位還是同步復位對于復位結果本身沒有太大的影響,區別在于Xilinx是推薦同步復位來節省資源(比如DSP48E或BRAM,異步復位比同步復位耗資源),而Altera的FPGA中帶異步復位的觸發器,想要同步復位需要消耗更多的資源。

編輯:lyn

-

FPGA

+關注

關注

1660文章

22412瀏覽量

636312 -

Xilinx

+關注

關注

73文章

2200瀏覽量

131137 -

同步復位

+關注

關注

0文章

27瀏覽量

10984 -

異步復位

+關注

關注

0文章

47瀏覽量

13684

發布評論請先 登錄

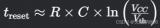

MAX709 電源監控復位芯片:設計與應用全解析

探索DS1811:經濟高效的電源監控復位芯片

MAX6467/MAX6468:微處理器監控復位電路新選擇

MAX6443–MAX6452:具備長手動復位設置周期的微處理器復位電路

CW32在不同復位方式對應的復位范圍

什么是內核LOCKUP故障復位?

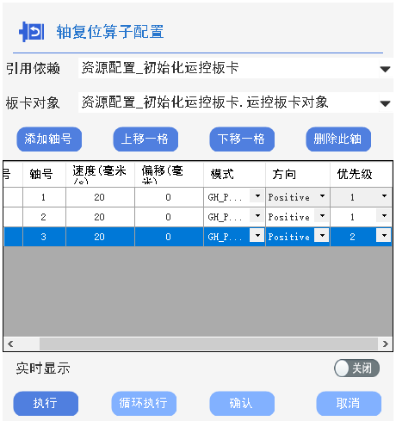

GraniStudio:軸復位例程

GraniStudio零代碼平臺軸復位算子支持多少個軸同時復位,有哪些回零模式?

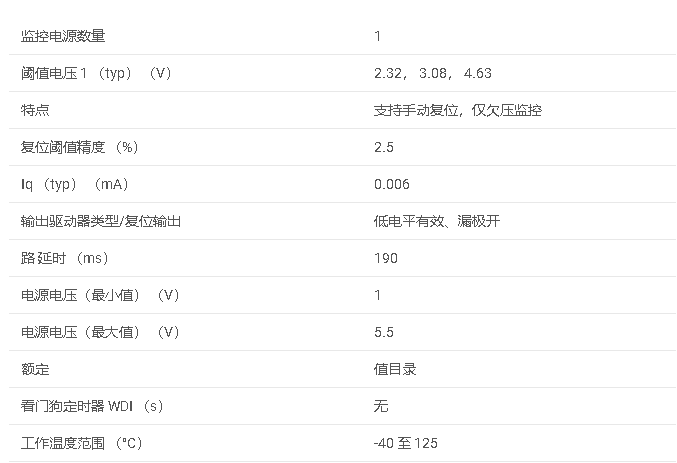

LM3724系列 低功率電壓監控和復位IC,帶手動復位功能數據手冊

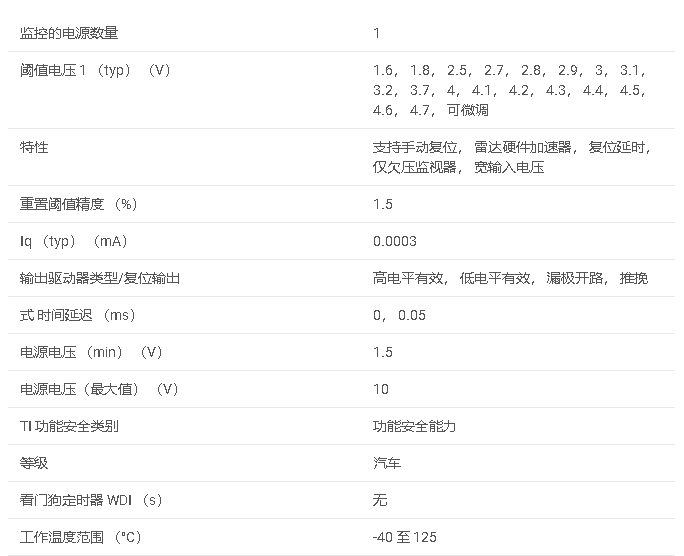

TPS3840-Q1 具有手動復位和可編程復位時間延遲的汽車高輸入電壓監控器數據手冊

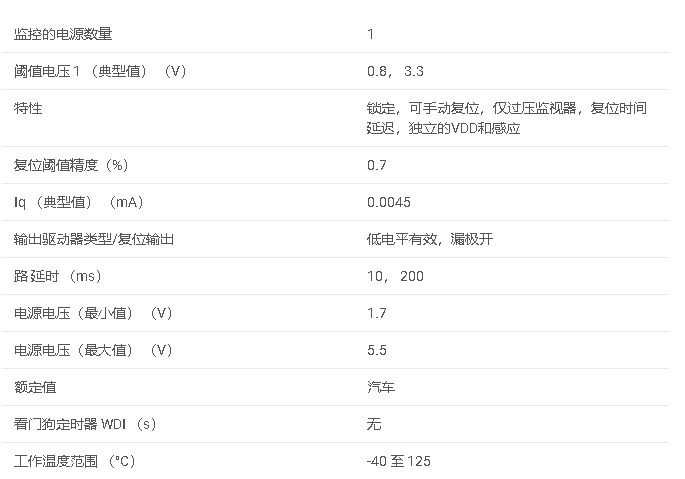

TPS3870-Q1 具有延時和手動復位功能的汽車級高精度過壓復位 IC數據手冊

TLV840系列 具有可調復位時間延遲和手動復位功能的低壓監控器數據手冊

詳細講解同步后的復位是同步復位還是異步復位?

詳細講解同步后的復位是同步復位還是異步復位?

評論