隨著現代電子系統的不斷發展,時鐘管理成為影響系統性能、穩定性和電磁兼容性(EMI)的關鍵因素之一。在FPGA設計中,PLL因其高精度、靈活性和可編程性而得到廣泛應用,本文將深入探討PLL技術在FPGA中的動態調頻與展頻功能應用。

2025-06-20 11:51:12 2360

2360

賽靈思在其FPGA中提供了豐富的時鐘資源,大多數設計人員在他們的FPGA設計中或多或少都會用到。不過對FPGA設計新手來說,什么時候用DCM、PLL、PMCD和MMCM四大類型中的哪一種,讓他們頗為困惑。本文為您解惑......

2013-07-23 09:25:53 20763

20763

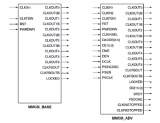

把握DCM、PLL、PMCD和MMCM知識是穩健可靠的時鐘設計策略的基礎。 賽靈思在其FPGA中提供了豐富的時鐘資源,大多數設計人員在他們的FPGA設計中或多或少都會用到。不過對FPGA設計新手來說

2021-02-13 17:02:00 3074

3074

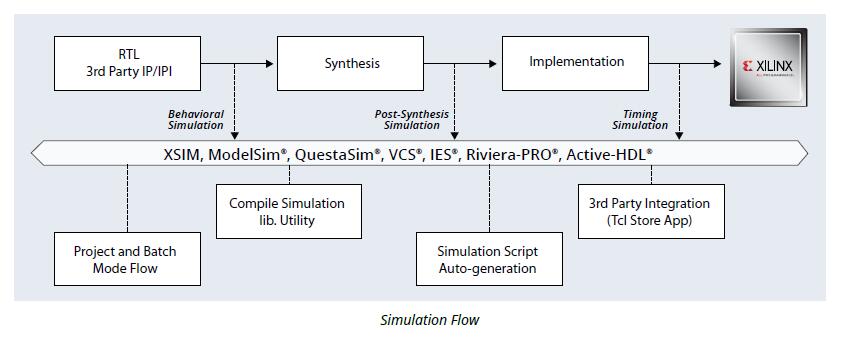

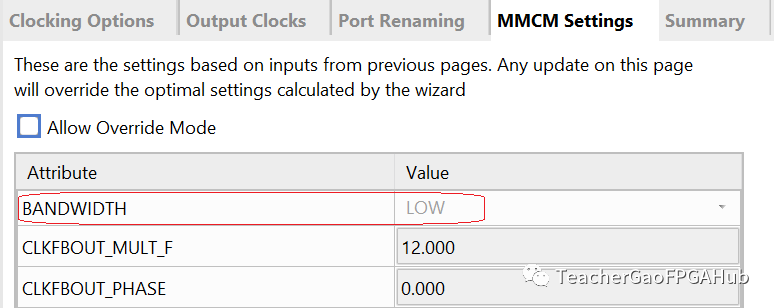

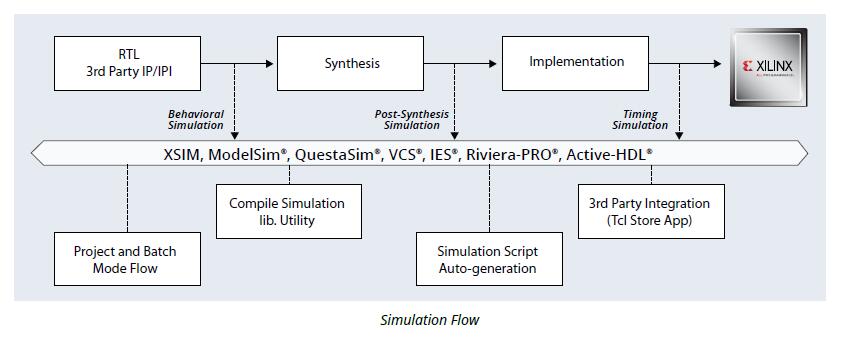

鎖相環基本上是每一個fpga工程必不可少的模塊,之前文檔xilinx 7 系列FPGA時鐘資源對xilinx fpga的底層時鐘資源做過說明,但是對于fpga的應用來說,使用Clocking Wizard IP時十分方便的。

2023-06-12 17:42:03 8964

8964

。Xilinx FPGA7系列分為全局時鐘(Global clock)和局部時鐘(Regional clock)資源。目前,大型設計一般推薦使用同步時序電路。同步時序電路基于時鐘觸發沿設計,對時鐘的周期

2023-07-24 11:07:04 1443

1443

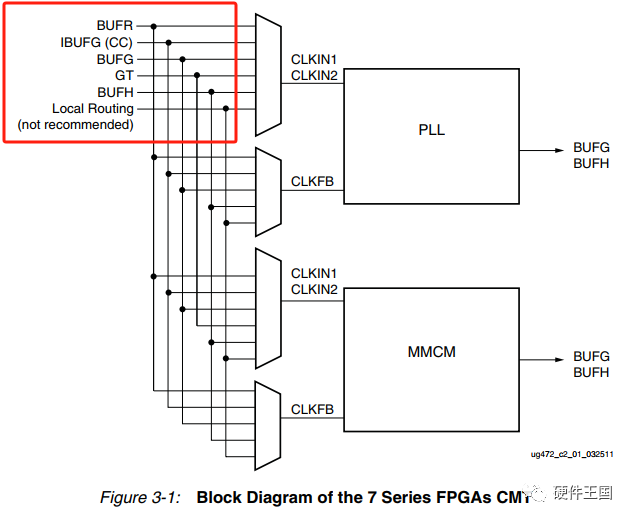

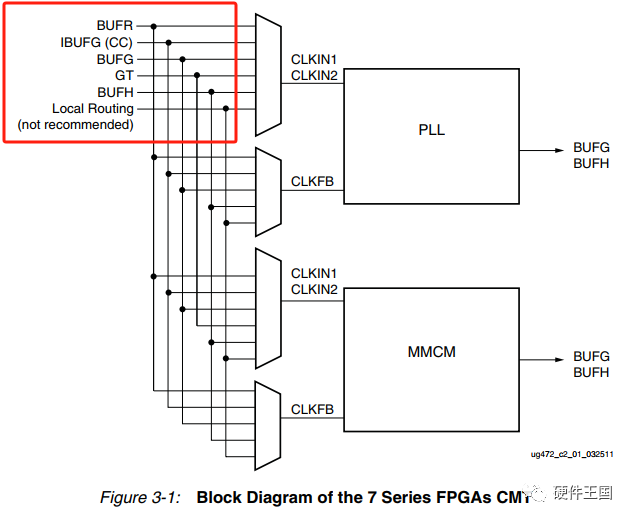

通過上一篇文章“時鐘管理技術”,我們了解Xilinx 7系列FPGA主要有全局時鐘、區域時鐘、時鐘管理塊(CMT)。 通過以上時鐘資源的結合,Xilinx 7系列FPGA可實現高性能和可靠的時鐘分配

2023-08-31 10:44:31 4432

4432

本文主要介紹Xilinx FPGA的GTx的參考時鐘。下面就從參考時鐘的模式、參考時鐘的選擇等方面進行介紹。

2023-09-15 09:14:26 5117

5117

Xilinx Block Memory Generator(BMG)是一個先進的內存構造器,它使用Xilinx fpga中的嵌入式塊RAM資源生成面積和 性能優化的內存。

2023-11-14 17:49:43 4754

4754

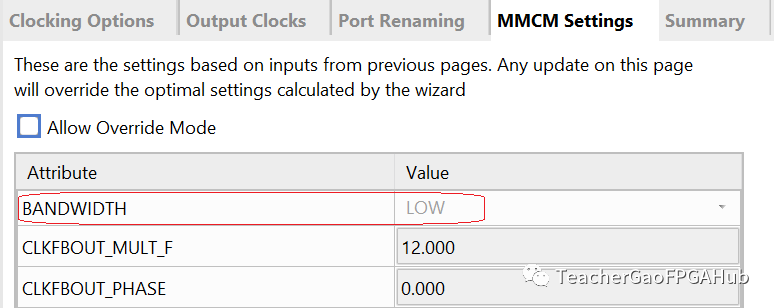

7系列FPGA包含最多24個CMT塊,CMT具體的分布和與其他時鐘資源的關系請參考本合集(FPGA應用開發)的上一篇文章。本文主要介紹CMT內部MMCM和PLL的區別以及在實際開發中怎么使用CMT,怎么實現跨時鐘區域,第一次讀者最好先閱讀上一篇文章——解剖時鐘結構篇。

2023-11-17 17:08:11 11730

11730

UltraScale/UltraScale+芯片開始支持BUFG_*、PLL和MMCM出現在動態區,在7系列FPGA中這些時鐘資源只能在靜態區。

2023-12-21 09:12:13 1780

1780

生成時鐘包括自動生成時鐘(又稱為自動衍生時鐘)和用戶生成時鐘。自動生成時鐘通常由PLL或MMCM生成,也可以由具有分頻功能的時鐘緩沖器生成如7系列FPGA中的BUFR、UltraScale系列

2024-01-11 09:50:09 3808

3808

_cfg_clk, pll_cfg_clk_i是一個輸入時鐘,pll_cfg_clk是動態配置的輸出時鐘, 通過另一個PLL產生一個pll_CFG_CLK_i 在生成動態配置IP之前要先配置PLL的hex step1:把PLL配置成50M (2)添加配置參數。點擊 Reco

2025-07-14 18:14:01 3113

3113

不多說,上貨。IP CORE 之 PLL- ISE 操作工具本篇實現基于叁芯智能科技的SANXIN -B02 FPGA開發板,如有入手開發板,可以登錄官方淘寶店購買,還有配套的學習視頻。Xilinx

2023-04-06 16:04:21

從在MMCME2_ADV原語和thanx到DRP寄存器上鏈接的MMCM_DRP verilog組件(XAPP888),我能夠動態重新配置輸出時鐘Frequency.ClkRegX位圖DRP寄存器允許

2020-06-15 08:52:05

MMCM是否也適用于40 Mhz或其他輸入時鐘?如果不工作,如何配置動態輸入時鐘MMCM?感謝您的幫助!以上來自于谷歌翻譯以下為原文Hi, I have a question about

2019-03-14 17:04:56

嗨,我有一個本地24Mhz clk饋入FPGA MRCC PIN,然后實例MMCM做clk合成2時鐘輸出。我將輸出驅動設置為mmcm而沒有緩沖區(因為我不想要bufg級聯),并將clkfb_out

2020-08-14 10:03:27

你好,我已將DDS芯片的輸出連接到我的Artix-7 FPGA引腳,用作頻率為F0的時鐘。我也限制了這個時鐘(按照F0),并在FPGA中使用輸入緩沖器。然后將該時鐘連接到MMCM ip內核的輸入,該

2019-04-23 08:53:32

Xilinx FPGA入門連載24:PLL實例之基本配置 1 工程移植可以復制上一個實例sp6ex7的整個工程文件夾,更名為sp6ex8。然后在ISE中打開這個新的工程。 2 新建IP核文件

2019-01-21 21:33:40

`Xilinx FPGA入門連載17:PWM蜂鳴器驅動之復位與FPGA重配置功能特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm1 復位

2015-10-26 12:05:15

`Xilinx FPGA入門連載23:PLL實例之功能簡介特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 PLL概述PLL

2015-11-10 08:44:06

`Xilinx FPGA入門連載24:PLL實例之基本配置特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 工程移植可以復制上一個實例

2015-11-16 12:09:56

`Xilinx FPGA入門連載40:SRAM讀寫測試之設計概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 功能簡介如圖所示,本

2015-12-18 12:57:01

Xilinx FPGA配置clocking時鐘動態相位輸出

2019-08-05 11:35:39

Xilinx FPGA SF-SP6入門指南 -- PWM蜂鳴器驅動之FPGA配置芯片固化Lesson19 特權Xilinx FPGA SF-SP6入門指南 -- PWM蜂鳴器驅動之復位與FPGA重配

2015-07-22 11:49:20

今天給大俠帶來Xilinx FPGA編程技巧之常用時序約束詳解,話不多說,上貨。

基本的約束方法為了保證成功的設計,所有路徑的時序要求必須能夠讓執行工具獲取。最普遍的三種路徑以及異常路徑為

2024-04-12 17:39:04

今天給大俠帶來Xilinx FPGA編程技巧之常用時序約束詳解,話不多說,上貨。

基本的約束方法

為了保證成功的設計,所有路徑的時序要求必須能夠讓執行工具獲取。最普遍的三種路徑以及異常路徑為

2024-05-06 15:51:23

Xilinx PlanAhead工具資料說可以用來部分動態重配置,我現在想對芯片的每一幀中每一位進行逐位翻轉的動態重配置,使用PlanAhead能夠實現么?應該怎么理解Planahead的部分重配置,如何應用?希望知道的朋友告訴下,對這個有點迷茫。

2015-06-01 10:11:33

《FPGACPLD設計工具──Xilinx+ISE使用詳解》

2018-01-12 15:04:43

`Xilinx系列FPGA芯片IP核詳解(完整高清書簽版)`

2017-06-06 13:15:16

', - 總是選擇主輸入時鐘CLKINSEL =>'1', - 動態重配置端口DADDR =>(其他=>'0'),DCLK => '0',DEN =>'0',DI

2020-07-29 10:08:32

,以便為Microblaze實現不同的periferal。我已經讀過Spartan3 FPGA支持部分重配置,但我不知道它是否支持動態重配置,而Microblaze仍在使用中。有幫助嗎?提前致謝缺口

2019-05-14 06:28:56

,MMCM,PLL生成的,那么顯然ISE知道這些時鐘之間的頻率、相位關系,所以也不需要我們指定。如果這些不同的時鐘是通過不同的引腳輸入的,ISE不知道其相位關系,所以指定其中一個為主時鐘,需要指定其間的相位

2019-07-09 09:14:48

Altera可重配置PLL使用手冊在實際應用中,FPGA的工作時鐘頻率可能在幾個時間段內變動,對于與之相關的鎖相環(PLL),若PLL的輸入時鐘在初始設定的時鐘頻率的基礎上變化不太大時,PLL一般

2009-12-22 11:27:13

Cyclone? IV GX 收發器支持對收發器的不同部分進行動態重配置,而無需對器件的任何部分斷電。本章節提供并講解了用于動態重配置各種模式的實例。您可以使用 ALTGX_RECONFIG

2017-11-14 10:53:11

本章節介紹了 Cyclone? IV 器件系列中具有高級特性的層次時鐘網絡與鎖相環 (PLL),包括了實時重配置 PLL 計數器時鐘頻率和相移功能的詳盡說明,這些功能使您能夠掃描 PLL 輸出頻率,以及動態調整輸出時鐘相移。

2017-11-14 10:09:42

喜我正在使用xilinx V5 XC5VSX50T板,我不得不動態更改DCM頻率。我在網上查了一下,文檔說我們可以使用drp模塊(動態重配置端口)來改變DCM的乘法/除法值。我想知道這個DRP模塊

2019-02-26 11:13:07

EG_PHY_PLL 是 FPGA 內部的時鐘鎖相環硬核 IP 模塊,Eagle 系列 FPGA 內嵌 4 個多功能鎖相環(PLL0~PLL3),分布在器件四角,可實現高性能時鐘管理功能。每個

2022-10-27 07:45:54

有沒有大神幫忙,板子時鐘50MHz,IP核產生的MMCM時鐘,102.3MHz,102.3是所有子模塊的時鐘,實在不會綁!求幫助

2018-04-11 23:32:47

嗨,我使用Virtex6 LX75T和4個高速DAC設計了一塊電路板。我將每個DAC連接到一個FPGA io Bank,我使用MRCC引腳作為MMCM(差分)的時鐘輸入,4個引腳用于片外反饋。不幸

2020-06-16 10:06:19

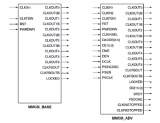

原子公眾號,獲取最新資料第十一章IP核之MMCM/PLL實驗PLL的英文全稱是Phase Locked Loop,即鎖相環,是一種反饋控制電路。PLL對時鐘網絡進行系統級的時鐘管理和偏移控制,具有時鐘

2020-09-22 16:48:59

module ip_pll( inputsys_clk,//系統時鐘 inputsys_rst_n,//系統復位,低電平有效 //輸出時鐘 output clk_100m ,//100Mhz時鐘頻率

2023-02-09 23:21:59

的硬件設計。默認125Mhz。

INIT_CLK

初始化階段的時鐘 ,在上電初始化階段,可以使用該時鐘來驅動一些邏輯。默認值:50Mhz。

DRP_CLK

DRP時鐘,動態重配置,一般沒用(通常一個

2024-11-14 21:29:37

的時鐘。首先建立一個文件在ip核目錄里搜索ALTPLL然后在工程文件的par文件里建立一個文件夾ipcore將剛剛的變化保存到文件里命名為pll_clk然后點擊ok就會出現配置過程界面FPGA系統晶振為

2020-01-13 18:13:48

大家好,我是fpga的新手,我想對使用mmcm_adv IP的簡單動態相移模塊進行簡單的行為模擬。我使用核心發生器將ip核心添加到項目中,以動態相移100 MHz輸入時鐘,psclock頻率為50

2020-03-12 09:24:34

你好,我需要動態頻率合成器。我可以使用MMCM的drp端口動態調整mmcm的頻率輸出。有什么限制?故障怎么樣?InXAPP872中使用了iodelay元素。使用這種方法是否可以將合成時鐘路由到結構

2020-07-31 10:19:37

`例說FPGA連載31:PLL例化配置與LED之PLL的IP核配置特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc 本實例使用了一個

2016-09-12 17:31:43

參考了官網和各路大神寫的一些關于PLL動態重配置的資料,雖然有收獲但是還是感覺大神們寫的太高端,不夠詳細,對于我這種學渣看起來還是迷迷糊糊。所以整理了一下自己的經驗,把整個過程記錄了下來。沒有很多語言全部是截圖大家湊合看吧。附有源代碼和Word文檔。

2017-10-12 12:32:44

不是FPGA輸出引腳。更具體地說,我正在使用一些Xilinx示例代碼來執行ISERDES。此代碼需要來自FPGA輸入引腳的差分時鐘。但是,我沒有正確的頻率進入引腳,必須使用PLL來產生正確的頻率。因此

2020-08-21 08:24:40

系列FPGA中,MMCM和PLL之間是否有專用的CMT路由? 我做了兩個實驗。 在第一個實驗中,我使用MMCM來驅動PLL,如下圖所示。此方法有效,但MMCM和PLL不位于相同的時鐘區域。 在第二個

2020-08-21 09:16:28

嗨,我想重新配置。 MMCM2通過動態重配置端口&更改Spread Spectrumparameter。“Xilinx PG065 LogiCORE IP時鐘向導4.2,產品指南”顯示了如

2020-07-20 16:14:55

你好,我正在使用MMCM將10MHz時鐘乘以MMCM_ADV乘以100MHz。Coregen向導預測600ps峰峰值抖動,我進行了相位噪聲測量,從MMCM輸出140ps rms相位噪聲,大部分

2020-06-18 13:57:55

把握DCM、PLL、PMCD和MMCM知識是穩健可靠的時鐘設計策略的基礎。賽靈思在其FPGA中提供了豐富的時鐘資源,大多數設計人員在他們的FPGA設計中或多或少都會用到。不過對FPGA設計新手來說,什么時候用DCM、PLL、PMCD和MMCM四大類型中的哪一種,讓他們頗為困惑。

2019-09-18 08:26:21

大家好!我正在使用Spartan6 FPGA為高速DAC提供數據。必要的高速I / O時鐘由PLL實例完成。在我的申請中,我有兩種不同的情況:case1:我需要從80MHz參考(M = 12)產生

2019-07-31 10:59:14

型號XC7VX690T-2FFG1761CPart編號XC7A200T-2FBG676C我們計劃使用MMCM在FPGA內部生成時鐘。這將在PCB中布線MGT時鐘引腳,以饋送MGT參考時鐘GTP

2020-03-18 09:53:15

://www.openedv.com/thread-13912-1-1.html第十三章 IP核之PLL實驗PLL的英文全稱是Phase Locked Loop,即鎖相環,是一種反饋控制電路。PLL對時鐘網絡進行系統級的時鐘管理

2020-07-30 14:58:52

系列器件的 PLL 支持 APB 動態重配功能,實現 HDMI 像素時鐘頻率的調整可通過 APB 接口動態配置 PLL 輸出時鐘頻率(時鐘相位和占空比不做調整)。而 Logos 器件是沒有這個功能

2024-08-15 17:41:46

請問,想通過FPGA的PLL倍頻產生個500MHz的時鐘來使用,以此時鐘來做定時精密延遲,不知道PLL倍頻倍數有什么要求,比如好像有的器件支持不到500MHz,有沒有可推薦的器件呢

補充內容 (2017-1-4 09:26):

或者有大神用過類似能到500MHz的FPGA推薦么

2017-01-03 17:04:23

Virtex-5 - 通過DRP動態重新配置DCM的地址和值是什么?我有PLL的電子表格,但沒有DCM的電子表格。

2020-06-16 16:25:11

我在Artix7上使用帶DRP的PLL。用于時鐘合成的PLL重配置工作正常。RST用于重新配置。因此,簡單的RESETN斷言不會初始化PLL。我需要一種初始化PLL的方法來恢復具有初始值的所有寄存器。請教我怎么做。

2020-08-26 15:13:24

嗨, 我想使用MMCM時鐘生成模塊來實時和動態地改變Artix FPGA中的相移。但我見過Xilinx UG472& PG065用戶指南和時鐘設置手冊。我使用PSCLK,PSEN

2020-08-11 10:33:29

Xilinx系列FPGA芯片IP核詳解 ,altera系列FPGA芯片IP核詳解 , 相關資料 謝謝!!萬分感謝!!!!!

2015-06-03 15:03:34

為了應用FPGA中內嵌的數字時鐘管理(DCM)模塊建立可靠的系統時鐘。首先對DCM的工作原理進行分析,然后根據DCM的工作原理給出了一種DCM動態重配置的設計方法。DCM動態重配置設計是利

2010-07-28 17:03:52 28

28 本文檔主要是以Altera公司的Stratix II系列的FPGA器件為例,介紹了其內嵌的增強型可重配置PLL在不同的輸入時鐘頻率之間的動態適應,其目的是通過提供PLL的重配置功能,使得不需要對

2010-11-02 15:17:24 27

27 FPGA的全局動態可重配置技術主要是指對運行中的FPGA器件的全部邏輯資源實現在系統的功能變換,從而實現硬件的時分復用。提出了一種基于System ACE的全局動態可重配置設計方法,

2011-01-04 17:06:01 54

54 WP374 Xilinx FPGA的部分重配置

2012-03-07 14:34:39 34

34 本文介紹了XiLinx FPGA中DCM的結構和相關特性,提出了一種基于XiLinx FPGA的DCM動態重配置的原理方法,并給出了一個具體的實現系統。系統僅通過外部和......

2012-05-25 13:42:50 39

39 Xilinx FPGA工程例子源碼:Xilinx TCP_IP協議實現

2016-06-07 14:54:57 33

33 普通IO可以通過BUFG再連到PLL的時鐘輸入上,但要修改PLL的設置 input clk的選項中要選擇"No Buffer";

2017-02-09 12:54:11 7661

7661

PLL),再到Virtex-6基于PLL的新型混合模式時鐘管理器MMCM(Mixed-Mode Clock Manager),實現了最低的抖動和抖動濾波,為高性能的FPGA設計提供更高性能的時鐘管理功能。

2017-02-11 09:14:01 1604

1604

Suite HLx 2017.1版中廣泛納入部分重配置技術,為有線和無線網絡、測試測量、航空航天與軍用、汽車以及數據中心等豐富應用,提供動態的現場升級優勢和更高的系統集成度。

2017-04-27 18:38:08 3338

3338

NI FlexRIO是NI公司推出的FPGA應用的模塊化產品,基于NI LabVIEW可重配置I/ O(RIO)架構的NI FlexRIO在一個平臺中集成了高性能模塊化I / O、功能強大的Xilinx FPGA以及基于PC的技術,是板載處理和實時分析應用系統的理想之選。

2018-07-05 09:11:00 3770

3770 FPGA 動態局部重配置技術是近幾年才發展起來的一項新技術。這項技術可以使 FPGA運行時,通過 JTAG或 SelectMAP(ICAP)動態重配置部分區域,而不影響非重配置區域的正常工作。 在

2017-10-18 16:38:59 4

4 本頁包含通過LabVIEW FPGA模塊可用的Xilinx CORE生成器IP的列表。LabVIEW通過Xilinx IP節點實現該IP。 下列IP名稱和說明來自于Xilinx數據表。LabVIEW

2017-11-18 05:55:51 5498

5498 在 Xilinx 系列 FPGA 產品中,全局時鐘網絡是一種全局布線資源,它可以保證時鐘信號到達各個目標邏輯單元的時延基本相同。其時鐘分配樹結構如圖1所示。 圖1.Xilinx FPGA全局時鐘分配

2017-11-22 07:09:36 12586

12586

的應用。在主流的FPGA中,絕大多數都采用了SRAM來存放配置數據,稱為SRAM FPGA。這種FPGA的突出優點是可以進行多次配置。通過給FPGA加載不同的配置數據,即可令其實現不同的邏輯功能.FPGA這種可重配置的能力將給數字系統的設計帶來很大的方便。

2018-07-18 12:50:00 3395

3395

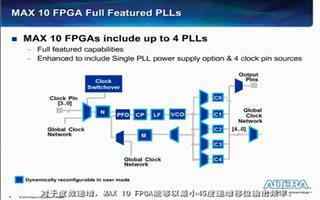

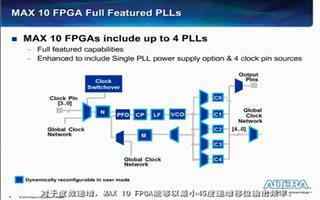

MAX 10 FPGA PLL和時鐘培訓,此次培訓涉及到器件系列的時鐘特性和選項。有20個全局時鐘網絡,全局CLK輸入引腳數量也可以加倍,用作通用IO引腳。并且采用動態用戶控制進行各種選擇和電源控制,構建魯棒的時鐘網絡源。它所有4個PLL都是全功能的。

2018-06-20 08:00:00 3327

3327

先用FPGA的外部輸入時鐘clk將FPGA的輸入復位信號rst_n做異步復位、同步釋放處理,然后這個復位信號輸入PLL,同時將clk也輸入PLL。設計的初衷是在PLL輸出有效時鐘之前,系統的其他部分都保持復位狀態。

2020-03-29 17:19:00 3320

3320

的時鐘管理資源會有一些差異,主要功能是對時鐘的頻率、占空比、相位等功能的管理。例如:PLL,DLL,DCM,MMCM等。

2020-12-09 14:49:03 21

21 MMCM的一個重要功能就是過濾抖動,更準確地說是改善抖動。使用MMCM時,建議直接調用IP Core Clocking Wizard,而不要使用原語。 ? 如果MMCM僅僅用作改善抖動,那么要求輸出

2021-02-02 16:39:17 3807

3807

?xilinx 的 FPGA 時鐘結構,7 系列 FPGA 的時鐘結構和前面幾個系列的時鐘結構有了很大的區別,7系列的時鐘結構如下圖所示。

2022-07-03 17:13:48 4699

4699 電子發燒友網站提供《ELF2 FPGA PLL動態配置.pdf》資料免費下載

2022-09-26 15:13:06 1

1 上文XILINX FPGA IP之FIFO對XILINX FIFO Generator IP的特性和內部處理流程進行了簡要的說明,本文通過實際例子對該IP的使用進行進一步的說明。本例子例化一個讀數

2023-09-07 18:31:35 3352

3352

把握DCM、PLL、PMCD和MMCM知識是穩健可靠的時鐘設計策略的基礎。賽靈思在其FPGA中提供了豐富的時鐘資源,大多數設計人員在他們的FPGA設計中或多或少都會用到。

2023-10-30 11:47:55 2892

2892

FPGA 中包含一些全局時鐘資源。以AMD公司近年的主流FPGA為例,這些時鐘資源由CMT(時鐘管理器)產生,包括DCM、PLL和MMCM等。

2024-04-25 12:58:30 3304

3304

在使用FPGA的時候,有些IP核是需要申請后才能使用的,本文介紹如何申請xilinx IP核的license。

2024-10-25 16:48:32 2275

2275

電子發燒友App

電子發燒友App

評論