TJ375已經支持PLL的動態配置。打開PLL在Advance Settings中的Dynamic Reconfiguration中勾選Enable就可以了。最大可以支持85組配置參數。動態配置框圖如下:

(1)在interface中打開動態配置功能

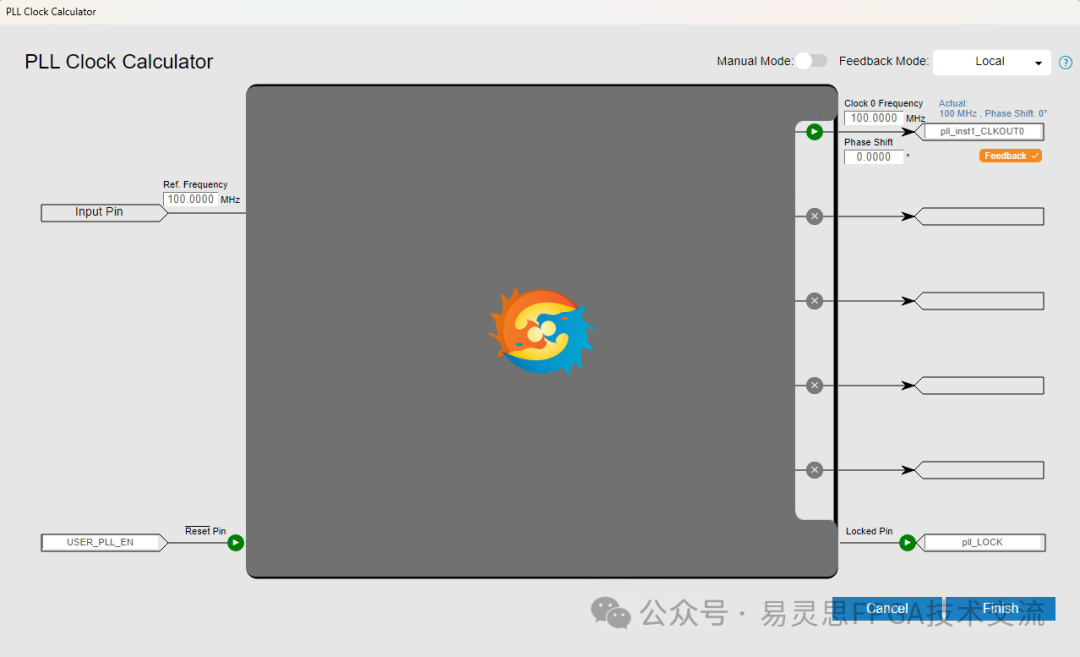

使用PLL動態配置功能需要打開PLL的reset和lock信號,

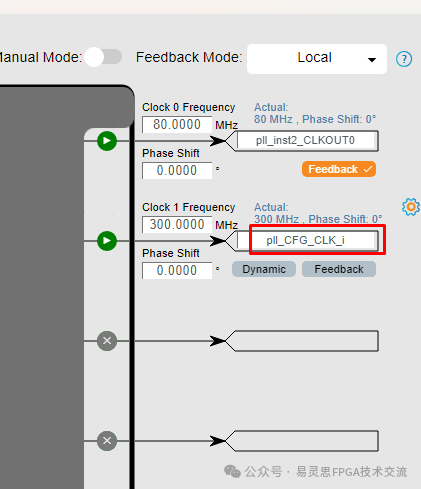

需要兩個時鐘,pll_cfg_clk_i 和 pll_cfg_clk, pll_cfg_clk_i是一個輸入時鐘,pll_cfg_clk是動態配置的輸出時鐘,

通過另一個PLL產生一個pll_CFG_CLK_i

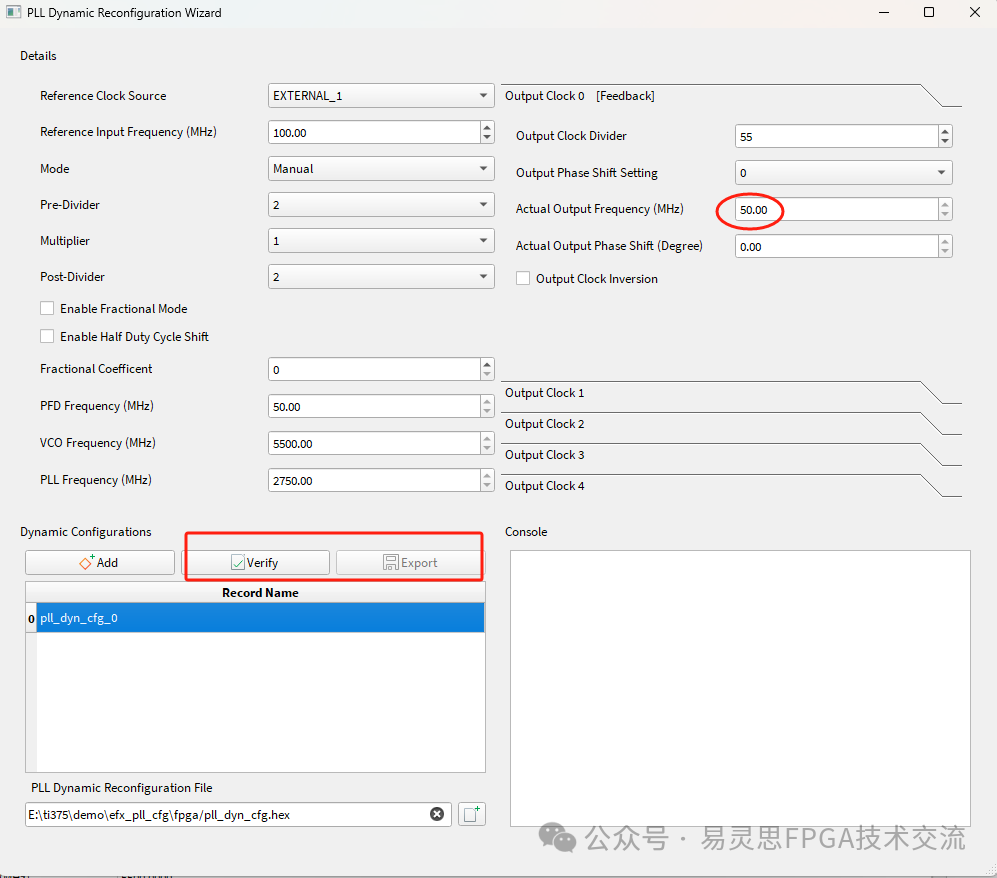

在生成動態配置IP之前要先配置PLL的hex

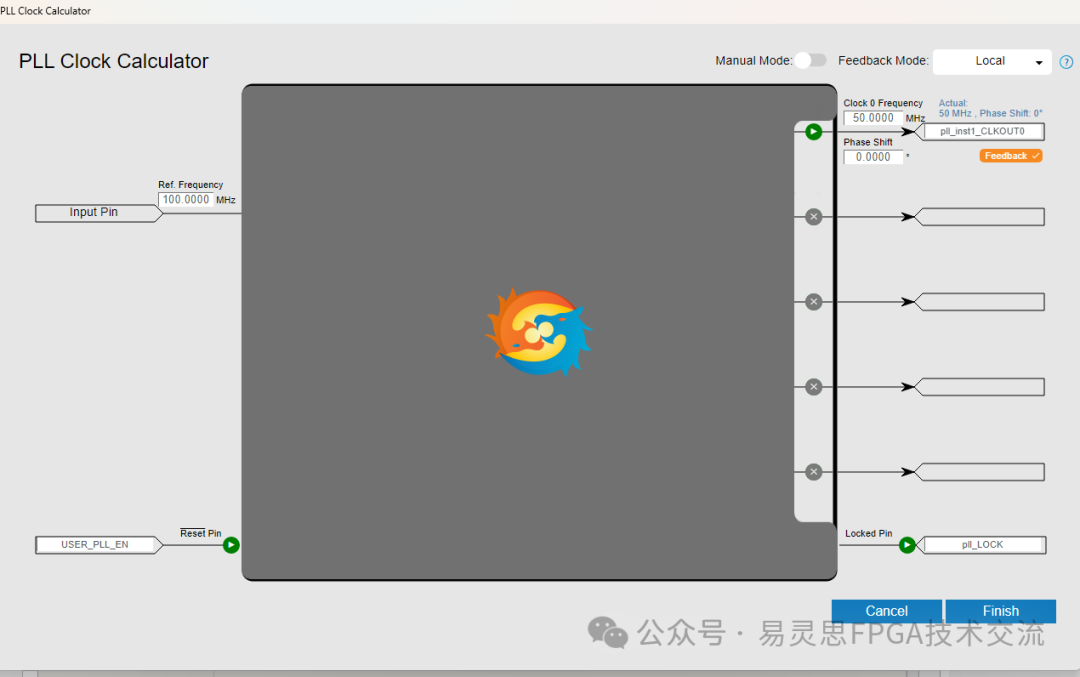

step1:把PLL配置成50M

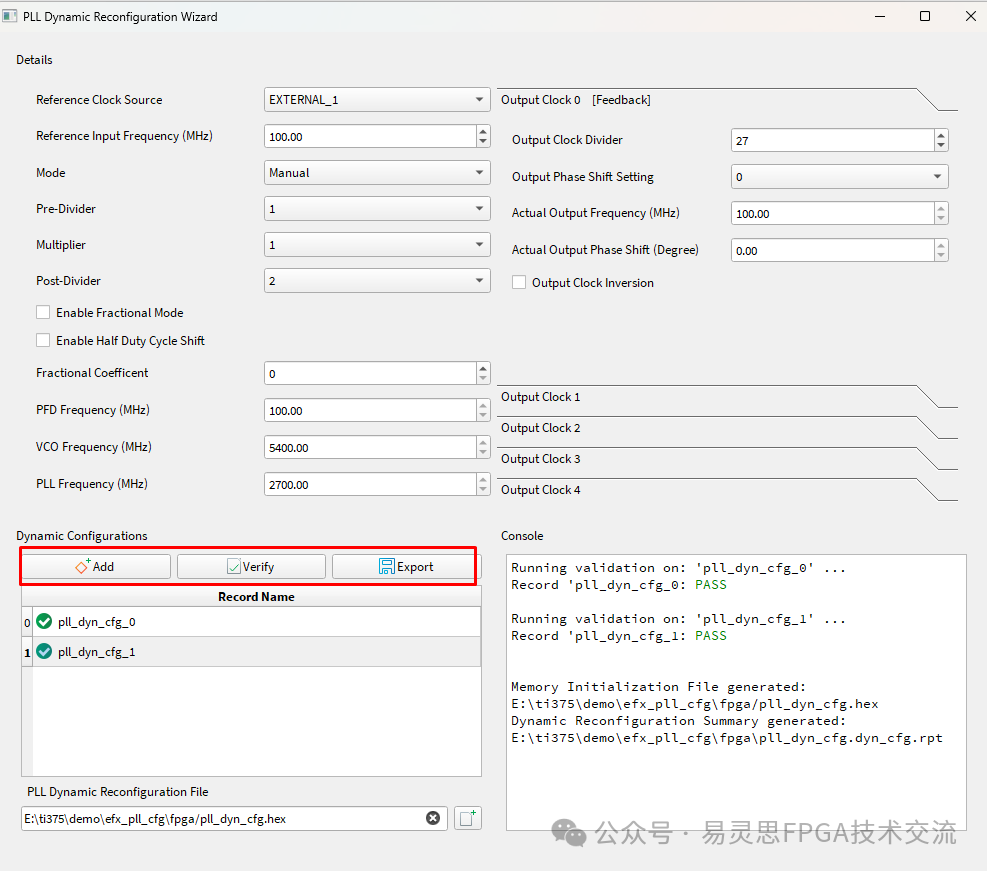

(2)添加配置參數。點擊 Reconfiguration Wizard就可以看到該組參數的配置,點擊verify確認參數是否正常;再點擊Export生成相應的參數到hex文件;

把PLL的輸出修改成100M輸出。

再次點擊 Reconfiguration Wizard就可以看到該組參數的配置,點擊verify確認參數是否正常;再點擊Export生成相應的參數到hex文件;

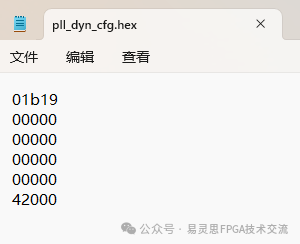

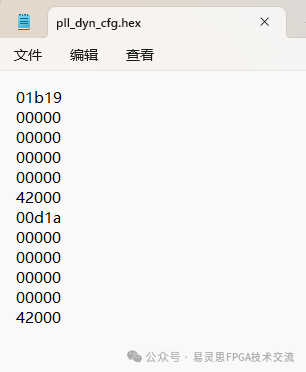

從生成的hex文件可以看到數據有所增加,說明有兩個組配置參數。

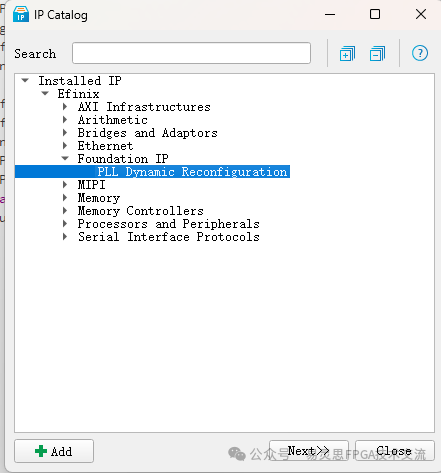

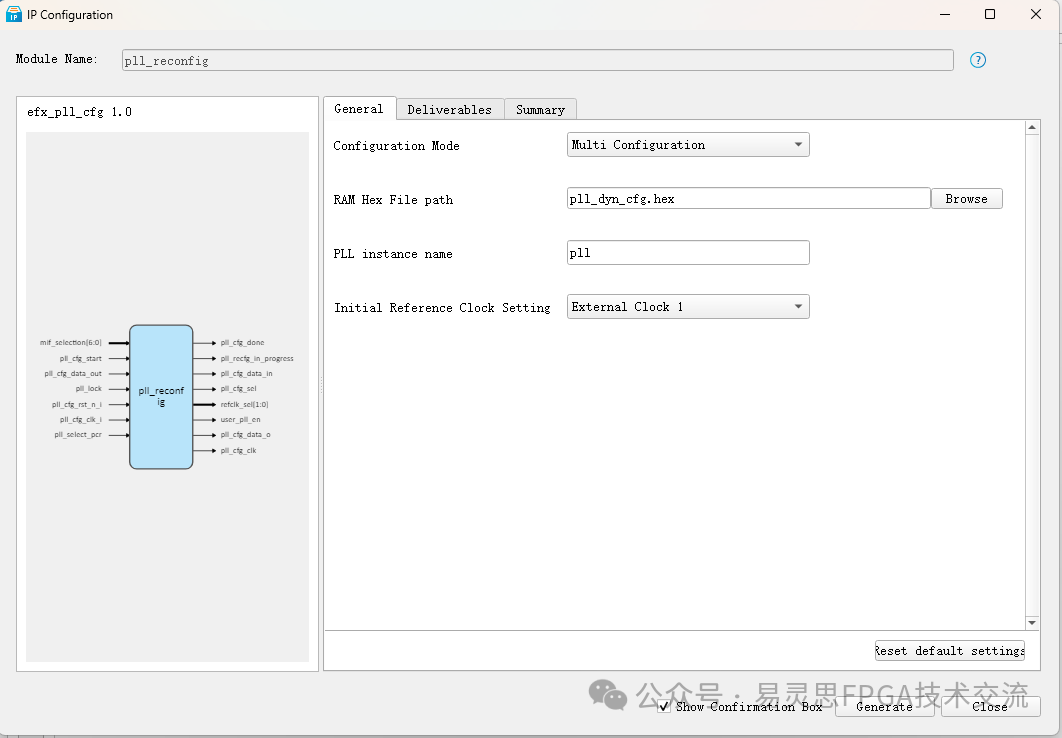

(3)添加IP.在interface里面設置完成之后就可以添加IP了

RAM Hex file path就是之前生成的hex文件的路徑;

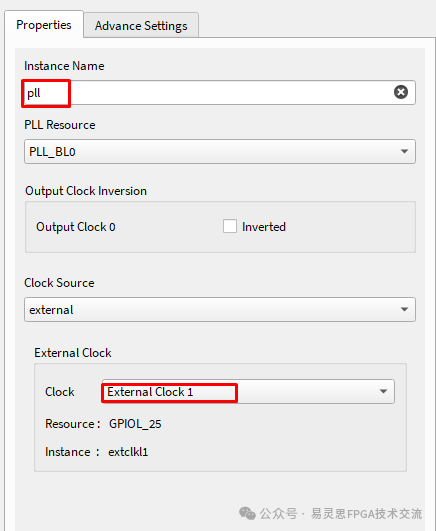

PLL instance name就是我們在interface中例化的PLL的名字;

Initial Reference clock Setting :PLL的參考時鐘的源,要對于interface中例化的PLL的參考源。再來看下PLL的配置就更清楚了。

IP 端口說明

| port | I/O | clock Domain | |

| user_pll_en | O | 連接PLL的復位信號 | |

| pll_cfg_clk | O | 動態配置時鐘,要與interface內部輸入的時鐘名一致,25 - 150MHz,應該是pll_cfg_clk_i的二分頻生成時鐘 | |

| pll_cfg_clk_i | I | 50 - 300MHz | |

| pll_cfg_rst_n_i | 復位PLL動態配置。只有pll_recfg_in_progress為低時才允許斷言。 | ||

| pll_select_pcr | I | pll_cfg_clk_i | 把PLL切回PCR設置。 |

| pll_cfg_start | I | pll_cfg_clk_i | 拉高該信號啟動PLL動態配置。實測一個時鐘周期即可。 |

PCR: Peripheral Configuration Register PLL在interface中設置的初始值 。可以通過把pll_select_pcr拉高來恢復到初始值

-

FPGA

+關注

關注

1661文章

22445瀏覽量

637510 -

易靈思

+關注

關注

6文章

65瀏覽量

5550

發布評論請先 登錄

基于易靈思eMMC IP的Linux系統加載方案

易靈思助力2025年全國大學生嵌入式芯片與系統設計競賽圓滿落幕

易靈思Sapphire SoC中RISC-V平臺級中斷控制器深度解析

易靈思助力上海集成電路緊缺人才培訓項目順利結課

易靈思2025 FPGA技術研討會成都站圓滿收官

易靈思與思特威第二屆機器視覺方案大會圓滿收官

易靈思與南京大學集成電路學院暑期課程圓滿結課

PLL技術在FPGA中的動態調頻與展頻功能應用

易靈思邀您相約2025上海國際汽車工業展覽會

易靈思 FPGA TJ375的PLL的動態配置

易靈思 FPGA TJ375的PLL的動態配置

評論