卷積是一種線性運(yùn)算,其本質(zhì)是滑動(dòng)平均思想,廣泛應(yīng)用于圖像濾波。而隨著人工智能及深度學(xué)習(xí)的發(fā)展,卷積也在神經(jīng)網(wǎng)絡(luò)中發(fā)揮重要的作用,如卷積神經(jīng)網(wǎng)絡(luò)。本參考設(shè)計(jì)主要介紹如何基于INTEL 硬浮點(diǎn)的DSP

2018-07-23 09:09:45 8401

8401

大部分運(yùn)算可以通過擴(kuò)位和近似的方式轉(zhuǎn)換為定點(diǎn)運(yùn)算。但有些算法在設(shè)計(jì)在設(shè)計(jì)的過程中就涉及大量的浮點(diǎn)運(yùn)算,在轉(zhuǎn)換為定點(diǎn)運(yùn)算時(shí)比較麻煩,會(huì)帶來龐大的工作量。

2022-09-08 15:41:56 3509

3509 近日,工業(yè)控制及智能家電領(lǐng)域的全國產(chǎn)RISC-V MCU領(lǐng)軍企業(yè)愛普特微電子正式發(fā)布了一款功能強(qiáng)大、高算力、高處理速度,可支持雙電機(jī)驅(qū)動(dòng)的全國產(chǎn)RISC-V 32位MCU—APT32F173系列

2023-10-25 09:58:37 2123

2123

的縮寫,即每秒所能夠進(jìn)行的浮點(diǎn)運(yùn)算數(shù)目(每秒浮點(diǎn)運(yùn)算量)。 ? 算力可以分為通用算力、智能算力和超算算力。早前通用算力占整體算力的比重達(dá)到90%以上,近些年隨著人工智能技術(shù)的發(fā)展,智能算力規(guī)模迅速增長(zhǎng)。從需求層面看,2022年,中國智能算力規(guī)模為268百億億次/秒(EFLOPS),已經(jīng)超過通用算力規(guī)

2024-02-06 00:08:00 8229

8229 28335 有支持64位浮點(diǎn)運(yùn)算的庫嗎?也即希望普通32位PC機(jī)上double型數(shù)據(jù)運(yùn)算程序(使用sin、atan等函數(shù))能夠在28335上正確運(yùn)行。如果沒有,哪款最低配置的芯片支持呢(優(yōu)先考慮軟件庫,其次才是硬件)?先謝謝各位的幫助。

2020-06-03 10:01:53

求用verilog實(shí)現(xiàn)浮點(diǎn)數(shù)運(yùn)算的資料,謝謝

2016-12-17 21:15:52

FPGA 如何進(jìn)行浮點(diǎn)運(yùn)算

2015-09-26 09:31:37

浮點(diǎn)運(yùn)算單元的設(shè)計(jì)和優(yōu)化可以從以下幾個(gè)方面入手:

1.浮點(diǎn)寄存器設(shè)計(jì):為了實(shí)現(xiàn)浮點(diǎn)運(yùn)算指令子集(RV32F或者RV32D),需要添加一組專用的浮點(diǎn)寄存器組,總共需要32個(gè)通用浮點(diǎn)寄存器。其中

2025-10-22 07:04:49

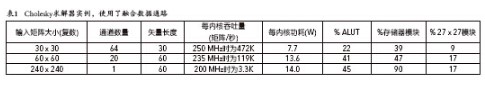

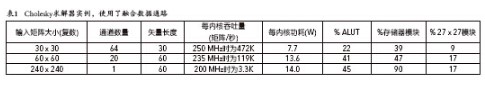

語言編寫的浮點(diǎn)矩陣相乘處理單元[1],其關(guān)鍵技術(shù)是乘累加單元的設(shè)計(jì),這樣設(shè)計(jì)的硬件,其性能依賴于設(shè)計(jì)者的編程水平。此外,FPGA廠商也推出了一定規(guī)模的浮點(diǎn)矩陣運(yùn)算IP核[2],雖然此IP核應(yīng)用了本廠家的器件,并經(jīng)過專業(yè)調(diào)試和硬件實(shí)測(cè),性能穩(wěn)定且優(yōu)于手寫代碼,但仍可對(duì)其進(jìn)行改進(jìn),以進(jìn)一步提高運(yùn)算速度。

2019-08-22 06:41:38

編者按:在計(jì)算領(lǐng)域,例如三角函數(shù)以及時(shí)域頻域變換通常會(huì)用到浮點(diǎn)運(yùn)算。當(dāng)CPU執(zhí)行一個(gè)需要浮點(diǎn)數(shù)運(yùn)算的程序時(shí),有三種方式可以執(zhí)行:軟件仿真器(浮點(diǎn)運(yùn)算函數(shù)庫)、附加浮點(diǎn)運(yùn)算器和集成浮點(diǎn)運(yùn)算單元。在控制

2021-08-27 07:51:06

CW32F030C8T7是否支持浮點(diǎn)運(yùn)算?如果需要執(zhí)行復(fù)雜的數(shù)**算,應(yīng)該如何處理?

2025-12-12 06:51:18

DM8168支持浮點(diǎn)運(yùn)算嗎?我的視頻采集經(jīng)過一個(gè)浮點(diǎn)運(yùn)算處理,視頻卡的不能動(dòng)了。求解釋

2018-06-21 03:14:22

在《ARM微控制器基礎(chǔ)與實(shí)戰(zhàn)》的 2.6.3 節(jié)有說到"浮點(diǎn)數(shù)寄存器(F0-F7...)",2104是否具有這些寄存器如果 EasyArm 不支持浮點(diǎn)運(yùn)算,而我的程序需要用到浮點(diǎn)運(yùn)算,請(qǐng)問可以實(shí)現(xiàn)嗎

2022-11-07 15:24:11

在添加浮點(diǎn)運(yùn)算單元時(shí),可以引用開源的浮點(diǎn)運(yùn)算器以簡(jiǎn)化所需工作任務(wù)壓力。在此我們采用了FPnew這個(gè)開源工程,再次介紹一些如何將其導(dǎo)成vivado工程。

首先在github上下載fpnew工程文件

2025-10-24 11:08:41

void SystemInit(void){/* FPU settings 浮點(diǎn)運(yùn)算單元設(shè)置,此處一般不執(zhí)行

2021-08-23 06:20:51

NUC980有浮點(diǎn)運(yùn)算單元嗎?另外采用外部的SPI NOR FLASH是不是不能加密呀!

2022-10-24 14:17:27

STSPIN32F0 支不支持硬件浮點(diǎn)運(yùn)算

2024-03-13 06:32:29

芯片介紹上寫浮點(diǎn)運(yùn)算能力達(dá)到20GFLOPS,是說1秒鐘能算20G次浮點(diǎn)數(shù)運(yùn)算嗎?按照主頻1.25GHz算,相當(dāng)于每ns計(jì)算16次浮點(diǎn)數(shù)運(yùn)算對(duì)嗎?那如果計(jì)算1百萬次浮點(diǎn)數(shù)加法需要多少時(shí)間呢?能不能請(qǐng)懂的人估算一下~~【我估算的和實(shí)測(cè)的差別太大了,不知道是不是估算方法出了什么問題】

2019-01-07 11:08:27

TMS320F28335浮點(diǎn)單元,進(jìn)行浮點(diǎn)運(yùn)算時(shí)會(huì)自動(dòng)選擇Q15,Q22等格式,自動(dòng)進(jìn)行精度和范圍的匹配嗎?

2013-04-06 18:33:52

Operations,浮點(diǎn)運(yùn)算次數(shù),每一個(gè)加、減、乘、除操作都算1FLOPs操作,常用來衡量模型計(jì)算復(fù)雜度。注意下FLOPS,注意全大寫,是floating point operations per

2022-12-15 21:19:38

HI論壇,在我的方式三相交流感應(yīng)電機(jī)控制,我遇到的文件“GS00 4”。它提到了一點(diǎn)“分?jǐn)?shù)乘法”,這是在匯編指令“MPY”中完成的。dsPIC的核心不支持浮點(diǎn)運(yùn)算,但DSC部分支持浮點(diǎn)運(yùn)算,對(duì)嗎?為什么XC16不定期使用這個(gè)芯片中可用的浮點(diǎn)命令?對(duì)我來說,壓倒性的參數(shù)對(duì)我來說并不重要。

2020-04-02 10:06:31

RISC-V浮點(diǎn)運(yùn)算單元(floating-point unit,簡(jiǎn)稱FPU)是一種專門用于執(zhí)行浮點(diǎn)運(yùn)算的硬件加速器,其作用是提高浮點(diǎn)運(yùn)算速度,在科學(xué)計(jì)算、圖像處理和機(jī)器學(xué)習(xí)等應(yīng)用領(lǐng)域有著廣泛

2025-10-21 14:46:51

已下是rx580顯卡算力9-11 Mh 沒有開啟計(jì)算模式,挖幾分種重啟自動(dòng)開啟,計(jì)算模式只支持WIN1022-28 Mh 原版BIOS,開啟時(shí)序,并設(shè)置超頻29-32 Mh 正常算力,卡體質(zhì)不同算力

2021-07-23 06:59:09

的支持。現(xiàn)代CPU的設(shè)計(jì)不僅注重性能的提升,還特別關(guān)注能效比和靈活性,以適應(yīng)不斷變化的計(jì)算需求。算力芯片的發(fā)展史,某種程度上就是人類智慧的結(jié)晶。從單一的算術(shù)邏輯單元到復(fù)雜的超標(biāo)量處理器,從簡(jiǎn)單的串行計(jì)算

2024-10-19 01:21:24

算力,然而當(dāng)用戶在真正運(yùn)行一個(gè)應(yīng)用時(shí),卻發(fā)現(xiàn)由于內(nèi)存帶寬的限制和架構(gòu)的限制,依然不能將所有的AI運(yùn)算單元填滿,從而導(dǎo)致計(jì)算硬件的計(jì)算效率低下。以谷歌第一代TPU為例,其平均硬件乘法陣列使用率只有28

2018-03-23 15:27:20

本帖最后由 1653149838.791300 于 2024-10-16 22:19 編輯

感謝平臺(tái)提供的書籍,厚厚的一本,很有分量,感謝作者的傾力付出成書。

本書主要講算力芯片CPU

2024-10-15 22:08:35

處理系統(tǒng)中最重要的部件之一。FPGA是當(dāng)前數(shù)字電路研究開發(fā)的一種重要實(shí)現(xiàn)形式,它與全定制ASIC電路相比,具有開發(fā)周期短、成本低等優(yōu)點(diǎn)。但多數(shù)FPGA不支持浮點(diǎn)運(yùn)算,這使FPGA在數(shù)值計(jì)算、數(shù)據(jù)分析和信號(hào)

2019-07-05 06:21:42

單元。

Unpack和Pack模塊塊將浮點(diǎn)類型轉(zhuǎn)換為符號(hào)、指數(shù)和尾數(shù)。圖中S、E、M分別代表符號(hào)、指數(shù)、尾數(shù)。這是基于IEEE-754浮點(diǎn)運(yùn)算標(biāo)準(zhǔn)。浮點(diǎn)算法實(shí)現(xiàn)塊在S、E和m上執(zhí)行計(jì)算。通過這種轉(zhuǎn)換

2025-10-22 06:48:48

。同時(shí)由于基于IEEE754標(biāo)準(zhǔn)的浮點(diǎn)運(yùn)算具有動(dòng)態(tài)范圍大,可實(shí)現(xiàn)高精度,運(yùn)算規(guī)律較定點(diǎn)運(yùn)算更為簡(jiǎn)捷等特點(diǎn),浮點(diǎn)運(yùn)算單元的設(shè)計(jì)研究已獲得廣泛的重視。

2019-09-03 08:31:04

處理系統(tǒng)中最重要的部件之一。FPGA是當(dāng)前數(shù)字電路研究開發(fā)的一種重要實(shí)現(xiàn)形式,它與全定制ASIC電路相比,具有開發(fā)周期短、成本低等優(yōu)點(diǎn)。但多數(shù)FPGA不支持浮點(diǎn)運(yùn)算,這使FPGA在數(shù)值計(jì)算、數(shù)據(jù)分析和信號(hào)

2019-08-15 08:00:45

STM32開發(fā)板ISP下載的原理是什么?STM32F4的浮點(diǎn)運(yùn)算單元是由哪些部分組成的?怎樣去計(jì)算STM32F4的浮點(diǎn)運(yùn)算單元呢?

2021-10-22 09:13:17

背景介紹數(shù)據(jù)、算法和算力是人工智能技術(shù)的三大要素。其中,算力體現(xiàn)著人工智能(AI)技術(shù)具體實(shí)現(xiàn)的能力,實(shí)現(xiàn)載體主要有CPU、GPU、FPGA和ASIC四類器件。CPU基于馮諾依曼架構(gòu),雖然靈活,卻

2021-07-26 06:47:30

本帖最后由 一只耳朵怪 于 2018-5-25 17:11 編輯

怎么樣使用TMS570LC4357片上浮點(diǎn)運(yùn)算單元(FPU)?怎么充分利用浮點(diǎn)運(yùn)算單元呢?

2018-05-25 02:22:48

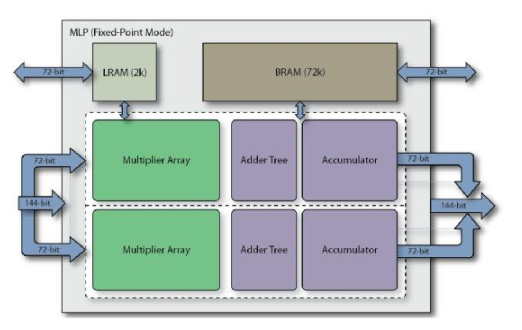

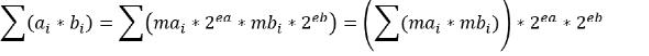

。 Achronix為了解決這一大困境,創(chuàng)新地設(shè)計(jì)了機(jī)器學(xué)習(xí)處理器(MLP)單元,不僅支持浮點(diǎn)的乘加運(yùn)算,還可以支持對(duì)多種定浮點(diǎn)數(shù)格式進(jìn)行拆分。

2020-11-26 06:42:00

介紹一種在FPGA上實(shí)現(xiàn)的單精度浮點(diǎn)加法運(yùn)算器,運(yùn)算器算法的實(shí)現(xiàn)考慮了FPGA器件本身的特點(diǎn),算法處理流程的拆分和模塊的拆分,便于流水設(shè)計(jì)的實(shí)現(xiàn)。

2021-04-29 06:27:09

的 PowerPC 440 處理器提供了一種行之有效的仿真浮點(diǎn)解決方案,但處理器內(nèi)核仍需占用數(shù)十個(gè)周期來執(zhí)行每條運(yùn)算。而采用浮點(diǎn)運(yùn)算單元 (FPU) 形式的浮點(diǎn)運(yùn)算硬件加速功能可縮短該運(yùn)算周期

2018-08-03 11:15:23

編譯選項(xiàng)選擇6700+。定點(diǎn)浮點(diǎn)結(jié)合可以在-mv編譯選項(xiàng)選擇6748。現(xiàn)在我想寫一段程序,這段程序先用浮點(diǎn)運(yùn)算計(jì)算一個(gè)公式,算完之后再用定點(diǎn)運(yùn)算計(jì)算這個(gè)公式,請(qǐng)問我該怎么實(shí)現(xiàn)呢?有什么相關(guān)的指令嗎?

2018-08-02 08:54:38

AURIX TC3xx tricore架構(gòu)下浮點(diǎn)運(yùn)算和將浮點(diǎn)數(shù)小數(shù)點(diǎn)去掉變成整數(shù)來計(jì)算哪種方式更加節(jié)省算力?

比如一個(gè)浮點(diǎn)數(shù)12.89V,如果將其寫成12890mV,再參與計(jì)算,哪種方式更加節(jié)省算力

2024-08-26 06:54:20

請(qǐng)問esp32 wroom 32u 默認(rèn)開啟硬件浮點(diǎn)運(yùn)算單元了嗎?感謝

2024-06-21 11:08:25

我們的藍(lán)牙芯片有浮點(diǎn)運(yùn)算單元嗎

2022-10-09 07:52:55

浮點(diǎn)運(yùn)算方法:

2008-01-16 09:22:37 29

29

DSP的浮點(diǎn)運(yùn)算方法

2008-01-16 09:25:05 4

4 定點(diǎn)dsp浮點(diǎn)運(yùn)算的多媒體視頻教程:

2008-01-24 09:14:21 50

50 騰視科技AI算力模組TS-SG-SM9系列搭載算能高集成度處理器CV186AH/BM1688片,功耗低、算力強(qiáng)、接口豐富、兼容性好。7.2-16TOPS INT8算力,兼容INT4/INT8

2025-10-20 10:16:03

浮點(diǎn)運(yùn)算與浮點(diǎn)運(yùn)算器

浮點(diǎn)加減法的運(yùn)算步驟 設(shè)兩個(gè)浮點(diǎn)數(shù) X=Mx※2Ex Y=My※2Ey 實(shí)現(xiàn)X±Y要用如下5步完成: ①對(duì)階操作:小階

2010-04-15 13:42:32 7293

7293 Altera公司日前演示了使用FPGA的浮點(diǎn)DSP新設(shè)計(jì)流程,這是業(yè)界第一款基于模型的浮點(diǎn)設(shè)計(jì)工具,支持在FPGA中實(shí)現(xiàn)復(fù)數(shù)浮點(diǎn)DSP算法。

2011-09-15 09:07:10 830

830 提出一種基2FFT的FPGA方法,完成了基于FPGA高精度浮點(diǎn)運(yùn)算器的FFT的設(shè)計(jì)。利用VHDL語言描述了蝶形運(yùn)算過程及地址產(chǎn)生單元,其仿真波形基本能正確的表示輸出結(jié)果。

2011-12-23 14:24:08 46

46 Float Point Unit,浮點(diǎn)運(yùn)算單元是專用于浮點(diǎn)運(yùn)算的協(xié)處理器,在計(jì)算領(lǐng)域,例如三角函數(shù)以及時(shí)域頻域變換通常會(huì)用到浮點(diǎn)運(yùn)算。

2017-09-16 11:28:47 6

6 14.10 浮點(diǎn)運(yùn)算 大多數(shù)的ARM處理器硬件上并不支持浮點(diǎn)運(yùn)算。但ARM上提供了以下幾個(gè)選項(xiàng)來實(shí)現(xiàn)浮點(diǎn)運(yùn)算。 浮點(diǎn)累加協(xié)處理器FPA(Floating-Point Accelerator):ARM

2017-10-17 16:48:39 1

1 浮點(diǎn)算法不遵循整數(shù)算法規(guī)則,但利用 FPGA 或者基于 FPGA 的嵌入式處理器不難設(shè)計(jì)出精確的浮點(diǎn)系統(tǒng)。工程人員一看到浮點(diǎn)運(yùn)算就會(huì)頭疼,因?yàn)?b class="flag-6" style="color: red">浮點(diǎn)運(yùn)算用軟件實(shí)現(xiàn)速度慢,用硬件實(shí)現(xiàn)則占用資源多。理解

2017-11-22 16:51:08 2072

2072 本文將詳細(xì)介紹如何使用硬件浮點(diǎn)單元以及相關(guān)數(shù)學(xué)運(yùn)算。 二.問題產(chǎn)生原因 1. ------對(duì)于Keil MDK Version 5 版本, 編譯器已經(jīng)完全支持STM32F4xx 的FPU(浮點(diǎn)運(yùn)算單元

2017-11-29 15:57:01 1750

1750

本文將詳細(xì)介紹如何使用硬件浮點(diǎn)單元以及相關(guān)數(shù)學(xué)運(yùn)算。 二.問題產(chǎn)生原因 1. ------對(duì)于Keil MDK Version 5 版本, 編譯器已經(jīng)完全支持STM32F4xx 的FPU(浮點(diǎn)運(yùn)算單元

2017-11-29 17:48:46 1170

1170

2014年4月23號(hào),北京Altera公司 (Nasdaq: ALTR) 今天宣布在FPGA浮點(diǎn)DSP性能方面實(shí)現(xiàn)了變革。Altera是第一家在FPGA中集成硬核IEEE 754兼容浮點(diǎn)運(yùn)算功能

2018-02-11 13:34:00 7749

7749 為什么 CPU 的浮點(diǎn)運(yùn)算能力比 GPU 差,為什么不提高 CPU 的浮點(diǎn)運(yùn)算能力?

2018-03-16 15:12:02 16274

16274 ,其速度直接影響DSP的速度,因此國內(nèi)外學(xué)者對(duì)提高浮點(diǎn)乘加單元的性能進(jìn)行了大量的研究。浮點(diǎn)運(yùn)算單元的設(shè)計(jì)主要是在速度和所占用資源之間進(jìn)行權(quán)衡。 本文以實(shí)時(shí)信號(hào)處理為應(yīng)用背景,首先介紹了單精度浮點(diǎn)格式,然后從速度和占用

2018-04-10 10:47:21 8

8 浮點(diǎn)運(yùn)算是計(jì)算機(jī)運(yùn)算的重要方式,較之定點(diǎn)運(yùn)算有著計(jì)數(shù)范圍寬有效精度高的特點(diǎn)。在各種工程計(jì)算和科學(xué)計(jì)算中有著廣泛應(yīng)用。目前浮點(diǎn)運(yùn)算大多采用DSP芯片實(shí)現(xiàn),具有算法簡(jiǎn)單,精度高的優(yōu)點(diǎn)。但同時(shí)由于浮點(diǎn)運(yùn)算

2018-04-10 14:25:53 17

17 以往FPGA在進(jìn)行浮點(diǎn)運(yùn)算時(shí),為符合IEEE 754標(biāo)準(zhǔn),每次運(yùn)算都需要去歸一化和歸一化步驟,導(dǎo)致了極大的性能瓶頸。因?yàn)檫@些歸一化和去歸一化步驟一般通過FPGA中的大規(guī)模桶形移位寄存器實(shí)現(xiàn),需要大量

2020-01-14 16:19:55 4101

4101

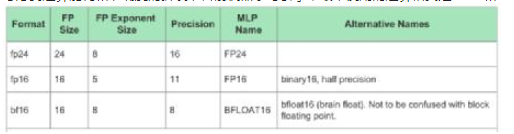

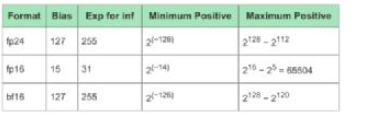

隨著機(jī)器學(xué)習(xí)(Machine Learning)領(lǐng)域越來越多地使用現(xiàn)場(chǎng)可編程門陣列(FPGA)來進(jìn)行推理(inference)加速,而傳統(tǒng)FPGA只支持定點(diǎn)運(yùn)算的瓶頸越發(fā)凸顯。

2020-04-30 11:31:32 1407

1407 隨著機(jī)器學(xué)習(xí)(Machine Learning)領(lǐng)域越來越多地使用現(xiàn)場(chǎng)可編程門陣列(FPGA)來進(jìn)行推理(inference)加速,而傳統(tǒng)FPGA只支持定點(diǎn)運(yùn)算的瓶頸越發(fā)凸顯。

2020-05-12 10:46:50 838

838 高性能浮點(diǎn)處理一直與高性能 CPU 相關(guān)聯(lián)。在過去幾年中,GPU 也成為功能強(qiáng)大的浮點(diǎn)處理平臺(tái),超越了圖形,稱為 GPGPU(通用圖形處理單元)。新創(chuàng)新是在苛刻的應(yīng)用中實(shí)現(xiàn)基于 FPGA 的浮點(diǎn)處理

2020-12-22 13:33:00 14

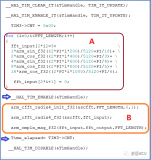

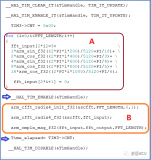

14 這里通過調(diào)用DSP庫里的FFT相關(guān)函數(shù)實(shí)現(xiàn)1024點(diǎn)的FFT運(yùn)算,樣點(diǎn)數(shù)據(jù)及運(yùn)算結(jié)果均為浮點(diǎn)數(shù)。 上圖中A區(qū)代碼是做樣點(diǎn)數(shù)據(jù)準(zhǔn)備,B區(qū)代碼完成FFT運(yùn)算。我們來一起看看基本的配置以及不啟用硬件浮點(diǎn)單元和啟用硬件浮點(diǎn)單元執(zhí)行B區(qū)代碼的時(shí)間上的差別。 程序里要調(diào)用

2021-01-02 18:09:00 9859

9859

該問題由某客戶提出,發(fā)生在 STM32F407IGT6 器件上。據(jù)其工程師講述:由于在其產(chǎn)品中,需要使用STM32進(jìn)行大量的浮點(diǎn)數(shù)以及浮點(diǎn)DSP運(yùn)算,所以針對(duì)STM32的浮點(diǎn)數(shù)運(yùn)算能力及 DSP

2021-04-28 15:17:02 10

10 有些FPGA中是不能直接對(duì)浮點(diǎn)數(shù)進(jìn)行操作的,只能采用定點(diǎn)數(shù)進(jìn)行數(shù)值運(yùn)算。對(duì)于FPGA而言,參與數(shù)學(xué)運(yùn)算的書就是16位的整型數(shù),但如果數(shù)學(xué)運(yùn)算中出現(xiàn)小數(shù)怎么辦呢?要知道,FPGA對(duì)小數(shù)是無能為力

2021-08-12 09:53:39 5486

5486 編者按:在計(jì)算領(lǐng)域,例如三角函數(shù)以及時(shí)域頻域變換通常會(huì)用到浮點(diǎn)運(yùn)算。當(dāng)CPU執(zhí)行一個(gè)需要浮點(diǎn)數(shù)運(yùn)算的程序時(shí),有三種方式可以執(zhí)行:軟件仿真器(浮點(diǎn)運(yùn)算函數(shù)庫)、附加浮點(diǎn)運(yùn)算器和集成浮點(diǎn)運(yùn)算單元。在控制

2021-12-04 13:36:05 19

19 使用插值算法實(shí)現(xiàn)圖像縮放是數(shù)字圖像處理算法中經(jīng)常遇到的問題。我們經(jīng)常會(huì)將某種尺寸的圖像轉(zhuǎn)換為其他尺寸的圖像,如放大或者縮小圖像。由于在縮放的過程中會(huì)遇到浮點(diǎn)數(shù),如何在FPGA中正確的處理浮點(diǎn)數(shù)運(yùn)算是在FPGA中實(shí)現(xiàn)圖像縮放的關(guān)鍵。

2022-03-18 11:03:41 5929

5929 FPGA在常規(guī)運(yùn)算時(shí)不能進(jìn)行浮點(diǎn)運(yùn)算,只能進(jìn)行定點(diǎn)整型運(yùn)算,在處理數(shù)據(jù)的小數(shù)乘加運(yùn)算和除法運(yùn)算時(shí)FPGA一般是無能為力的,其中一種常用的處理方法就是數(shù)據(jù)進(jìn)行浮點(diǎn)到定點(diǎn)的轉(zhuǎn)換。

2022-10-13 16:23:50 6173

6173 數(shù)據(jù)中心和超算需要高于1000 TOPS的高算力芯片。當(dāng)前,超算中心算力已經(jīng)進(jìn)入E級(jí)算力(百億億次運(yùn)算每秒)時(shí)代,并正在向Z(千E)級(jí)算力發(fā)展。2022年5月登頂世界超算500強(qiáng)榜單的美國國防部橡樹

2022-12-09 11:29:59 4592

4592 我們使用的處理器一般情況下,要么直接支持硬件的 浮點(diǎn)運(yùn)算 ,比如某些帶有FPU的器件,要么就只支持定點(diǎn)運(yùn)算,此時(shí)對(duì) 浮點(diǎn) 數(shù)的處理需要通過編譯器來完成。在支持硬件浮點(diǎn)處理的器件上,對(duì) 浮點(diǎn)運(yùn)算

2022-12-09 12:25:09 3815

3815 MLP全稱Machine Learning Processing單元,是由一組至多32個(gè)乘法器的陣列,以及一個(gè)加法樹、累加器、還有四舍五入rounding/飽和saturation/歸一化normalize功能塊。

2023-02-27 10:45:30 600

600 隨著 機(jī)器學(xué)習(xí) (Machine Learning)領(lǐng)域越來越多地使用現(xiàn)場(chǎng)可 編程 門陣列( FPGA )來進(jìn)行推理(inference)加速,而傳統(tǒng)FPGA只支持定點(diǎn)運(yùn)算的瓶頸越發(fā)凸顯

2023-03-11 13:05:07 1285

1285 據(jù)統(tǒng)計(jì)預(yù)測(cè),全球算力需求呈現(xiàn)高速發(fā)展態(tài)勢(shì)。2021年,全球計(jì)算設(shè)備算力總規(guī)模達(dá)到615EFLOPS(每秒一百京次(=10^18)浮點(diǎn)運(yùn)算);到2025年,全球算力規(guī)模將達(dá)6.8 ZFLOPS( 每秒

2023-05-22 09:36:28 1376

1376

新形勢(shì)下,算力前沿技術(shù)未來的發(fā)展趨勢(shì)。華為數(shù)據(jù)通信產(chǎn)品線數(shù)據(jù)中心網(wǎng)絡(luò)領(lǐng)域副總裁張白發(fā)表了主題為《華為星河AI網(wǎng)絡(luò),高運(yùn)力釋放AI時(shí)代高算力》的演講。 華為數(shù)據(jù)通信產(chǎn)品線數(shù)據(jù)中心網(wǎng)絡(luò)領(lǐng)域 副總裁 張白發(fā)表主題演講 張白表示:“自2020年

2023-08-18 18:15:06 1756

1756 ,浮點(diǎn)加法器是現(xiàn)代信號(hào)處理系統(tǒng)中最重要的部件之一。FPGA是當(dāng)前數(shù)字電路研究開發(fā)的一種重要實(shí)現(xiàn)形式,它與全定制ASIC電路相比,具有開發(fā)周期短、成本低等優(yōu)點(diǎn)。 但多數(shù)FPGA不支持浮點(diǎn)運(yùn)算,這使FPGA在數(shù)值計(jì)算、數(shù)據(jù)分析和信號(hào)處理等方

2023-09-22 10:40:03 2116

2116

近日,工業(yè)控制及智能家電領(lǐng)域的全國產(chǎn)RISC-VMCU領(lǐng)軍企業(yè)愛普特微電子正式發(fā)布了一款功能強(qiáng)大、高算力、高處理速度,可支持雙電機(jī)驅(qū)動(dòng)的全國產(chǎn)RISC-V32位MCU—APT32F173系列

2023-10-26 08:18:55 1593

1593

運(yùn)算的運(yùn)算步驟遠(yuǎn)比定點(diǎn)運(yùn)算繁瑣,運(yùn)算速度慢且所需硬件資源大大增加,因此基于浮點(diǎn)運(yùn)算的LMS算法的硬件實(shí)現(xiàn)一直以來是學(xué)者們研究的難點(diǎn)和熱點(diǎn)。 本文正是基于這種高效結(jié)構(gòu)的多輸入FPA,在FPGA上成功實(shí)現(xiàn)了基于浮點(diǎn)運(yùn)算的LMS算法。測(cè)試

2023-12-21 16:40:01 1590

1590 支持硬件浮點(diǎn)運(yùn)算單元(FPU),可以提供快速和高效的浮點(diǎn)運(yùn)算性能。本文將詳細(xì)介紹 STM32F407 的浮點(diǎn)運(yùn)算速度。 浮點(diǎn)運(yùn)算是很多應(yīng)用中常用的一種運(yùn)算類型,特別是對(duì)于需要進(jìn)行較復(fù)雜計(jì)算的任務(wù),如圖像處理、信號(hào)處理和物理模擬等。傳統(tǒng)的處理器對(duì)于浮點(diǎn)運(yùn)算的支持有限,需要通過軟件庫實(shí)現(xiàn)

2024-01-04 10:58:34 5181

5181 隨著國家大力發(fā)展數(shù)字經(jīng)濟(jì),算力的提升和普惠變得越來越重要。在數(shù)字化時(shí)代,算力已成為推動(dòng)科技發(fā)展和創(chuàng)新的關(guān)鍵要素。

2024-01-18 18:20:22 6204

6204

的?要想提高算力,都有哪些方法?一、算力的關(guān)鍵因素從算力的常見計(jì)量單位FPOPS(FloatingPointOperationsPerSecond,浮點(diǎn)運(yùn)算次數(shù)/秒)、

2024-07-11 08:04:57 104

104

由于定點(diǎn)的四則運(yùn)算比較簡(jiǎn)單,如加減法只要注意符號(hào)擴(kuò)展,小數(shù)點(diǎn)對(duì)齊等問題即可。在本文中,運(yùn)用在前一節(jié)中描述的自定義浮點(diǎn)格式FPGA中數(shù)的表示方法(下),完成浮點(diǎn)四則運(yùn)算的實(shí)現(xiàn)過程 1.自定義浮點(diǎn)格式加

2024-11-16 11:19:23 2139

2139

由于定點(diǎn)的四則運(yùn)算比較簡(jiǎn)單,如加減法只要注意符號(hào)擴(kuò)展,小數(shù)點(diǎn)對(duì)齊等問題即可。在本文中,運(yùn)用在前一節(jié)中描述的自定義浮點(diǎn)格式FPGA中數(shù)的表示方法(下),完成浮點(diǎn)四則運(yùn)算的實(shí)現(xiàn)過程 1.自定義浮點(diǎn)格式加

2024-11-16 12:51:57 1323

1323

本文系統(tǒng)地整理和解釋了算力領(lǐng)域中常用的數(shù)十個(gè)關(guān)鍵名詞,并按照以下維度進(jìn)行了分類:基礎(chǔ)概念、系統(tǒng)架構(gòu)、硬件架構(gòu)、基礎(chǔ)運(yùn)算類型、計(jì)算模式、相關(guān)軟件架構(gòu)與部署模式、浮點(diǎn)精度格式、算力類型、算力關(guān)聯(lián)與服務(wù)

2025-04-07 11:21:03 1308

1308

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論