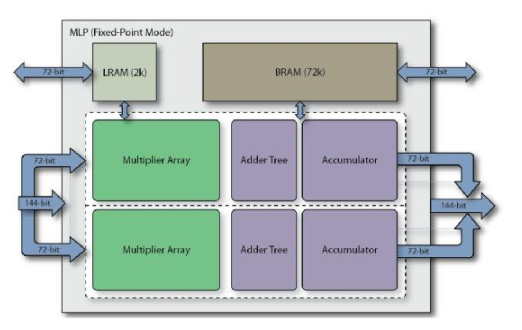

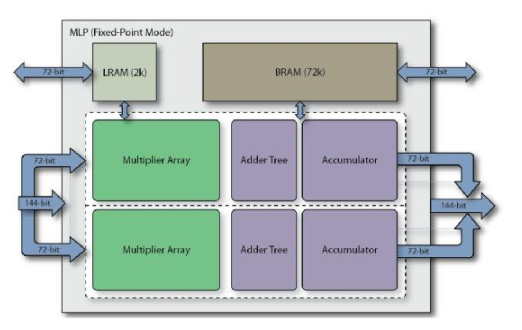

MLP全稱Machine Learning Processing單元,是由一組至多32個乘法器的陣列,以及一個加法樹、累加器、還有四舍五入rounding/飽和saturation/歸一化normalize功能塊。

2020-03-03 17:28:08 2073

2073

大部分運算可以通過擴位和近似的方式轉(zhuǎn)換為定點運算。但有些算法在設(shè)計在設(shè)計的過程中就涉及大量的浮點運算,在轉(zhuǎn)換為定點運算時比較麻煩,會帶來龐大的工作量。

2022-09-08 15:41:56 3509

3509 的縮寫,即每秒所能夠進(jìn)行的浮點運算數(shù)目(每秒浮點運算量)。 ? 算力可以分為通用算力、智能算力和超算算力。早前通用算力占整體算力的比重達(dá)到90%以上,近些年隨著人工智能技術(shù)的發(fā)展,智能算力規(guī)模迅速增長。從需求層面看,2022年,中國智能算力規(guī)模為268百億億次/秒(EFLOPS),已經(jīng)超過通用算力規(guī)

2024-02-06 00:08:00 8229

8229 一場【2020年5G技術(shù)創(chuàng)新研討會】,計劃邀請阿里云、華為、高通、中國移動、Qorvo、是德科技、高管與大家分享他們的獨到看見與市場洞察力,為大家拓展人脈和發(fā)掘商機創(chuàng)建一個不可多得的國際性

2020-01-14 09:23:54

FPGA 如何進(jìn)行浮點運算

2015-09-26 09:31:37

。同時,這樣的理念會幫助企業(yè)發(fā)展的更快。石萬鵬鼓勵企業(yè)要著眼長遠(yuǎn),苦練內(nèi)功,狠抓技術(shù)創(chuàng)新,狠抓科學(xué)管理,不斷提升核心競爭力和持續(xù)發(fā)展能力,瞄準(zhǔn)世界產(chǎn)業(yè)技術(shù)前沿,不斷突破更多核心和關(guān)鍵技術(shù),努力搶占未來

2009-12-10 14:45:21

浮點運算單元的設(shè)計和優(yōu)化可以從以下幾個方面入手:

1.浮點寄存器設(shè)計:為了實現(xiàn)浮點運算指令子集(RV32F或者RV32D),需要添加一組專用的浮點寄存器組,總共需要32個通用浮點寄存器。其中

2025-10-22 07:04:49

語言編寫的浮點矩陣相乘處理單元[1],其關(guān)鍵技術(shù)是乘累加單元的設(shè)計,這樣設(shè)計的硬件,其性能依賴于設(shè)計者的編程水平。此外,FPGA廠商也推出了一定規(guī)模的浮點矩陣運算IP核[2],雖然此IP核應(yīng)用了本廠家的器件,并經(jīng)過專業(yè)調(diào)試和硬件實測,性能穩(wěn)定且優(yōu)于手寫代碼,但仍可對其進(jìn)行改進(jìn),以進(jìn)一步提高運算速度。

2019-08-22 06:41:38

CW32F030C8T7是否支持浮點運算?如果需要執(zhí)行復(fù)雜的數(shù)**算,應(yīng)該如何處理?

2025-12-12 06:51:18

DM8168支持浮點運算嗎?我的視頻采集經(jīng)過一個浮點運算處理,視頻卡的不能動了。求解釋

2018-06-21 03:14:22

在《ARM微控制器基礎(chǔ)與實戰(zhàn)》的 2.6.3 節(jié)有說到"浮點數(shù)寄存器(F0-F7...)",2104是否具有這些寄存器如果 EasyArm 不支持浮點運算,而我的程序需要用到浮點運算,請問可以實現(xiàn)嗎

2022-11-07 15:24:11

在添加浮點運算單元時,可以引用開源的浮點運算器以簡化所需工作任務(wù)壓力。在此我們采用了FPnew這個開源工程,再次介紹一些如何將其導(dǎo)成vivado工程。

首先在github上下載fpnew工程文件

2025-10-24 11:08:41

void SystemInit(void){/* FPU settings 浮點運算單元設(shè)置,此處一般不執(zhí)行

2021-08-23 06:20:51

NUC980有浮點運算單元嗎?另外采用外部的SPI NOR FLASH是不是不能加密呀!

2022-10-24 14:17:27

STSPIN32F0 支不支持硬件浮點運算

2024-03-13 06:32:29

芯片介紹上寫浮點運算能力達(dá)到20GFLOPS,是說1秒鐘能算20G次浮點數(shù)運算嗎?按照主頻1.25GHz算,相當(dāng)于每ns計算16次浮點數(shù)運算對嗎?那如果計算1百萬次浮點數(shù)加法需要多少時間呢?能不能請懂的人估算一下~~【我估算的和實測的差別太大了,不知道是不是估算方法出了什么問題】

2019-01-07 11:08:27

TMS320F28335浮點單元,進(jìn)行浮點運算時會自動選擇Q15,Q22等格式,自動進(jìn)行精度和范圍的匹配嗎?

2013-04-06 18:33:52

Operations,浮點運算次數(shù),每一個加、減、乘、除操作都算1FLOPs操作,常用來衡量模型計算復(fù)雜度。注意下FLOPS,注意全大寫,是floating point operations per

2022-12-15 21:19:38

HI論壇,在我的方式三相交流感應(yīng)電機控制,我遇到的文件“GS00 4”。它提到了一點“分?jǐn)?shù)乘法”,這是在匯編指令“MPY”中完成的。dsPIC的核心不支持浮點運算,但DSC部分支持浮點運算,對嗎?為什么XC16不定期使用這個芯片中可用的浮點命令?對我來說,壓倒性的參數(shù)對我來說并不重要。

2020-04-02 10:06:31

RISC-V浮點運算單元(floating-point unit,簡稱FPU)是一種專門用于執(zhí)行浮點運算的硬件加速器,其作用是提高浮點運算速度,在科學(xué)計算、圖像處理和機器學(xué)習(xí)等應(yīng)用領(lǐng)域有著廣泛

2025-10-21 14:46:51

已下是rx580顯卡算力9-11 Mh 沒有開啟計算模式,挖幾分種重啟自動開啟,計算模式只支持WIN1022-28 Mh 原版BIOS,開啟時序,并設(shè)置超頻29-32 Mh 正常算力,卡體質(zhì)不同算力

2021-07-23 06:59:09

。浮點數(shù)單元則專門處理浮點運算,其中加法器和乘法器的設(shè)計直接影響了CPU的浮點性能。SIMD(單指令多數(shù)據(jù))技術(shù)如MMX、SSE、AVX等指令集的演進(jìn),體現(xiàn)了并行計算在CPU層面的應(yīng)用。以AVX-512為例

2024-10-19 01:21:24

算力,然而當(dāng)用戶在真正運行一個應(yīng)用時,卻發(fā)現(xiàn)由于內(nèi)存帶寬的限制和架構(gòu)的限制,依然不能將所有的AI運算單元填滿,從而導(dǎo)致計算硬件的計算效率低下。以谷歌第一代TPU為例,其平均硬件乘法陣列使用率只有28

2018-03-23 15:27:20

本帖最后由 1653149838.791300 于 2024-10-16 22:19 編輯

感謝平臺提供的書籍,厚厚的一本,很有分量,感謝作者的傾力付出成書。

本書主要講算力芯片CPU

2024-10-15 22:08:35

處理系統(tǒng)中最重要的部件之一。FPGA是當(dāng)前數(shù)字電路研究開發(fā)的一種重要實現(xiàn)形式,它與全定制ASIC電路相比,具有開發(fā)周期短、成本低等優(yōu)點。但多數(shù)FPGA不支持浮點運算,這使FPGA在數(shù)值計算、數(shù)據(jù)分析和信號

2019-07-05 06:21:42

引言

想要實現(xiàn)浮點運算功能,如果自己寫Verilog代碼,需要花費較多的時間和精力。好在Simulink HDL Coder工具箱提供了自動代碼生成技術(shù)。下圖展示了HDL Coder如何生成浮點運算

2025-10-22 06:48:48

處理系統(tǒng)中最重要的部件之一。FPGA是當(dāng)前數(shù)字電路研究開發(fā)的一種重要實現(xiàn)形式,它與全定制ASIC電路相比,具有開發(fā)周期短、成本低等優(yōu)點。但多數(shù)FPGA不支持浮點運算,這使FPGA在數(shù)值計算、數(shù)據(jù)分析和信號

2019-08-15 08:00:45

高性能浮點處理一直與高性能CPU相關(guān)聯(lián)。在過去幾年中,GPU也成為功能強大的浮點處理平臺,超越了圖形,稱為GP-GPU(通用圖形處理單元)。新創(chuàng)新是在苛刻的應(yīng)用中實現(xiàn)基于FPGA的浮點處理。

2019-10-21 08:15:23

STM32開發(fā)板ISP下載的原理是什么?STM32F4的浮點運算單元是由哪些部分組成的?怎樣去計算STM32F4的浮點運算單元呢?

2021-10-22 09:13:17

背景介紹數(shù)據(jù)、算法和算力是人工智能技術(shù)的三大要素。其中,算力體現(xiàn)著人工智能(AI)技術(shù)具體實現(xiàn)的能力,實現(xiàn)載體主要有CPU、GPU、FPGA和ASIC四類器件。CPU基于馮諾依曼架構(gòu),雖然靈活,卻

2021-07-26 06:47:30

。 Achronix為了解決這一大困境,創(chuàng)新地設(shè)計了機器學(xué)習(xí)處理器(MLP)單元,不僅支持浮點的乘加運算,還可以支持對多種定浮點數(shù)格式進(jìn)行拆分。

2020-11-26 06:42:00

的 PowerPC 440 處理器提供了一種行之有效的仿真浮點解決方案,但處理器內(nèi)核仍需占用數(shù)十個周期來執(zhí)行每條運算。而采用浮點運算單元 (FPU) 形式的浮點運算硬件加速功能可縮短該運算周期

2018-08-03 11:15:23

`電源技術(shù)創(chuàng)新設(shè)計專輯`

2012-08-17 21:59:50

其它競爭對手而言是具有不可復(fù)制性的,其市場競爭力的強弱也就不言而喻了。而一些只注重在產(chǎn)品應(yīng)用層面上的創(chuàng)新,產(chǎn)品的基本根本未有任何改變的企業(yè),其競爭力必將受到影響。技術(shù)創(chuàng)新的同時也必須從產(chǎn)品內(nèi)部展開

2017-06-23 10:56:12

是具有不可復(fù)制性的,其市場競爭力的強弱也就不言而喻了。而一些只注重在產(chǎn)品應(yīng)用層面上的創(chuàng)新,產(chǎn)品的基本根本未有任何改變的企業(yè),其競爭力必將受到影響。技術(shù)創(chuàng)新的同時也必須從產(chǎn)品內(nèi)部展開,比如說電源芯片技術(shù)

2017-06-28 10:37:11

突出貢獻(xiàn)的創(chuàng)新技術(shù),鼓勵更多企業(yè)投入技術(shù)創(chuàng)新,以提高生產(chǎn)力、經(jīng)濟(jì)效益;給用戶提供更大便利;達(dá)到智慧生活、智能制造,智慧出行及可持續(xù)發(fā)展的目的。活動以其公正、客觀的評選流程倍受業(yè)界廣泛關(guān)注,已成為中國具有

2019-07-11 04:20:24

請問技術(shù)創(chuàng)新是如何推動設(shè)計工藝發(fā)展的?

2021-04-21 06:46:39

AURIX TC3xx tricore架構(gòu)下浮點運算和將浮點數(shù)小數(shù)點去掉變成整數(shù)來計算哪種方式更加節(jié)省算力?

比如一個浮點數(shù)12.89V,如果將其寫成12890mV,再參與計算,哪種方式更加節(jié)省算力

2024-08-26 06:54:20

請問esp32 wroom 32u 默認(rèn)開啟硬件浮點運算單元了嗎?感謝

2024-06-21 11:08:25

我們的藍(lán)牙芯片有浮點運算單元嗎

2022-10-09 07:52:55

新的接口標(biāo)準(zhǔn)之上能帶來更好的音質(zhì),從整個手機行業(yè)確實算的上先行技術(shù)創(chuàng)新,但是對于用戶來說呢?在整個行業(yè)并未建立起完整生態(tài)的時候,附送一根轉(zhuǎn)接器的解決做法確實噱頭大于創(chuàng)新!3. 虹膜眼球識別在用戶可以“最低

2016-10-18 22:14:25

,華大北斗專注于北斗GNSS衛(wèi)星導(dǎo)航定位芯片領(lǐng)域,不斷提高芯片設(shè)計核心技術(shù)水平,始終堅持基于先進(jìn)工藝的高集成度一體化SoC設(shè)計架構(gòu)和創(chuàng)新設(shè)計理念。技術(shù)創(chuàng)新是刻在華大北斗人骨子里的基因,是不斷驅(qū)動

2023-09-22 14:46:30

2024年8月26日下午,飛凌嵌入式技術(shù)創(chuàng)新日深圳站在深圳威尼斯英迪格酒店盛大舉行,此次活動匯聚了近200位嵌入式技術(shù)領(lǐng)域的專家和企業(yè)代表,共享嵌入式技術(shù)的盛宴,共創(chuàng)嵌入式技術(shù)的美好未來!

進(jìn)入活動

2024-08-28 09:06:40

浮點運算方法:

2008-01-16 09:22:37 29

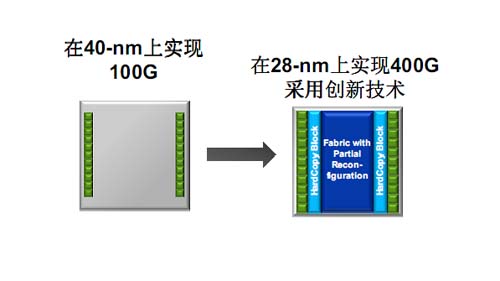

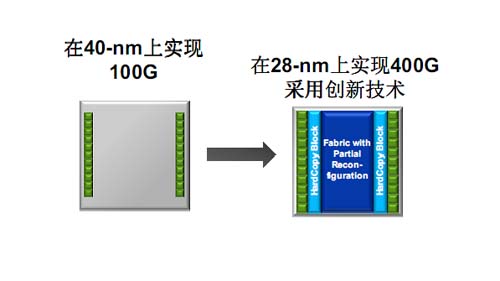

29 Altera 發(fā)布28-nm FPGA技術(shù)創(chuàng)新

Altera公司宣布了在即將推出的28nm FPGA中采用的創(chuàng)新技術(shù):嵌入式HardCopy®模塊、部分重新配置新方法以及嵌入式28-Gbps收發(fā)器,這些技術(shù)將極

2010-02-02 09:52:09 1025

1025 Altera發(fā)布28nm FPGA技術(shù)創(chuàng)新

基于技術(shù)上保持領(lǐng)先的歷史,Altera公司2月2日宣布了即將推出的28nm FPGA中采用的創(chuàng)新技術(shù):嵌入式HardCopy模塊、部分重新配置新方法以及嵌入式

2010-02-04 08:37:57 848

848 28nm下求變革,Altera三大技術(shù)創(chuàng)新欲開啟FPGA新時代

“市場對于高帶寬的需求越來越迫切,傳統(tǒng)摩爾定律顯然無法完全解決現(xiàn)階段的問題。高帶寬,低功耗,小面積。。

2010-02-04 09:16:39 968

968

浮點運算與浮點運算器

浮點加減法的運算步驟 設(shè)兩個浮點數(shù) X=Mx※2Ex Y=My※2Ey 實現(xiàn)X±Y要用如下5步完成: ①對階操作:小階

2010-04-15 13:42:32 7293

7293 提出一種基2FFT的FPGA方法,完成了基于FPGA高精度浮點運算器的FFT的設(shè)計。利用VHDL語言描述了蝶形運算過程及地址產(chǎn)生單元,其仿真波形基本能正確的表示輸出結(jié)果。

2011-12-23 14:24:08 46

46 Float Point Unit,浮點運算單元是專用于浮點運算的協(xié)處理器,在計算領(lǐng)域,例如三角函數(shù)以及時域頻域變換通常會用到浮點運算。

2017-09-16 11:28:47 6

6 14.10 浮點運算 大多數(shù)的ARM處理器硬件上并不支持浮點運算。但ARM上提供了以下幾個選項來實現(xiàn)浮點運算。 浮點累加協(xié)處理器FPA(Floating-Point Accelerator):ARM

2017-10-17 16:48:39 1

1 本文將詳細(xì)介紹如何使用硬件浮點單元以及相關(guān)數(shù)學(xué)運算。 二.問題產(chǎn)生原因 1. ------對于Keil MDK Version 5 版本, 編譯器已經(jīng)完全支持STM32F4xx 的FPU(浮點運算單元

2017-11-29 15:57:01 1750

1750

本文將詳細(xì)介紹如何使用硬件浮點單元以及相關(guān)數(shù)學(xué)運算。 二.問題產(chǎn)生原因 1. ------對于Keil MDK Version 5 版本, 編譯器已經(jīng)完全支持STM32F4xx 的FPU(浮點運算單元

2017-11-29 17:48:46 1170

1170

,其速度直接影響DSP的速度,因此國內(nèi)外學(xué)者對提高浮點乘加單元的性能進(jìn)行了大量的研究。浮點運算單元的設(shè)計主要是在速度和所占用資源之間進(jìn)行權(quán)衡。 本文以實時信號處理為應(yīng)用背景,首先介紹了單精度浮點格式,然后從速度和占用

2018-04-10 10:47:21 8

8 結(jié)構(gòu)復(fù)雜,采用DSP實現(xiàn)會增加系統(tǒng)負(fù)擔(dān),降低系統(tǒng)速度。在某些對速度要求較高的情況,必須采用專門的浮點運算處理器。 EDA/FPGA技術(shù)不斷發(fā)展,其高速、應(yīng)用靈活、低成本的優(yōu)點使其廣泛應(yīng)用數(shù)字信號處理領(lǐng)域。在FPCA技術(shù)應(yīng)用的初期,

2018-04-10 14:25:53 17

17 隨著機器學(xué)習(xí)(Machine Learning)領(lǐng)域越來越多地使用現(xiàn)場可編程門陣列(FPGA)來進(jìn)行推理(inference)加速,而傳統(tǒng)FPGA只支持定點運算的瓶頸越發(fā)凸顯。

2020-04-30 11:31:32 1407

1407 高性能浮點處理一直與高性能 CPU 相關(guān)聯(lián)。在過去幾年中,GPU 也成為功能強大的浮點處理平臺,超越了圖形,稱為 GPGPU(通用圖形處理單元)。新創(chuàng)新是在苛刻的應(yīng)用中實現(xiàn)基于 FPGA 的浮點處理

2020-12-22 13:33:00 14

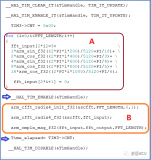

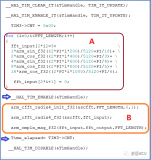

14 這里通過調(diào)用DSP庫里的FFT相關(guān)函數(shù)實現(xiàn)1024點的FFT運算,樣點數(shù)據(jù)及運算結(jié)果均為浮點數(shù)。 上圖中A區(qū)代碼是做樣點數(shù)據(jù)準(zhǔn)備,B區(qū)代碼完成FFT運算。我們來一起看看基本的配置以及不啟用硬件浮點單元和啟用硬件浮點單元執(zhí)行B區(qū)代碼的時間上的差別。 程序里要調(diào)用

2021-01-02 18:09:00 9859

9859

有些FPGA中是不能直接對浮點數(shù)進(jìn)行操作的,只能采用定點數(shù)進(jìn)行數(shù)值運算。對于FPGA而言,參與數(shù)學(xué)運算的書就是16位的整型數(shù),但如果數(shù)學(xué)運算中出現(xiàn)小數(shù)怎么辦呢?要知道,FPGA對小數(shù)是無能為力

2021-08-12 09:53:39 5486

5486 編者按:在計算領(lǐng)域,例如三角函數(shù)以及時域頻域變換通常會用到浮點運算。當(dāng)CPU執(zhí)行一個需要浮點數(shù)運算的程序時,有三種方式可以執(zhí)行:軟件仿真器(浮點運算函數(shù)庫)、附加浮點運算器和集成浮點運算單元。在控制

2021-12-04 13:36:05 19

19 使用插值算法實現(xiàn)圖像縮放是數(shù)字圖像處理算法中經(jīng)常遇到的問題。我們經(jīng)常會將某種尺寸的圖像轉(zhuǎn)換為其他尺寸的圖像,如放大或者縮小圖像。由于在縮放的過程中會遇到浮點數(shù),如何在FPGA中正確的處理浮點數(shù)運算是在FPGA中實現(xiàn)圖像縮放的關(guān)鍵。

2022-03-18 11:03:41 5929

5929 FPGA在常規(guī)運算時不能進(jìn)行浮點運算,只能進(jìn)行定點整型運算,在處理數(shù)據(jù)的小數(shù)乘加運算和除法運算時FPGA一般是無能為力的,其中一種常用的處理方法就是數(shù)據(jù)進(jìn)行浮點到定點的轉(zhuǎn)換。

2022-10-13 16:23:50 6173

6173 數(shù)據(jù)中心和超算需要高于1000 TOPS的高算力芯片。當(dāng)前,超算中心算力已經(jīng)進(jìn)入E級算力(百億億次運算每秒)時代,并正在向Z(千E)級算力發(fā)展。2022年5月登頂世界超算500強榜單的美國國防部橡樹

2022-12-09 11:29:59 4592

4592 我們使用的處理器一般情況下,要么直接支持硬件的 浮點運算 ,比如某些帶有FPU的器件,要么就只支持定點運算,此時對 浮點 數(shù)的處理需要通過編譯器來完成。在支持硬件浮點處理的器件上,對 浮點運算

2022-12-09 12:25:09 3815

3815 MLP全稱Machine Learning Processing單元,是由一組至多32個乘法器的陣列,以及一個加法樹、累加器、還有四舍五入rounding/飽和saturation/歸一化normalize功能塊。

2023-02-27 10:45:30 600

600 。Achronix為了解決這一大困境,創(chuàng)新地設(shè)計了機器學(xué)習(xí)處理器(MLP)單元,不僅支持浮點的乘加運算,還可以支持對多種定浮點數(shù)格式進(jìn)行拆分。 MLP全稱Machine Learning Processing單元

2023-03-11 13:05:07 1285

1285 據(jù)統(tǒng)計預(yù)測,全球算力需求呈現(xiàn)高速發(fā)展態(tài)勢。2021年,全球計算設(shè)備算力總規(guī)模達(dá)到615EFLOPS(每秒一百京次(=10^18)浮點運算);到2025年,全球算力規(guī)模將達(dá)6.8 ZFLOPS( 每秒

2023-05-22 09:36:28 1376

1376

算力網(wǎng)絡(luò)的發(fā)展需要技術(shù)的堅實支撐,這其中既有現(xiàn)有技術(shù)的加速創(chuàng)新,也有交叉技術(shù)的跨界創(chuàng)新,更有原創(chuàng)技術(shù)的引領(lǐng)創(chuàng)新。算力網(wǎng)絡(luò)為技術(shù)創(chuàng)新

提出了巨大需求和應(yīng)用空間,是技術(shù)創(chuàng)新的發(fā)展機遇,也是重大挑戰(zhàn)。

2023-05-23 17:18:49 0

0 算力網(wǎng)絡(luò)的發(fā)展需要技術(shù)的堅實支撐,這其中既有現(xiàn)有技術(shù)的加速創(chuàng)新,也有交叉技術(shù)的跨界創(chuàng)新,更有原創(chuàng)技術(shù)的引領(lǐng)創(chuàng)新。算力網(wǎng)絡(luò)為技術(shù)創(chuàng)新

提出了巨大需求和應(yīng)用空間,是技術(shù)創(chuàng)新的發(fā)展機遇,也是重大挑戰(zhàn)。

2023-05-24 16:31:46 0

0 工智能行業(yè)年度評選獎項,美格智能通過層層篩選,旗下高算力AI模組SNM970榮獲維科杯·OFweek2023物聯(lián)網(wǎng)行業(yè)創(chuàng)新技術(shù)產(chǎn)品獎——通信技術(shù)創(chuàng)新獎。本屆大會是202

2023-08-29 15:28:12 1310

1310

,浮點加法器是現(xiàn)代信號處理系統(tǒng)中最重要的部件之一。FPGA是當(dāng)前數(shù)字電路研究開發(fā)的一種重要實現(xiàn)形式,它與全定制ASIC電路相比,具有開發(fā)周期短、成本低等優(yōu)點。 但多數(shù)FPGA不支持浮點運算,這使FPGA在數(shù)值計算、數(shù)據(jù)分析和信號處理等方

2023-09-22 10:40:03 2116

2116

近日,中國移動通信集團(tuán)有限公司( 以下簡稱“中國移動”) 聯(lián)合華為圓滿完成 SPN(Slicing?Packet?Network ,切片分組網(wǎng))算力業(yè)務(wù)新技術(shù)創(chuàng)新試點工作。本次試點覆蓋算力接入和算力

2023-09-25 19:00:11 882

882

引言 LMS(最小均方)算法因其收斂速度快及算法實現(xiàn)簡單等特點在自適應(yīng)濾波器、自適應(yīng)天線陣技術(shù)等領(lǐng)域得到了十分廣泛的應(yīng)用。為了發(fā)揮算法的最佳性能,必須采用具有大動態(tài)范圍及運算精度的浮點運算,而浮點

2023-12-21 16:40:01 1590

1590 龐大的算力支持,用戶普遍需要向云計算廠商購買算力服務(wù);且由于大量用戶涌入云服務(wù)市場,云廠商需要盡快升級數(shù)據(jù)中心算力以應(yīng)對AI需求,同時持續(xù)降低TCO,為用戶提供價格合理的算力資源;此外,AI應(yīng)用開發(fā)還涉及大量隱私敏感數(shù)據(jù)的云端存儲和使用,云廠商也要

2023-12-29 14:32:23 786

786

支持硬件浮點運算單元(FPU),可以提供快速和高效的浮點運算性能。本文將詳細(xì)介紹 STM32F407 的浮點運算速度。 浮點運算是很多應(yīng)用中常用的一種運算類型,特別是對于需要進(jìn)行較復(fù)雜計算的任務(wù),如圖像處理、信號處理和物理模擬等。傳統(tǒng)的處理器對于浮點運算的支持有限,需要通過軟件庫實現(xiàn)

2024-01-04 10:58:34 5181

5181 隨著國家大力發(fā)展數(shù)字經(jīng)濟(jì),算力的提升和普惠變得越來越重要。在數(shù)字化時代,算力已成為推動科技發(fā)展和創(chuàng)新的關(guān)鍵要素。

2024-01-18 18:20:22 6204

6204

的?要想提高算力,都有哪些方法?一、算力的關(guān)鍵因素從算力的常見計量單位FPOPS(FloatingPointOperationsPerSecond,浮點運算次數(shù)/秒)、

2024-07-11 08:04:57 104

104

在信息時代,算力不僅是推動生產(chǎn)力發(fā)展的關(guān)鍵,更是一種稀缺而昂貴的資源。它從簡單的數(shù)學(xué)運算擴展到邏輯處理,再到現(xiàn)代多媒體信息的深度處理,其應(yīng)用范圍和需求不斷增長。香農(nóng)和圖靈的理論為電子計算機的誕生奠定

2024-08-27 14:30:24 665

665 九章云極DataCanvas公司技術(shù)專家向與會者詳細(xì)介紹算力包的產(chǎn)品能力和創(chuàng)新模式,收獲行業(yè)伙伴的高度認(rèn)可。算力作為AI時代的數(shù)字能源,將在行業(yè)應(yīng)用和技術(shù)創(chuàng)新互相驅(qū)動下,邁入“算力普惠”的終極生態(tài),AI應(yīng)用也將迎來爆發(fā)式的繁榮。

2024-09-29 14:44:17 1626

1626

由于定點的四則運算比較簡單,如加減法只要注意符號擴展,小數(shù)點對齊等問題即可。在本文中,運用在前一節(jié)中描述的自定義浮點格式FPGA中數(shù)的表示方法(下),完成浮點四則運算的實現(xiàn)過程 1.自定義浮點格式加

2024-11-16 11:19:23 2139

2139

由于定點的四則運算比較簡單,如加減法只要注意符號擴展,小數(shù)點對齊等問題即可。在本文中,運用在前一節(jié)中描述的自定義浮點格式FPGA中數(shù)的表示方法(下),完成浮點四則運算的實現(xiàn)過程 1.自定義浮點格式加

2024-11-16 12:51:57 1323

1323

本文系統(tǒng)地整理和解釋了算力領(lǐng)域中常用的數(shù)十個關(guān)鍵名詞,并按照以下維度進(jìn)行了分類:基礎(chǔ)概念、系統(tǒng)架構(gòu)、硬件架構(gòu)、基礎(chǔ)運算類型、計算模式、相關(guān)軟件架構(gòu)與部署模式、浮點精度格式、算力類型、算力關(guān)聯(lián)與服務(wù)

2025-04-07 11:21:03 1308

1308

NPU IP,通過架構(gòu)創(chuàng)新、軟硬件協(xié)同優(yōu)化與開放生態(tài)等,為應(yīng)對端側(cè)AI“算力墻”、“內(nèi)存墻”、“功耗墻”困境給出技術(shù)錦囊。 ? ? 錦囊一:應(yīng)對“算力墻”,從“定點”到“浮點”,架構(gòu)升級與算力靈活配置 端側(cè)AI從CNN向Transformer遷移,對高精度浮點運算的需求

2025-12-18 13:45:09 286

286

電子發(fā)燒友App

電子發(fā)燒友App

評論