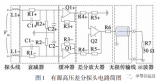

Anritsu(安立)公司的12端口矢量網(wǎng)絡(luò)分析儀(VNA)能夠?qū)ぷ髟?0~65GHz頻率范圍內(nèi)的單端信號、混合模式和差分器件進(jìn)行散射參數(shù)(S參數(shù))測試,非常適合高速器件和系統(tǒng)的信號完整性(SI)測量。

Anritsu的12端口65GHz系統(tǒng)由一個型號為37397D的雙端口VNA系統(tǒng)、一個外部測試裝置以及多個安置方便的端口模塊組成。這種移動測試端口可以緊靠任何形狀的被測設(shè)備(DUT)放置,從而使得該測量系統(tǒng)與晶圓探測系統(tǒng)一起使用時能發(fā)揮強(qiáng)大功能。適用于4、8和12端口應(yīng)用的測試系統(tǒng)校準(zhǔn)功能得到了PAF公司的一款靈活的校準(zhǔn)和測量軟件的支持。這個功能強(qiáng)大的軟件可以幫助操作人員應(yīng)對最困難的多端口測試,包括晶圓級測量。針對具有144個S參數(shù)的復(fù)雜測量,這個12端口VNA系統(tǒng)和軟件支持一個精確的78項(xiàng)錯誤模型,帶有至少有17條連接。

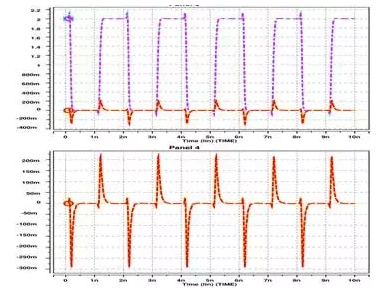

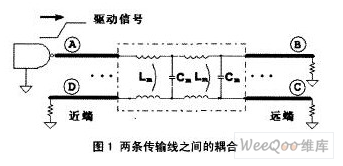

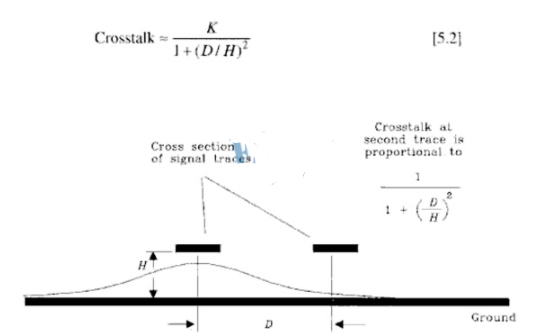

VNA傳統(tǒng)上常被用來對單端50Ω元器件進(jìn)行S參數(shù)測量,但隨著數(shù)字通信系統(tǒng)和總線速度、頻率的提高,多端口混合模式S參數(shù)已經(jīng)成為分析高速數(shù)字信號線、總線和器件信號完整性(SI)的有效工具。例如,VNA可以直接測量高速通道上的串?dāng)_。雖然高速背板中設(shè)計的通道相互之間是獨(dú)立的,但它們經(jīng)常受到高速/高頻信號通道之間串?dāng)_的影響。對于USB3.0或第3代PCI Express等速度已經(jīng)超過10Gbps的數(shù)字通信標(biāo)準(zhǔn)來說,12端口65GHz VNA測試系統(tǒng)可以在全速狀態(tài)下提供有意義的信號完整性測量,能為多通道同時測量提供必需的測量端口。

除了高速背板,越來越多的無線元器件和設(shè)備也采用差分(平衡的)架構(gòu)來減少電磁干擾(EMI)的影響。雖然4端口VNA系統(tǒng)可被用來測量單個差分通道或器件,但更復(fù)雜的元器件需要更多數(shù)量的測量端口。事實(shí)上,對高速傳輸線進(jìn)行單端測量可能產(chǎn)生性能降低的錯誤結(jié)果,因?yàn)檫@些傳輸線是針對差分信號來設(shè)計的。

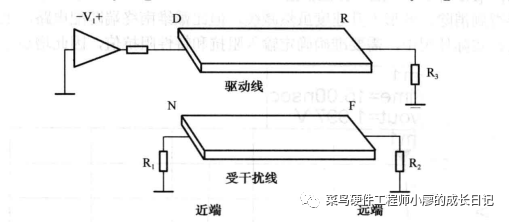

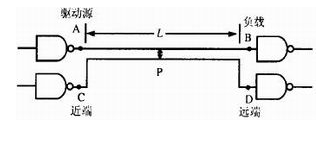

對高速背板而言,相鄰差分通道間的串?dāng)_會降低其性能。在一對差分通道中,產(chǎn)生串?dāng)_的那個通道被稱為干擾通道(干擾線),而耦合而受到串?dāng)_影響的相鄰?fù)ǖ辣环Q為被干擾通道(被干擾線)。為用VNA系統(tǒng)分析兩個差分通道的串?dāng)_,干擾線需要4個測試端口,被干擾線需要4個測試端口。當(dāng)然,在多通道通信系統(tǒng)或多組差分線中,一對相鄰線實(shí)際上與周邊其它線并非隔離。因此,分析兩個相鄰干擾線在被干擾線上造成的串?dāng)_通常更有實(shí)際意義。因?yàn)槊扛€需要4個測試端口,所以共需要12個測試端口。

構(gòu)建12端口VNA系統(tǒng)有好幾種架構(gòu)可供選擇。下面介紹的兩種架構(gòu)都以基本的雙端口VNA系統(tǒng)為基礎(chǔ),這種雙端口VNA系統(tǒng)通常采用一對采樣器,并且每個端口上都有一個雙向耦合器,以測量這些端口上的突發(fā)事件和反射信號。在第一種設(shè)計中,通過為每個額外測試端口增加一對采樣器和相關(guān)的高頻硬件來增加端口數(shù)量。這種方法雖然比較簡捷,但會大大增加測試系統(tǒng)的復(fù)雜性和成本。在第二種方法中,為從雙端口系統(tǒng)為起點(diǎn)創(chuàng)建具有更多端口的VNA系統(tǒng),需要在雙端口VNA中增加開關(guān)矩陣,以便將信號路由到原始的測試端口。雖然這種方法對開關(guān)矩陣的性能又很高要求,但與第一種方法相比復(fù)雜性較低,成本也更低。Intel公司的研究表明,當(dāng)采用正確的校準(zhǔn)技術(shù)時,基于這種系統(tǒng)架構(gòu)的多采樣器測試系統(tǒng)具有相當(dāng)高的精度。

?

圖1:12端口VNA系統(tǒng)能對40~65GHz頻率范圍內(nèi)的混合模式和差分器件進(jìn)行S參數(shù)測量。

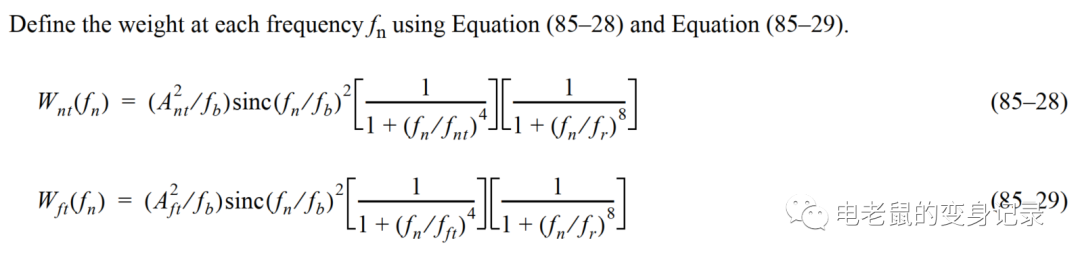

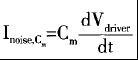

Anritsu(安立)公司的12端口65GHz系統(tǒng)(圖1)基于4端口測量引擎,這個4端口測量引擎采用毫米波頻率的開關(guān)矩陣將信號從遠(yuǎn)程端口模塊路由到4個測試端口,從而增加了測量端口的有效數(shù)量。由Anritsu公司設(shè)計生產(chǎn)的上述開關(guān)矩陣采用了低損耗的65GHz寬帶開關(guān)(圖2)。

?

開關(guān)元件的選擇包括電子機(jī)械開關(guān)和固態(tài)(PIN二極管)開關(guān)。電子機(jī)械開關(guān)具有帶寬高、插損低和隔離度高的優(yōu)點(diǎn),但與固態(tài)開關(guān)相比,它們的運(yùn)動部件導(dǎo)致元件的平均無故障時間(MTBF)較短,并且性能可重復(fù)性也較低。PIN二極管支持?jǐn)?shù)百萬的開關(guān)次數(shù),具有卓越的可靠性,但缺少機(jī)械開關(guān)突出的射頻/微波性能。為克服固態(tài)開關(guān)的電氣缺陷,特別是在毫米波頻率下?現(xiàn)的缺點(diǎn),Anritsu開發(fā)出了一種創(chuàng)新設(shè)計,該設(shè)計充分整合了機(jī)械開關(guān)的電氣性能和固態(tài)開關(guān)經(jīng)過驗(yàn)證的MTBF可靠性。整個開關(guān)矩陣具有大于95dB的隔離度,在60GHz時的插入損耗低于6dB。在移動測試端口內(nèi)靠近DUT放置高性能耦合器有助于優(yōu)化原始的定向性。

采用開關(guān)矩陣多端口NVA架構(gòu)還能為校準(zhǔn)提供全面的靈活性。12端口65GHz VNA系統(tǒng)包含一個型號為37000D的VNA、帶多個SM6272測試端口模塊的開關(guān)矩陣的測試裝置,以及校準(zhǔn)與測量軟件。SM6272外部測試端口模塊(圖3)采用固態(tài)開關(guān)和高性能定向性耦合器,在65GHz頻率以下可以提供很高的精度和可重復(fù)性。它們的外形也非常緊湊,只有4.5x5.0x7.0英寸,因而非常便于靠近DUT擺放。這些模塊可以被增加到基本系統(tǒng)中,形成一個具有更多端口數(shù)量的測試解決方案(比如從4端口系統(tǒng)升級到8端口系統(tǒng))。

?

不管VNA系統(tǒng)是一個簡單的雙端口系統(tǒng)還是一個較復(fù)雜的12端口VNA,為獲得較高的測量精度,必須仔細(xì)選擇和謹(jǐn)慎執(zhí)行校準(zhǔn)過程。校準(zhǔn)的目的是去除或減掉測試夾具、電纜和用于從被測設(shè)備(DUT)收發(fā)信號的其它元件引起的電氣貢獻(xiàn)值。通過盡量縮短測試電纜的長度(就如Anritsu的12端口VNA系統(tǒng)一樣)并采用高性能測試元件,系統(tǒng)能獲得很好的原始定向性。一個有效的校準(zhǔn)過程會使用明確規(guī)定的電氣標(biāo)準(zhǔn)來表征測試系統(tǒng)的性能,因此理想的DUT測量應(yīng)該只是測試DUT的電氣性能,不包括測試系統(tǒng)、夾具、探針或其它測試附件。

一個有效的校準(zhǔn)過程必須從測試夾具、探針以及將信號路由至DUT的其它硬件那里收集到足夠的數(shù)據(jù),以確定內(nèi)部時延、失配、連接和開關(guān)損耗效應(yīng),并從DUT測量結(jié)果中刨除這些效應(yīng)。目前的VNA測試系統(tǒng)采用廣泛的校準(zhǔn)過程,包括短路-開路-負(fù)載-直通(SOLT)和直通-反射-匹配(TRM)方法。校準(zhǔn)技術(shù)的選擇通常是DUT類型及實(shí)際標(biāo)準(zhǔn)可用性的函數(shù)。每種校準(zhǔn)方法都試圖從在DUT上取得的原始測量數(shù)據(jù)中去除錯誤項(xiàng)。隨著VNA系統(tǒng)端口數(shù)量的增加,錯誤項(xiàng)的數(shù)量也越來越多。

?

這些已制定的VNA校準(zhǔn)方法是專為傳統(tǒng)的多采樣器/定向性耦合器VNA架構(gòu)而開發(fā),不適合采用開關(guān)矩陣的多端口VNA測試系統(tǒng)(如Anritsu的12端口65GHz系統(tǒng))。因此,Anritsu與PAF公司共同為12端口系統(tǒng)開發(fā)了實(shí)用的測量與校準(zhǔn)軟件。PAF是一家以開發(fā)多端口VNA校準(zhǔn)算法而著名的公司,致力于為20GHz以下的多端口VNA測量與校準(zhǔn)提供商用化軟件產(chǎn)品。Anritsu要求這種工具精確地擴(kuò)展到65GHz。

該軟件縮短了校準(zhǔn)和測試時間,并提供很大的靈活性,因?yàn)?2端口VNA測量系統(tǒng)可被用于帶夾具裝置的同軸測量和晶圓級測量。系統(tǒng)的分離型硬件架構(gòu),以及可以靠近DUT測試夾具放置或直接擺放在晶圓探針臺上的端口模塊,都需要一定程度的校準(zhǔn)靈活性以支持多種測試應(yīng)用。這種靈活性對12端口晶圓測試應(yīng)用來說尤其關(guān)鍵,因?yàn)槠淇捎玫倪B接和校準(zhǔn)標(biāo)準(zhǔn)數(shù)量非常有限。

為Anritsu的12端口65GHz VNA開發(fā)的校準(zhǔn)過程能根據(jù)連接的最小數(shù)量動態(tài)計算標(biāo)準(zhǔn)連接順序,并同時提供最高可能達(dá)到的精度。PAF公司提供的MMS-NT校準(zhǔn)和測試軟件(圖4)支持許多校準(zhǔn)過程,包括SOLT、TRL、線路-反射-匹配(LRM)、線路-反射線(LRL)、短路-開路-負(fù)載-互易直通(SOLR)、快速SOLT(QSOLT)甚至半泄漏校準(zhǔn)。

根據(jù)新系統(tǒng)的測試端口數(shù)量以及校準(zhǔn)中的可能連接數(shù)量,盡量縮短校準(zhǔn)和測試時間對新的校準(zhǔn)軟件來說非常重要。MMS-NT軟件允許在兩個相對的端口之間,用單個12項(xiàng)校準(zhǔn)完成12端口VNA系統(tǒng)的校準(zhǔn),對TRL校準(zhǔn)而言這要用到6條連接。然后,在每個原始端口和對面的5個端口之間全面測量5次,這樣做僅增加11條連接。這個過程很容易在半自動晶圓上系統(tǒng)中實(shí)現(xiàn)。即使在同軸測試環(huán)境中,17條連接校準(zhǔn)仍可以在不到20分鐘的時間內(nèi)完成。

實(shí)質(zhì)上,MMS-NT校準(zhǔn)軟件適合獨(dú)特的測試端口配置,能以最少的連接提供最高的精度。MMS-NT軟件還能提供豐富的測量與顯示功能,支持12端口差分參數(shù)、時域反射儀(TDR)測量、眼圖顯示,可以將數(shù)據(jù)導(dǎo)出到Excel電子表格生成報表,或轉(zhuǎn)換成Touchstone文件格式供軟件仿真工具使用。

校準(zhǔn)軟件包含可以自動計算和管理多端口測量系統(tǒng)的誤差系數(shù)的內(nèi)部算法和數(shù)據(jù)結(jié)構(gòu)。一旦定義好多端口連接方式,軟件就能為所有已定義的端口的校準(zhǔn)確定最優(yōu)最有效的連接方案。該軟件能自動定義系統(tǒng)端口和連接器結(jié)構(gòu)、描述正確的校準(zhǔn)標(biāo)準(zhǔn)集、優(yōu)化校準(zhǔn)標(biāo)準(zhǔn)連接的序列、減少所需連接的數(shù)量、計算誤差系數(shù)并修正測量數(shù)據(jù)。

這個12端口VNA系統(tǒng)采用緊湊的SM6272測試端口模塊,由于能將測試端口盡可能靠近DUT放置,所以非常適合進(jìn)行晶圓級測試。開關(guān)和所有射頻信號路由表都位于每個模塊內(nèi)和測試端口定向性耦合器的后面,具有最小的插入損耗和最優(yōu)的測量穩(wěn)定性。每個測試端口模塊包含兩個帶堅固的公頭V型連接器的測試端口。MMS-NT軟件可以將測量連接方式自動轉(zhuǎn)換成包括外部測試夾具補(bǔ)償在內(nèi)的最佳多端口校準(zhǔn)方案。

電子發(fā)燒友App

電子發(fā)燒友App

評論