本章的實驗任務是在 PL 端自定義一個 AXI4 接口的 IP 核,通過 AXI_HP 接口對 PS 端 DDR3 進行讀寫測試,讀寫的內存大小是 4K 字節。

2025-11-24 09:19:42 3470

3470

添加Zynq Processing System IP核,配置DDR控制器和時鐘。7000系列的Zynq可以參考正點原子DMA回環測試設置。

2025-11-24 09:25:50 2883

2883

JEDEC 固態技術協會,微電子產業標準全球領導制定機構,今天宣布正式發布JEDEC DDR3L規范。這是廣受期待的DDR3存儲器標準JESD79-3 的附件。這是DDR3作為當今DRAM主導性標準演變的繼續

2010-08-05 09:10:50 4186

4186 本白皮書討論各種存儲器接口控制器設計所面臨的挑戰和 Xilinx 的解決方案,同時也說明如何使用 Xilinx軟件工具和經過硬件驗證的參考設計來為您自己的應用(從低成本的 DDR SD

2010-08-18 10:50:37 3738

3738

DDR3只有一組控制、地址和數據總線,因此同一時刻只能有一個設備在訪問。##幀地址控制模塊主要是將DDR3空間進行劃分,同時控制幀地址的切換。

2015-04-07 15:52:10 13985

13985

廉價的雙倍數據速率(DDR)內存(以及DDR2和DDR3等后來的版本)為臺式機和筆記本電腦的工作內存提供了支柱。通過在脈沖序列的前沿和后沿上為存儲器提供時鐘,存儲器吞吐量加倍,而功耗僅略微增加。

2019-03-25 08:48:00 5374

5374

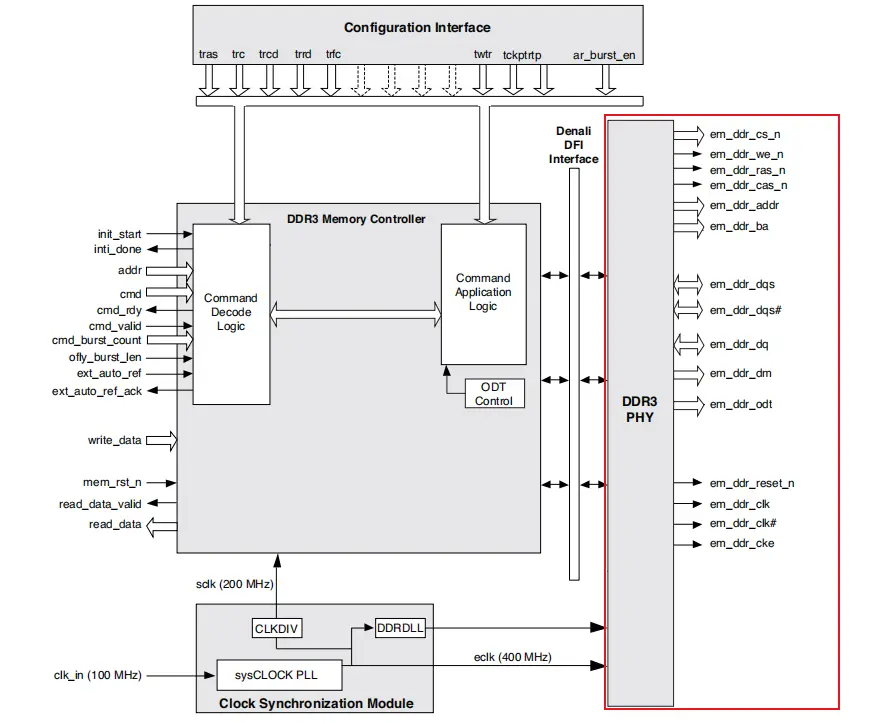

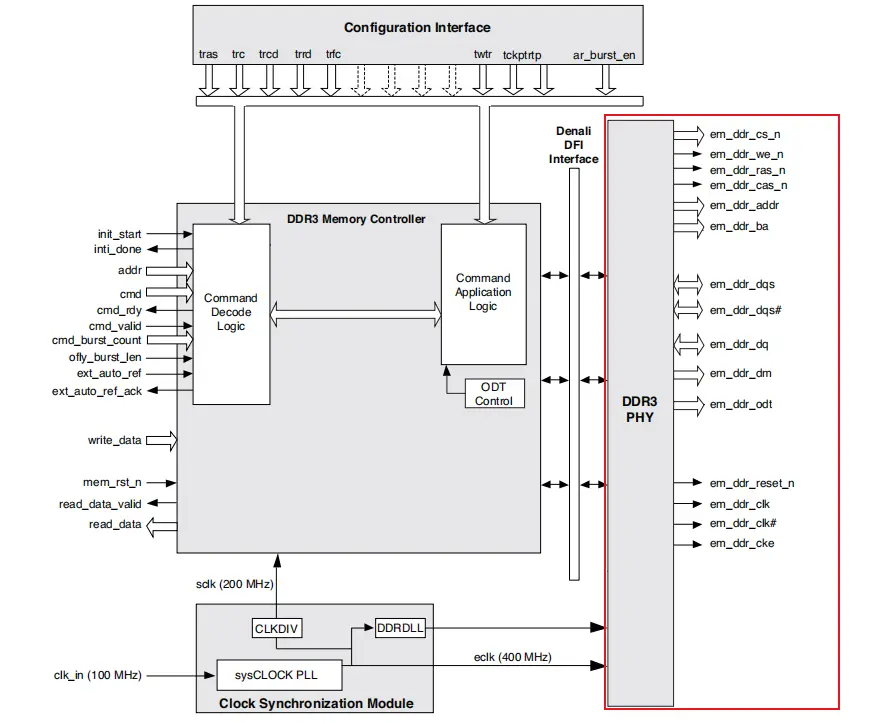

1. 背景 這篇文章主要介紹了DDR3IP核的寫實現。 2. 寫命令和數據總線介紹 DDR3 SDRAM控制器IP核主要預留了兩組總線,一組可以直接綁定到DDR3 SDRAM芯片端口,一組是留給

2020-12-31 11:17:02 6783

6783

本實驗為后續使用DDR3內存的實驗做鋪墊,通過循環讀寫DDR3內存,了解其工作原理和DDR3控制器的寫法,由于DDR3控制復雜,控制器的編寫難度高,這里筆者介紹采用第三方的DDR3 IP控制器情況下的應用,是后續音頻、視頻等需要用到DDR3實驗的基礎。

2021-02-05 13:27:00 10988

10988

的SDRAMs其結果如圖6所說,63位,N=3。圖6 地址映射例子2.5. DDR3內存控制器接口為了使得數據能夠有效的將數據源從DSP搬運外部DDR3 SDRAM中,DDR3內存控制器使用了一個命令

2018-01-18 22:04:33

使用microblaze處理器。我必須通過DDR3內存發送一些固定值,如8位數據(X'FF'),即我將該數據寫入Genesys2 DDR3內存并從內存中讀出數據。我已經通過Xilinx網絡設備視頻手冊

2019-05-05 15:29:38

。為了充分利用和發揮DDR3存儲器的優點,使用一個高效且易于使用的DDR3存儲器接口控制器是非常重要的。視屏處理應用就是一個很好的示例,說明了DDR3存儲器系統的主要需求以及在類似數據流處理系統中

2019-05-24 05:00:34

DDR3存儲器接口控制器是什么?有什么優勢?

2021-04-30 06:57:16

本貼資料整理于《例說FPGA 可直接用于工程項目的第一手經驗》1.1功能概述:對FPGA提供的DDR2控制器IP核模塊進行讀寫操作。每1.78秒執行一次寫入和讀出操作。先從0地址開始遍歷寫256

2017-02-15 20:31:49

能為高時,對讀寫存儲空間進行乒乓操作,保證讀寫的存儲不會在同一個空間,反之,就不進行乒乓操作,使讀寫的存儲在同一個空間。

具體的頂層調用如上面所述,同時,在數據處理方面要注意:輸入DDR3頂層模塊的數據和DDR3頂層模塊輸出的數據都為16bit,而MIG的數據位寬為128bit,需要進行數據處理。

2025-10-24 06:53:17

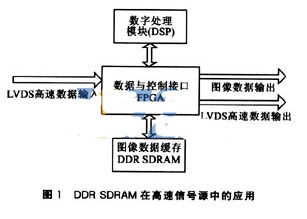

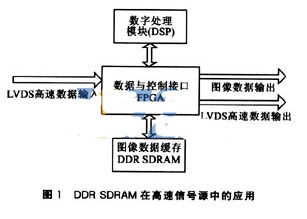

核心,以WinCE為軟件平臺,能實時、連續地采集清晰的視頻數據。1 系統結構框圖及視頻數據采集原理視頻數據采集系統結構如圖1所示。從圖1中可以看出。系統由嵌入式微處理器S3C2440、存儲器(包括

2019-08-06 08:30:15

? ALTMEMPHY宏功能來構建所有的 DDR2或者 DDR SDRAM外部存儲器。通過將 Altera DDR2 或者 DDR SDRAM 存儲控制器、第三方控制器或者定制控制器用于特定的應用需要,可以實現控制器功能

2017-11-14 10:12:11

(flight-time skew)來降低共同切換噪聲(SSN)。走線擺率可以達到0.8tCK,這個寬度導致無法確定在哪兩個時鐘周期獲取數據,因此,JEDEC為DDR3定義了校準功能,它可以使控制器

2019-04-22 07:00:08

=1.5V;但我看了一篇FPGA的DDR3 IP核例化文章,上面寫FPGA的BANK1,3連接外部存儲控制器(如下圖,且只有四個BANK),所以要將DDR3連接在BANK3上。所以DDR3如何與FPGA芯片

2021-11-29 16:10:48

DDR3讀寫控制器主要用于生成片外存儲器DDR3 SDRAM進行讀寫操作所需要的時序,繼而實現對片外存儲器的讀寫訪問。由攝像頭采集得到的圖像數據通常數據量較大,使用片內存儲資源難以實現大量圖像數據

2025-10-21 10:40:28

傳輸給AT91RM9200;在AT91RM9200上,Lnux驅動實現存儲器映射I/O和物理內存重映射,避免了視頻數據在應用程序與內核之間的二次拷貝,提高了應用程序的網絡發包效率。 1 HPI接口硬件

2018-11-26 11:12:49

的等待時間。 共享存儲器效率 —— 為進一步提高共享存儲器的執行效率,在 CorePac 內置了擴展存儲器控制器 (XMC)。對共享內部存儲器 (SL2/SL3) 和外部存儲器 (DDR3 SRAM

2011-08-13 15:45:42

管理,具有高帶寬、高性能特性,適合于嵌入式處理器與高性能外圍設備、片內存儲器及接口功能單元的連接。 根據兩種總線的特點和廣泛支持,為了給嵌入式SoC系統提供USB接口,需要設計USB和AHB間的橋接IP核

2019-05-13 07:00:04

MIG IP控制器是Xilinx為用戶提供的一個用于DDR控制的IP核,方便用戶在即使不了解DDR的控制和讀寫時序的情況下,也能通過MIG IP控制器讀寫DDR存儲器。一、新建工程在Vivado環境

2019-12-19 14:36:01

RASn,CASn等,是IP核自動產生的么?要如何配置條件,給DDR3寫入數據并讀取DDR3的數據,謝謝,現在頭緒不清,第一次做,拜托各位解惑了

2016-01-14 18:15:19

& 14用于DDR3內存接口,但由于我使用的是3.3V的fash存儲器IC,我必須使用bank 14進行閃存存儲器接口。原因是需要的資源僅在Bank 14中可用.DDR3存儲器連接的bank應該工作在

2020-04-17 07:54:29

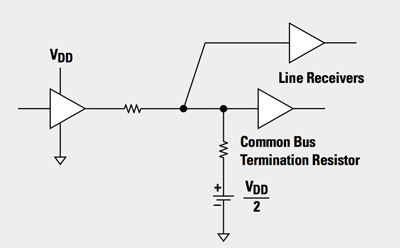

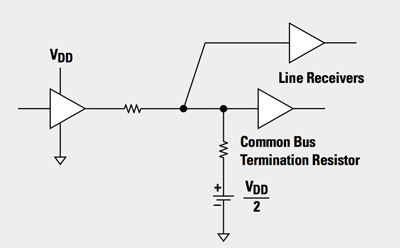

。具有短的線跡長度、最多兩個 DDR3 器件和平衡的 T 拓撲是必須滿足的要求;否則,應遵循 VTT 終端指南。特性在具有集成式 DDR 控制器的 Sitara AM437x 處理器上采用系統優化

2015-04-03 17:14:40

。具有短的線跡長度、最多兩個 DDR3 器件和平衡的 T 拓撲是必須滿足的要求;否則,應遵循 VTT 終端指南。主要特色在具有集成式 DDR 控制器的 Sitara AM437x 處理器上采用系統優化

2018-09-26 08:53:27

FPGA外部的DDR2芯片,它與DDR2 IP核的接口通常命名為“mem_*”。● DDR2 IP核內部分兩個部分,即圖示的“ALTMEMPHY”和“存儲控制器(Memory Controller

2016-10-27 16:36:58

。為了充分利用和發揮DDR3存儲器的優點,使用一個高效且易于使用的DDR3存儲器接口控制器是非常重要的。視屏處理應用就是一個很好的示例,說明了DDR3存儲器系統的主要需求以及在類似數據流處理系統中

2019-05-27 05:00:02

IP DDR3控制器 RISC-V

基于DDR200T開發板原理圖,找到所需要使用的DDR引腳,制成DDR.ucf文件方便在添加管腳約束時使用。在使用MIG IP核時,為了方便使用DDR產生的時鐘

2025-10-21 12:43:40

進行了DDR3 SDRAM控制器的編寫,分析并提出了提高帶寬利用率的方法。最終將其進行類FIFO接口的封裝,屏蔽掉了DDR3 IP核復雜的用戶接口,為DDR3數據流緩存的實現提供便利。系統測試表明,該

2018-08-02 09:34:58

,根據不同操作完成對應接口的時序控制[7],進而實現對DDR3的正確讀寫訪問。2 DDR3存儲器控制模塊設計DDR3 IP核生成的控制器邏輯框圖如圖2所示,采用UI接口的方式相比于AXI4接口,不需要自己

2018-08-02 09:32:45

的沖突。幀地址控制模塊控制幀地址的切換。為了提高并行處理的速度,簡化數據讀寫沖突,將圖形數據和視頻數據分別存儲在不同的DDR3中。2DDR3存儲器控制模塊設計MIG生成的DDR3控制器的邏輯框圖[5

2018-08-02 11:23:24

問題。幀地址控制模塊控制幀地址的切換。為了提高并行處理的速度,減少數據讀寫沖突,將圖形數據和視頻數據分別存儲在不同的DDR3中。

DDR3存儲器控制模塊設計

MIG生成的DDR3控制器的邏輯框圖

2024-06-26 18:13:42

12位,擴展成16位后進行存儲,DDR3內部以1067M處理速度,32位的處理帶寬進行存儲,寫數據時從地址全0寫到地址全1,讀數據時也從地址全0讀到全1,經對比無誤,說明該控制器能夠較好地進行高速讀寫操作。`

2018-08-30 09:59:01

DDR控制協議

DDR3讀寫控制器主要用于生成片外存儲器DDR3 SDRAM進行讀寫操作所需要的時序,繼而實現對片外存儲器的讀寫訪問。由攝像頭采集得到的圖像數據通常數據量較大,使用片內存儲資源

2025-10-21 14:30:16

選擇。視頻處理和圖形生成需要存儲海量數據,FPGA內部的存儲資源無法滿足存儲需求,因此需要配置外部存儲器。與DDR2 SDRAM相比,DDR3 SDRAM帶寬更好高、傳輸速率更快且更省電,能夠滿足

2019-06-24 06:07:53

如圖1所示由視頻A/D采集的原始視頻數據,在Philips公司生產的TM1300專用視頻處理器中壓縮后,通過USB控制器送至PC機。PC機的整個通過USB控制器傳輸到TM1300,解壓后發送至視頻D

2021-06-29 07:30:00

的片上系統。針對本設計中觸控屏幀緩存讀操作的特點,選擇以Avalon 主端口接口的形式對模塊進行開發,大大提高了處理器運行效率,同時實現了觸控屏控制器IP 核的參數化設計, 提高了控制器對于不同LCD

2018-11-07 15:59:27

DDR3存儲器控制器面臨的挑戰有哪些?如何用一個特定的FPGA系列LatticeECP3實現DDR3存儲器控制器。

2021-04-30 07:26:55

現在因為項目需要,要用DDR3來實現一個4入4出的vedio frame buffer。因為片子使用的是lattice的,參考設計什么的非常少。需要自己調用DDR3控制器來實現這個vedio

2015-08-27 14:47:57

,以及對應的波形圖和 Verilog HDL 實現。我們調取的 DDR3 SDRAM 控制器給用戶端預留了接口,我們可以通過這些預留的接口總線實現對該 IP 核的控制,本章節將會講解如何根據

2022-02-08 07:08:01

的工作時鐘頻率。然而,設計至DDR3的接口也變得更具挑戰性。在FPGA中實現高速、高效率的DDR3控制器是一項艱巨的任務。直到最近,只有少數高端(昂貴)的FPGA有支持與高速的DDR3存儲器可靠接口的塊

2019-08-09 07:42:01

vc707)上進行了仿真和實現。它的簡單CPU有:2個端口(指令地址和指令數據)3個端口(mem地址,mem數據輸入,mem dataout),...但現在我想使用SRAM DDR3作為主存儲器

2020-08-25 13:19:36

你好我們計劃使用XC7Z020 PS部分的DDR3內置控制器將其連接到2個芯片[MT41K128M16] -32位數據寬度。我們計劃再使用一個DDR3組件來支持ECC。請告知我們XC7Z020 PS中DDR3控制器引腳的詳細信息,包括ECC引腳詳細信息。謝謝Pench

2020-03-24 09:34:32

產品,其它產品也將陸續推出。憑借其創新的架構和強大的功能,SPEAr1310以最先進的技術引領嵌入式市場,實現前所未有的成本競爭力、性能以及靈活性。”內置DDR2/DDR3內存控制器和完整的外設接口

2018-12-12 10:20:29

目前有一個項目需要使用DDR3作為顯示緩存,VGA作為顯示器,FPGA作為主控器,來刷圖片到VGA上。VGA部分已經完成,唯獨這個DDR3以前沒有使用過,時序又比較復雜,所以短時間內難以完成,希望做過DDR3控制器的大神指點一二。急求!!!!

2015-11-16 09:18:59

DDR3讀寫控制器主要用于生成片外存儲器DDR3 SDRAM進行讀寫操作所需要的時序,繼而實現對片外存儲器的讀寫訪問。由攝像頭采集得到的圖像數據通常數據量較大,使用片內存儲資源難以實現大量圖像數據

2025-10-21 08:43:39

數據速率 800Mbps

一、實驗要求

生成 DDR3 IP 官方例程,實現 DDR3 的讀寫控制,了解其工作原理和用戶接口。

二、DDR3 控制器簡介

GL50H 為用戶提供一套完整的 DDR

2023-05-19 14:28:45

一、實驗要求

生成 DDR3 IP 官方例程,實現 DDR3 的讀寫控制,了解其工作原理和用戶接口。

二、DDR3 控制器簡介

PGL50H 為用戶提供一套完整的 DDR memory 控制器

2023-05-31 17:45:39

一個基于Avalon總線接口的UPFC控制器IP核,以便于和NiosII組成一個完整的控制系統。1 UPFC控制器IP的主要功能UPFC控制器的IP主要用來輸出3路相位分別相差2π/3的正弦波形數據

2019-06-03 05:00:05

本文介紹了DDR3 SDRAM 的基本特點和主要操作時序,給出了一種基于ALTMEMPHY宏功能的DDR3 SDRAM控制器的設計方法。詳述了控制器基本結構和設計思想,分析了各模塊功能與設計注意事項,并

2010-07-30 17:13:55 30

30 用中檔FPGA實現高速DDR3存儲器控制器

引言

由于系統帶寬不斷的增加,因此針對更高的速度和性能,設計人員對存儲技術進行了優化。下一代雙數據速率(D

2010-01-27 11:25:19 1217

1217

MAX17000A脈寬調制(PWM)控制器為筆記本電腦的DDR、DDR2、DDR3存儲器提供完整的電源方案。該器件集成了一路降壓控制器、一路可

2010-11-25 09:26:24 909

909

使用功能強大的FPGA來實現一種DDR2 SDRAM存儲器的用戶接口。該用戶接口是基于XILINX公司出產的DDR2 SDRAM的存儲控制器,由于該公司出產的這種存儲控制器具有很高的效率,使用也很廣泛,

2013-01-08 18:15:50 239

239 凌華科技推出的首款高性能四核3U PXI嵌入式控制器PXI-3980,搭載高性能Intel Corei7四核處理器,支持最大DDR3內存容量16GB,非常適合高速數據處理與分析測量測試應用需求。

2013-06-17 14:58:39 1292

1292 基于協議控制器的DDR3訪存控制器的設計及優化_陳勝剛

2017-01-07 19:00:39 16

16 為解決超高速采集系統中的數據緩存問題,文中基于Xilinx Kintex-7 FPGA MIG_v1.9 IP核進行了DDR3 SDRAM控制器的編寫,分析并提出了提高帶寬利用率的方法。最終將其進行

2017-11-16 14:36:41 25161

25161

控制器用戶接口設計方案。該控制器用戶接口已經在Xilinx 公司的VC707 開發板上通過了功能驗證,并成功的被應用到高速圖像數據采集系統中。

2017-11-17 14:14:02 4072

4072

本文詳細介紹了在Xilinx Virtex-6系列FPGA中使用MIG3.7 IP核實現高速率DDR3芯片控制的設計思想和設計方案。針對高速實時數字信號處理中大容量采樣數據通過DDR3存儲和讀取

2017-11-17 14:26:43 26092

26092

Virtex - 6 系列 FPGA 中實現 DDR3 SDRAM控制器的設計方法, 并進行硬件測試。 驗證了 DDS3 控制器的可行性, 其工作穩定、 占用資源少、 可植性強等。 DDR3 SDRAM 是從 DDR、 DDR2 發展而來的一種高速同步動態隨機訪問存儲器。

2017-11-18 06:58:34 31634

31634

為了解決視頻圖形顯示系統中多個端口訪問DDR3的數據存儲沖突,設計并實現了基于FPGA的DDR3存儲管理系統。DDR3存儲器控制模塊使用MIG生成DDR3控制器,只需通過用戶接口信號就能完成DDR3

2017-11-18 18:51:25 7989

7989

對DDR2控制器的IP核進行了模塊化的劃分,分析了每個模塊的功能。強調了用戶接口功能的完善,并介紹了IP核的操作流程,使每個用戶都能輕松的使用該IP核。

2017-11-22 07:20:50 5930

5930

針對采用DDR3接口來設計的新一代閃存固態盤(SSD)需要完成與內存控制器進行通信與交互的特點,提出了基于現場可編程門陣列( FPGA)的DDR3協議解析邏輯方案。首先,介紹了DDR3內存工作原理

2017-12-05 09:34:44 10

10 DR3 在高頻時數據出現了交錯,因此,高速DDR3存儲器設計有一定的難度。如果FPGA I/O 結構中沒有直接內置調平功能,那么連接DDR3 SDRAM DIMM的成本會非常高,而且耗時,并且需要

2018-06-22 02:04:00 4421

4421 大家好,我叫Paul Evans,是Stratix III產品營銷經理。到目前為止,我已經從事了6年的雙倍數據速率存儲器工作,今天和大家一起討論一下DDR3。DDR3的主要難題之一是它引入了數據交錯

2018-06-22 05:00:00 9489

9489 SDRAM成為首選方法。但由于DDR3只有一套數據訪問通道,不能滿足多個通道同時訪問的需求。此前的對于SDRAM的多通道解決方案中,比如曹一江等設計的基于NPI總線的片外存儲器,最大帶寬可達743 Mb/s

2018-08-01 15:25:11 3972

3972

,因此能夠很好地滿足上述場合對大量數據緩存的需求。但DDR SDRAM的接口不能直接與現今的微處理器和DSP的存儲器接口相連,需要在其間插入控制器實現微處理器或DSP對存儲器的控制。

2019-07-02 08:03:00 5010

5010

使用中速Kintex-7 325T FPGA演示DDR3控制器和接口,運行速度高于1866 Mbps數據速率。

2018-11-30 06:21:00 6366

6366

這展示了DDR3內存的Kintex-7 FPGA接口功能。

2018-11-30 06:23:00 7144

7144 DDR3內存與DDR2內存相似包含控制器和存儲器2個部分,都采用源同步時序,即選通信號(時鐘)不是獨立的時鐘源發送,而是由驅動芯片發送。它比DR2有更高的數據傳輸率,最高可達1866Mbps;DDR3還采用8位預取技術,明顯提高了存儲帶寬;其工作電壓為1.5V,保證相同頻率下功耗更低。

2019-06-25 15:49:23 2336

2336 學完SDRAM控制器后,可以感受到SDRAM的控制器的書寫是十分麻煩的,因此在xilinx一些FPGA芯片內已經集成了相應的IP核來控制這些SDRAM,所以熟悉此類IP核的調取和使用是非常必要的。下面我們以A7的DDR3 IP核作為例子進行IP核調取。

2019-11-10 10:28:45 5993

5993

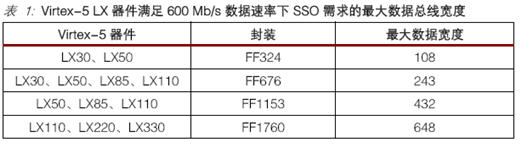

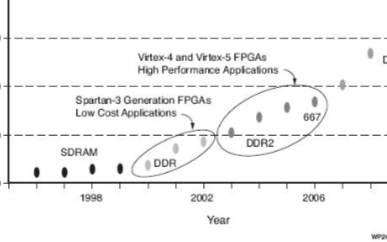

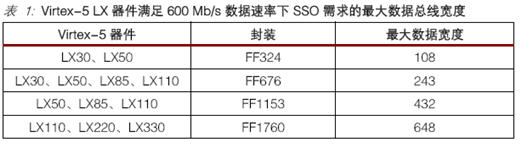

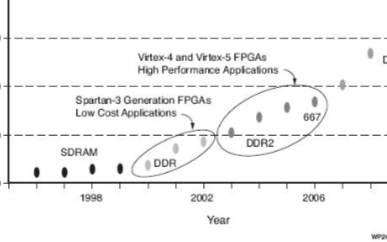

20 世紀 90 年代后期,存儲器接口從單倍數據速率 (SDR) SDRAM 發展到了雙倍數據速率 (DDR) SDRAM,而今天的 DDR2 SDRAM 運行速率已經達到每引腳 667 Mb/s或

2020-04-12 10:57:53 1552

1552

DDR對于做項目來說,是必不可少的。一般用于數據緩存和平滑帶寬。今天介紹下Xilinx DDR控制器MIG IP核的例化及仿真。 FPGA芯片:XC7K325T(KC705) 開發工具:Vivado

2020-11-26 15:02:11 10427

10427

EMD3D256M08/16B 256Mb DDR3自旋轉移扭矩MRAM(STT-MRAM)是非易失性存儲器,在DDR3速度下具有非揮發性和高耐久性。該設備能夠以高達1333MT /秒/引腳的速率

2021-03-19 16:23:30 1003

1003 15V、雙通道 3A 單片同步降壓型穩壓器為 DDR1、DDR2 或 DDR3 存儲器供電

2021-03-20 15:29:10 6

6 參考資料 《pg150-ultrascale-memory-ip》 以該手冊的脈絡為主線,對DDR3/4控制器進行探討。 1.IP核結構 根據官方提供的資料,IP核主要劃分為三個部分,分別是用戶接口

2021-09-22 10:28:24 3487

3487

,以及對應的波形圖和 Verilog HDL 實現。我們調取的 DDR3 SDRAM 控制器給用戶端預留了接口,我們可以通過這些預留的接口總線實現對該 IP 核的控制,本章節將會講解如何根據 Xilinx 官方提供的技術參數來實現對 IP 核的寫控制。寫命令和寫數據總線介紹DDR3 SDRAM控制器I

2021-12-04 19:21:05 4

4 車載視頻拼接的項目,該項目使用到了LVDS高速接口和DDR3接口,攝像頭采集的視頻圖像數據需要先存入DDR3中然后與通過LVDS傳輸的主機視頻數據進行拼接輸出,最終在屏幕上顯示畫中畫的效果。分享給大家

2022-03-14 14:46:06 1212

1212

本文以一個案例的形式來介紹lattice DDR3 IP核的生成及調用過程,同時介紹各個接口信號的功能作用

2022-03-16 14:14:19 2713

2713

一、DDR3簡介 ? ? ? ? DDR3全稱double-data-rate 3 synchronous dynamic RAM,即第三代雙倍速率同步動態隨機存儲器。所謂同步,是指DDR3數據

2022-12-21 18:30:05 5150

5150 視頻圖形顯示系統理想的架構選擇。視頻處理和圖形生成需要存儲海量數據,FPGA內部的存儲資源無法滿足存儲需求,因此需要配置外部存儲器。 ??? 與DDR2 SDRAM相比,DDR3 SDRAM帶寬更好高、傳輸速率更快且更省電,能夠滿足吞吐量大、功耗低的需求,因此

2023-06-08 03:35:01 2792

2792 本文開源一個FPGA項目:基于AXI總線的DDR3讀寫。之前的一篇文章介紹了DDR3簡單用戶接口的讀寫方式:《DDR3讀寫測試》,如果在某些項目中,我們需要把DDR掛載到AXI總線上,那就要通過MIG IP核提供的AXI接口來讀寫DDR。

2023-09-01 16:20:37 7276

7276

本文介紹一個FPGA開源項目:DDR3讀寫。該工程基于MIG控制器IP核對FPGA DDR3實現讀寫操作。

2023-09-01 16:23:19 3353

3353

電子發燒友網站提供《完整的DDR、DDR2和DDR3內存電源解決方案同步降壓控制器數據表.pdf》資料免費下載

2024-03-13 10:16:45 1

1 電子發燒友網站提供《具有同步降壓控制器、2A LDO和緩沖基準的TPS51916完整DDR2、DDR3、DDR3L和DDR4存儲器電源解決方案數據表.pdf》資料免費下載

2024-03-13 11:24:34 0

0 電子發燒友網站提供《完整的DDR2、DDR3和DDR3L內存電源解決方案同步降壓控制器TPS51216數據表.pdf》資料免費下載

2024-03-13 13:58:12 0

0 電子發燒友網站提供《具有同步降壓控制器、2A LDO和緩沖基準的完整DDR2、DDR3和DDR3L存儲器電源解決方案TPS51216-EP數據表.pdf》資料免費下載

2024-03-26 11:19:21 0

0 電子發燒友網站提供《全套DDR、DDR2、DDR3、DDR3L、LPDDR3 和 DDR4 電源解決方案同步降壓控制器數據表.pdf》資料免費下載

2024-04-09 09:51:21 9

9 電子發燒友網站提供《完整DDR,DDR2,DDR3 和LPDDR3 存儲器電源解決方案同步降壓控制器數據表.pdf》資料免費下載

2024-04-09 09:49:32 0

0

電子發燒友App

電子發燒友App

評論