摘要:為了滿足高速圖像數據采集系統中對高帶寬和大容量的要求,利用Virtex-7 系列FPGA 外接DDR3 SDRAM 的設計方法,提出了一種基于Verilog-HDL 語言的DDR3 SDRAM 控制器用戶接口設計方案。該控制器用戶接口已經在Xilinx 公司的VC707 開發板上通過了功能驗證,并成功的被應用到高速圖像數據采集系統中。含有該用戶接口的控制器具有比一般的控制器接口帶寬利用率高、可移植性強和成本低的優點,可以根據設計人員的需要被靈活地應用到不同的工程。

隨著現代科學技術的高速發展,在工業生產和科學研究上,如衛星通信、高速圖像處理等領域,普遍存在對數據進行高速大容量、實時性強和高帶寬的處理要求[1,2]。高速數據采集系統作為各個系統中比較核心的部分,對數據處理的速度、實時性、穩定性以及功耗等要求都越來越高。

目前,在能夠同時滿足高帶寬和大容量要求的存儲器方案中,比較成熟的有DDR,DDR2,DDR3等,其中DDR3 具有更高的帶寬和更低的功耗,因此成為高速實時數據存儲系統設計中的首選方案[3]。由于DDR3 內存不能夠直接識別處理器的訪問請求,所以有必要通過設計一款控制器去控制DDR3的正常讀寫操作。

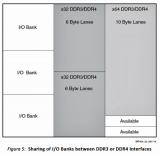

Virtex-7 系列FPGA 與Virtex-6 系列FPGA 相比,系統性能提高了一倍,功耗降低了一半,存儲器帶寬提升了2 倍,并且內有獨特的IP核mig_v1. 7,可用來解決使用DDR3 存儲器時的一些復雜問題。因此本文在介紹DDR3 的工作原理的基礎上,結合IP 核MIG_v1. 7,給出了一種利用Verilog-HDL 語言設計DDR3-SDRAM 控制器用戶接口的方法,并且提出了一種在高速圖像數據采集系統中DDR3 存儲器的應用方案,同時在Virtex-7 系列的FPGA 上實現。

1 DDR3-SDRAM 的技術特點

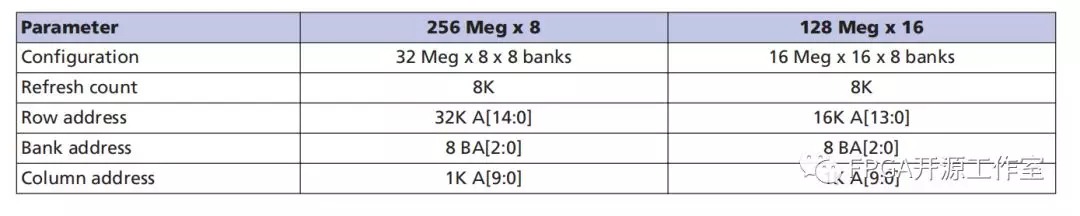

本文采用的DDR3-SDRAM 為Micron 公司的MT8JTF12864HZ-1G6G1 內存條。該DDR3 內存條的存儲空間為1 GB,由8 片容量為128 MB 的內存芯片構成。每個芯片的數據位寬為8 位,行地址線復用14 根,列地址線復用10 根,Bank 數量為8 個,因此每個內存芯片的容量為16 384 × 1 024 × 8 × 8,即128 MB。8 片組成在一起就構成了MT8JTF12864HZ-1G6G1 的64 位數據位寬,容量為1 GB。

DDR3 的控制命令信號主要有芯片選擇信號CS、行地址選擇信號RAS、列地址選擇信號CAS 和WE 寫使能信號,DDR3 的各種操作指令實質上都是通過這四個信號的組合決定的,如表1 所示。其中H 表示高電平,L 表示低電平。

?

表1 DDR3-SDRAM 的操作指令

DDR3 的Mode Register 有四個,分別為MR0、MR1、MR2 和MR3,當四個控制命令信號均為低電平時,即可通過Bank 選擇位對模式寄存器進行選擇; Refresh 操作分為Auto Refresh 與Self Refresh 兩種,其中不論是何種Refresh 方式,都不需要外部提供行地址信息,因為這是一個內部的自動操作;DDR3 在進行讀寫操作時,內存會給出一個與數據同步的DQS 信號,用來在一個時鐘周期內準確地區分出每個傳輸周期,提高了接收方接收數據的準確度。

與上一代存儲器件相比,DDR3 的內存模式有了很大的改進: 邏輯Bank 數量由DDR2 的4 個增加為8 個; 突發長度增加為8 bit,任何突發中斷操作都將在DDR3 內存中予以禁止,且不予支持; 取而代之的是更為靈活的突發傳輸控制; 其核心工作電壓由DDR2 的1. 8 V 降至1. 5 V[4],能夠在達到高帶寬的同時,大幅度的降低其功耗; DDR3 采用FLY_BY 總線,參考電壓分離,增加了ZQ 校準功能,從而大大的提高了存儲信號的完整性; 并且DDR3 為綠色封裝,不含任何有害物質,減少了對空氣的污染。

2 DDR3-SDRAM控制器用戶接口的設計

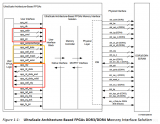

DDR3 控制器的設計采用了Xilinx 推出的IP 核MIG_v1. 7 + 用戶接口模塊的設計方法,其中本次設計主要是對用戶接口模塊進行闡述。圖1 為DDR3控制器的總體實現方案。

圖1 DDR3 控制器的總體實現方案

2. 1 用戶接口模塊的設計

用戶接口模塊為整個DDR3 控制器系統的核心模塊,其中主要包括寫數據通路和讀數據通路兩個部分,圖2 為DDR3 控制器的用戶接口設計的實現方案。

圖2 DDR3 控制器的用戶接口設計

在寫數據通路的輸入端,addr _ rdy、wr _ rdy 和init_done 為DDR3 IP 核反饋給寫數據控制模塊的信號, init_done 為高電平時指DDR3 已經完成初始化操作,addr_rdy 為高電平時表示DDR3 準備好接收寫數據地址和寫數據命令,wr_rdy 為高電平時表示DDR3 準備好接收寫數據; wr_cmd 為寫數據命令信號。在寫數據通路的輸出端,cmd_en 為輸入到DDR3 IP 核的命令和地址的使能信號,wr_en 和wr_end 為輸入到DDR3 IP 核的寫數據控制信號,跟有效寫數據信號對齊。

在用戶接口的設計中采用back_to_back 的讀寫設計模式,將addr_rdy、cmd_en、cmd 和addr 作為地址總線,將wr_rdy、wr_en、wr_end 和wr_data 作為數據總線,兩條總線是相互獨立的,兩個反饋信號addr_rdy 和wr_rdy 也是相對獨立的。在寫數據開始的時候,要保證地址總線提前數據總線一個周期使能,在addr_rdy 和wr_rdy 沒有反壓的理想情況下,寫數據要比寫地址和寫命令推遲一個周期發出,當addr_rdy 和wr_rdy 有反壓時,寫數據和寫地址可以不滿足相差一個周期被發出的。

讀數據通路與寫數據通路的設計原理相似,其中rd_valid 為讀數據有效信號, rd_data 為讀數據信號。在讀數據通路中將addr_rdy、cmd_en、cmd 和addr 作為地址總線,rd_valid 和rd_data 作為讀數據總線。

2. 2 用戶接口的時鐘模塊設計

從外界輸入200 MHz 的延遲參考時鐘、200MHz 的差分輸入時鐘,這些輸入信號經過時鐘和系統復位模塊后能夠生成整個DDR3 控制器和DDR3工作的全部時鐘,包括用戶接口的工作時鐘、DDR3 IP 核的工作時鐘和DDR3 讀寫數據的時鐘等。這種設計方法,具有簡化控制器的設計結構,便于對時鐘進行管理的優點[5]。圖3 為時鐘模塊的實現模型。

?

圖3 時鐘和系統復位模塊

3 DDR3-SDRAM控制器用戶接口的仿真

DDR3-SDRAM 的工作必須按照一定的規則進行,必須符合相應的狀態機轉換要求,圖4 給出了DDR3 存儲器工作的狀態機,該狀態機描述了DDR3各個狀態的轉換以及轉換時所涉及的一些命令。DDR3 控制器的設計實質上是圍繞著該狀態機的進行設計的,以確保內存模塊上的每個DDR3 都能正常的進行工作。

圖4 DDR3 存儲器的狀態機

3. 1 用戶接口設計模塊的Chipscope 仿真結果分析

在本次設計中,硬件仿真采用將含有此用戶接口模塊的控制器下載到Virtex-7 系列FPGA 上,通過Chipscope 在線實時地觀察用戶接口內部的信號。和圖6 中addr 每隔一個時鐘周期加1 的現象。

3. 2 用戶接口設計模塊的Modelsim 仿真結果分析

在本次設計中,軟件仿真采用ISE 14. 3 與Modelsim10.0a 相結合的方法。

圖5 為在理想情況下,用戶接口的輸入信號addr_rdy 和wr_rdy 在無反壓時候的內部信號觀測圖,在此狀態下,cmd_en 比wr_en 和wr_end 提前一個周期被拉高,有效地址與相應的有效數據之間一直保持著一個周期的時間延遲。圖6 為用戶接口在addr_rdy 和wr_rdy 信號有反壓情況下的內部信號觀測圖,在此狀態下,初始時刻cmd_en 比wr_en 和wr_end 提前一個周期被拉高,有效地址與相應的有效數據之間相差一個周期的時間延遲,但是隨著addr_rdy 和wr_rdy 被拉低之后,有效地址與相應的有效數據之間不再滿足相差一個周期的時間延遲。因為在本次設計中采用的是back-to-back 模式,地址總線與數據總線相互獨立,所以即使有效地址與相應的有效數據之間不再滿足相差一個周期的時間延遲,也不會影響數據的傳輸。在此模式下,數據與地址的傳輸比較靈活,控制起來比較方便,也有效的避免了數據的丟失。

圖5 addr_rdy 信號和wr_rdy 信號無反壓的內部信號觀測圖

圖6 addr_rdy 信號和wr_rdy 信號有反壓的內部信號觀測圖

圖7 寫數據的Modelsim 仿真圖

由于DDR3 采用的突發傳輸長度BL = 8,讀寫地址值以8 為單位連續增加,這樣addr 的低3 位將一直為0,所以在利用Chipscope 對地址進行觀測時,是從addr 的第4 位開始觀測的,即出現圖5。

由于此次設計采用的內存核心頻率為200MHz,又因為采用的DDR3 的內存總線位數為64位,DDR3 一次可以預讀取8 位,根據內存帶寬= 內存核心頻率× 內存總線位數× 倍增系數,所以在不考慮刷新和激活等操作所占用的帶寬下,DDR3 的內存帶寬可以達到12. 5 GB,傳輸速率可達到1 600MB /s。在如此快的傳輸速率下,利用Chipscope 難以觀測由DDR3 控制器寫入到DDR3 內部的數據。所以在本次設計中,采用在ISE14. 3 里面對DDR3控制器的工程添加DDR3 模型,利用Modelsim 對DDR3 控制器和DDR3 模型進行聯合仿真的方法對由控制器寫入到DDR3 內部的數據進行觀測。

從圖7 中可以看出,在一個時鐘周期內dq 的同步信號qds_n 和dqs_p 變化了8 次,也就是說,在一個時鐘周期內寫數據以64 bit 為單位被寫入了8次。由用戶接口傳輸過來的數據經過DDR3 IP 核之后,能夠準確的被寫入到DDR3 里面。當進行讀數據的時候,也是以64 bit 為單位,在一個時鐘周期內讀8 個64 bit 的數據。

3. 3 DDR3 控制器用戶接口在高速圖像數據采集系統中的應用

含有該用戶接口的DDR3 控制器已經成功的被應用到某高速圖像數據采集系統中,圖8 為該高速圖像數據采集系統采集到的圖片。

圖8 高速圖像數據采集結果圖

該圖像采集系統設置CMOS 相機工作在采用8bit 位寬的雙通道模式下,幀頻為250 幀/s,其分辨率為2 040 × 1 024。采集系統將接收到的圖像數據經過DDR3 緩存之后,通過千兆以太網接口傳輸至PC 機,再將寫入PC 機內的數據以圖片的形式顯示出來。圖8 為采集系統連續采集到的兩幀圖片,從圖中可以看出兩幀圖片的時間間隔為4 ms,滿足幀數要求,并且圖像清晰完整,達到了預期的標準。

4 結論

本次設計的硬件平臺為Xilinx 公司的Virtex-7 FPGA VC707 評估套件。7 系列的FPGA 具有比6系列和5 系列的FPGA 尺寸小、成本低、高性價比和大容量以及超高端連接帶寬等優點。

該內存控制器的用戶接口設計能夠對DDR3 內存模塊進行很好的管理,同時完成用戶發送的各種請求,并且最大限度的提高了訪問內存的速度和帶寬,避免了數據的丟失,并成功的應用到某高速圖像采集系統中。在此用戶接口的基礎上設計的內存控制器能夠與市場上大多數主流內存進行兼容,可移植性強,大大降低了開發成本。

電子發燒友App

電子發燒友App

評論