很多人可能覺得PCB信號速率越高,如25Gbps,56G/112G-PAM4信號等調試上發現的問題會越多,其實不然。我們收到最多的調試問題還是DDR3、DDR4等,不是跑不到額度速率,就是識別不到

2026-01-05 15:46:16

添加Zynq Processing System IP核,配置DDR控制器和時鐘。7000系列的Zynq可以參考正點原子DMA回環測試設置。

2025-11-24 09:25:50 2881

2881

本章的實驗任務是在 PL 端自定義一個 AXI4 接口的 IP 核,通過 AXI_HP 接口對 PS 端 DDR3 進行讀寫測試,讀寫的內存大小是 4K 字節。

2025-11-24 09:19:42 3467

3467

vivado中,怎么將e203內核源代碼封裝成ip核,并添加總線?

2025-11-10 07:22:49

下面是HummingBird EV Kit給的版圖,其中DDR3_D0對應的應該是板子上的FPGA的C2引腳:?

不過我在配置MIG的時候,通過讀入ucf文件的方式配置DDR3 SDRAM的引腳

2025-11-06 07:57:09

電子發燒友網站提供《DDR3 SDRAM參考設計手冊.pdf》資料免費下載

2025-11-05 17:04:01 4

4 前文介紹了DDR3擴展,然而,對于大塊數據而言,使用CPU進行搬運速度較慢,因此可以使用DMA進行數據搬運。這里會使用到前文提到的中斷與DDR3。

本例中使用了Vivado提供的AXI-DMA

2025-10-29 08:21:10

由于FPGA內部存儲資源有限,很多時候不能滿足需求,因此可以利用DDR對系統進行存儲擴展。由于DDR3內部控制十分復雜,因此可以基于AXI總線,利用Vivado提供的MIG IP對DDR3進行控制

2025-10-29 07:16:34

文件夾內,打開文件夾。閱讀readme說明文檔,我們能夠知道,原作者采用了vivado MIG IP來控制開發板上的DDR3,由于芯來科技的E203平臺系統片內總線是icb總線,所以我們需要做跨時鐘域

2025-10-28 07:25:32

DDR使用

在我們的項目中,我們使用的是芯來科技的DDR200T開發板,我們通過調用板上的DDR3 IP核完成如下表的配置,配置完成后例化該DDR3,然后利用DMA和VDMA作為數據的緩沖模塊,將

2025-10-28 07:24:01

VDMA端口信號

S_AXI_LITE:PS端可以通過AXI_LITE協議對IP核進行控制;

S_AXIS_S2MM:視頻流(AXI STREAM)輸入到IP核的FIFO中

2025-10-28 06:14:54

蜂鳥E203軟核工作的主頻為16MHz高頻時鐘和3.2768KHz低頻時鐘,并且不同開發板提供的晶振頻率不同,因此需要例化mmcm IP核和reset IP核將外部晶振時鐘轉換為兩個不同頻率

2025-10-27 07:35:23

:使用DDR200T上板載的DDR3對內存進行擴展

擴展方案結構圖:

該方案中DDR3使用vivado提供的axi接口mig的IP核來進行控制,蜂鳥e203源代碼中提供了icb2axi模塊,可以使發出

2025-10-24 08:12:53

綜合時不需要,直接注釋掉),并在design source中添加ddr3_model.sv和ddr3_model_parameters.vh文件。

在IP Source中右鍵點擊mig的ip核,然后

2025-10-24 07:25:00

接口,以便我們后面使用axi接口的DDR3。

(2)axi_interconnect模塊

(3)mig模塊

mig 的模塊配置具體可參考:https://blog.csdn.net

2025-10-24 07:08:09

是1bit1bit進來的,則需要tlast,發完最后一個bit時拉高,tuser可以用來配置表示一些用戶需要的信息)。

需要注意的是,本以為只有當數據數據的valid拉高后,IP核才能接受數據,但仿真的波形

2025-10-24 07:01:36

Vivado浮點數IP核的一些設置注意點

我們在vivado2018.3中使用了Floating-point(7.1)IP核,可以自定義其計算種類及多模式選擇。有時多種計算可以用同一個IP核實

2025-10-24 06:25:22

決定的。 ram 主要用來存放程序及程序執行過程中產生的中間數據、 運算結果等。

rom為只讀存儲器,只能讀取數據而不能向里面寫入數據。

本次講解的ram ip核ram指的是bram,即block

2025-10-23 07:33:21

準備工作:

1.蜂鳥e203的RTL源碼;

2.一段分頻代碼;

3.頂層設計文件(system.v)

4.開發板文件;

5.Nexys4DDR電路圖;

6.Nexys4DDR管腳約束模板

2025-10-23 07:22:22

soc_top層的ddr3的接口引出到最頂層system,mig的ddr3管腳約束在配置mig核的時候已經完成,不用再考慮。

(2)綜合時需要把ui_clk和clk_16M間的時序路徑設成

2025-10-23 06:16:44

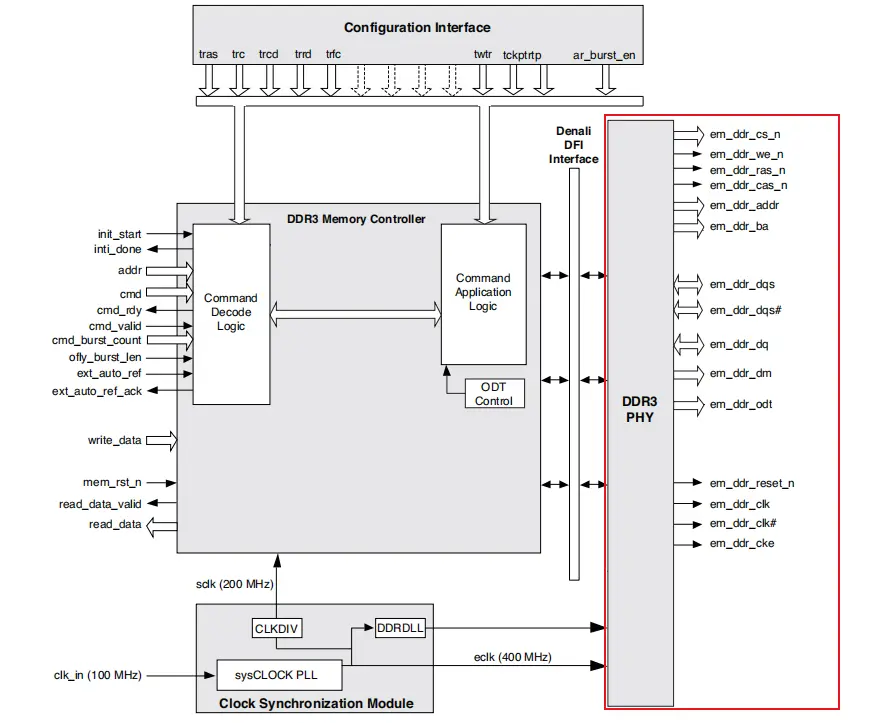

DDR讀寫操作的控制流程。下圖所示是7系列的MIG IP核結構圖。MIG IP核對外分出了兩組接口,左側是用戶接口,右側是DDR物理芯片接口,負責產生具體的操作時序,并直接操作芯片管腳。

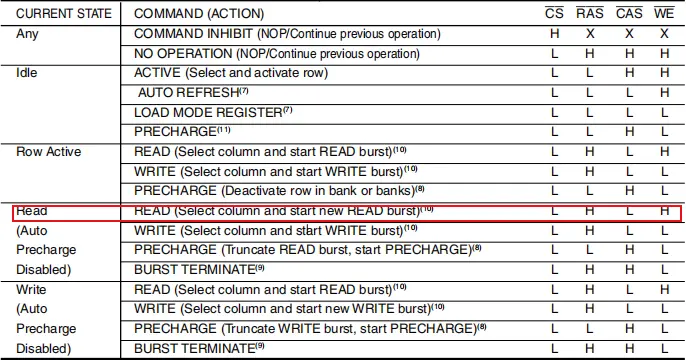

DDR3的讀寫

2025-10-21 14:30:16

IP DDR3控制器 RISC-V

基于DDR200T開發板原理圖,找到所需要使用的DDR引腳,制成DDR.ucf文件方便在添加管腳約束時使用。在使用MIG IP核時,為了方便使用DDR產生的時鐘

2025-10-21 12:43:40

蜂鳥DDR200T中DDR3的ip配置案列,提供DDR3引腳配置。具體參數可更具項目實際更改。

這里選用的axi接口

在賽靈思的IP配置中沒有MT41K28M6JT-125K內存的信息,因此選用

2025-10-21 11:19:08

流程。下圖所示是7系列的MIG IP核結構圖。MIG IP核對外分出了兩組接口,左側是用戶接口,右側是DDR物理芯片接口,負責產生具體的操作時序,并直接操作芯片管腳。

DDR3的讀寫都包含寫命令操作

2025-10-21 10:40:28

的控制流程。下圖所示是7系列的MIG IP核結構圖。MIG IP核對外分出了兩組接口,左側是用戶接口,右側是DDR物理芯片接口,負責產生具體的操作時序,并直接操作芯片管腳。

DDR3的讀寫都包含寫

2025-10-21 08:43:39

回收DDR2,回收DDR3,收購DDR2,收購DDR3 DDR4 DDR5長期現金高價回收DDR,回收三星DDR,回收海力士DDR,回收南亞DDR,回收爾必達DDR,回收美光DDR,回收DDR

2025-10-09 14:15:34

在第二期的特性阻抗講解中,我們提到了傳輸線路。雖然將傳輸線比作水路,但它究竟是通過什么原理傳輸信號和電力的呢?

2025-10-09 13:49:14 1917

1917

我們常聽到的“特性阻抗”究竟是什么?它與通常所說的“阻抗”或“直流電阻”有何區別?雖然“特性阻抗”和“阻抗”都使用[Ω]單位,但它們之間存在什么差異?

2025-09-17 15:07:29 1174

1174

) == RT_Object_Class_Memory) assertion failed at function:rt_smem_alloc, line number:290 ;

然后內核改成V4.1.1就沒任何問題。

因為v5.0.2下引入backtrace也始終有編譯問題,所以不好跟蹤究竟是為何。

2025-09-15 07:46:09

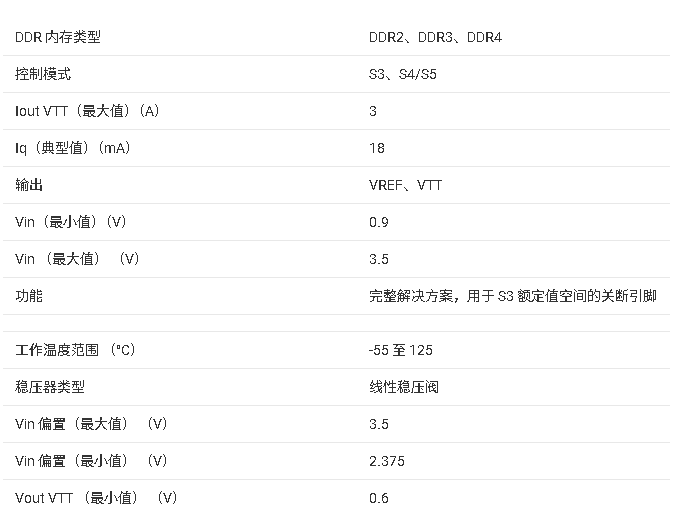

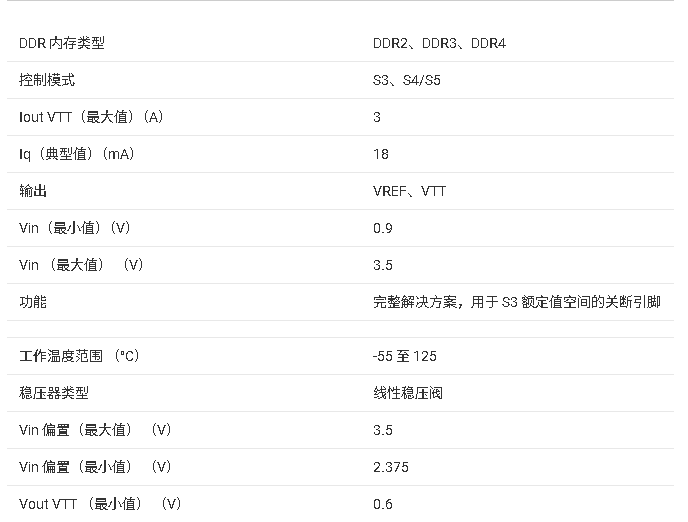

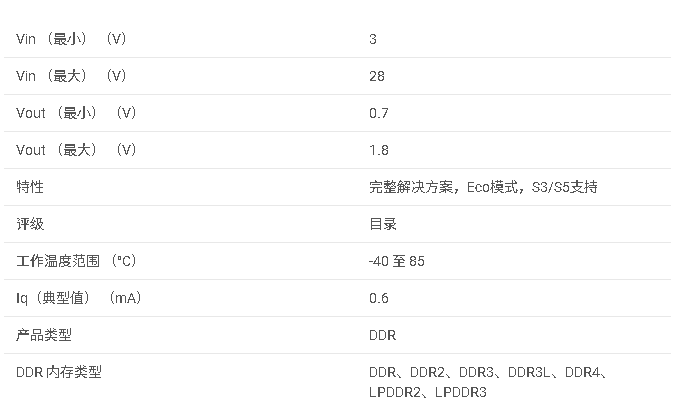

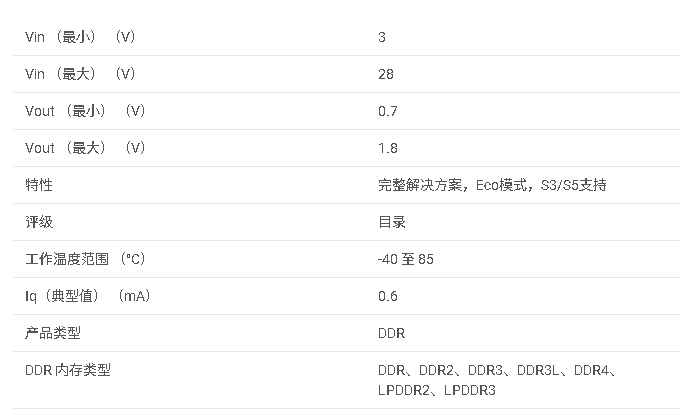

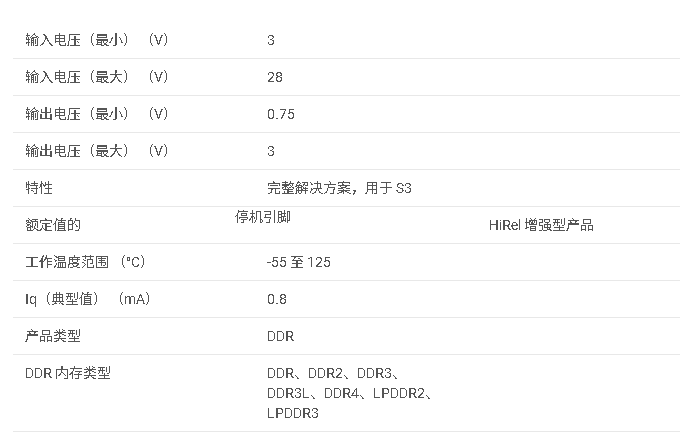

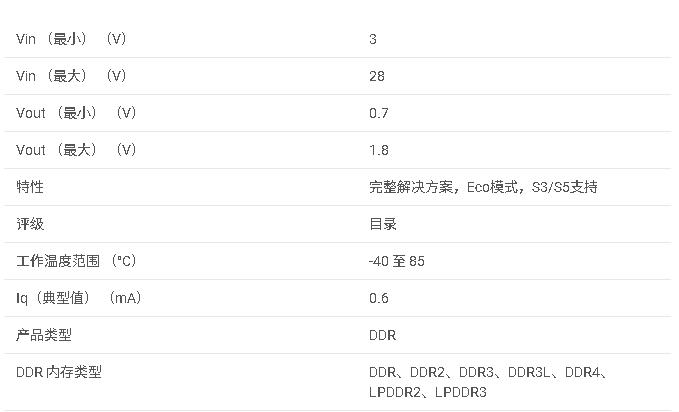

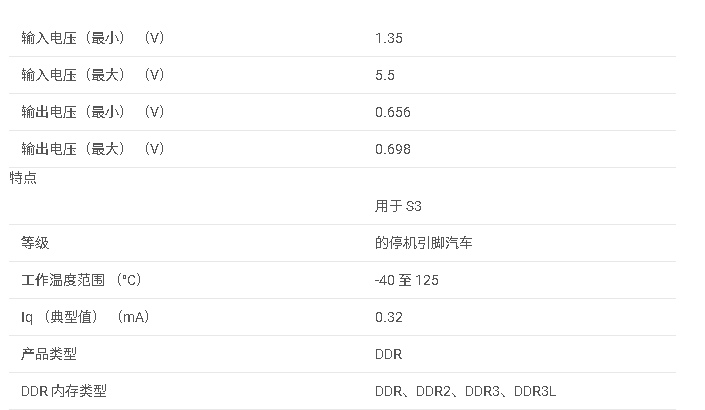

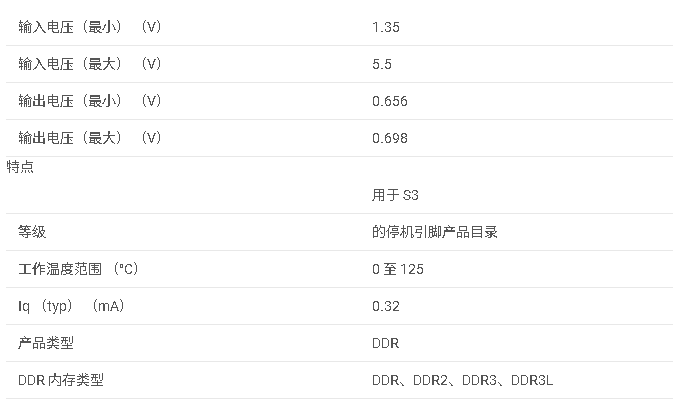

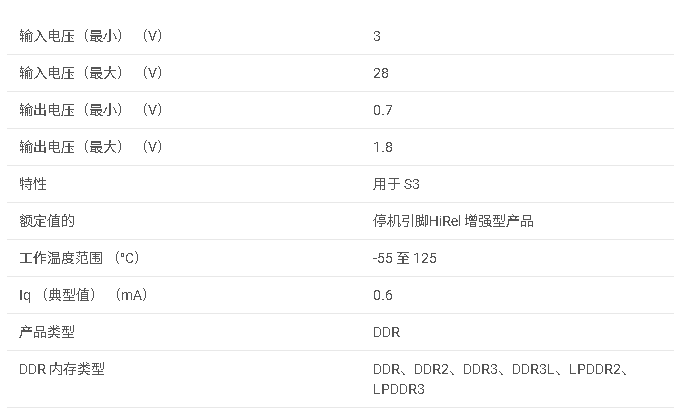

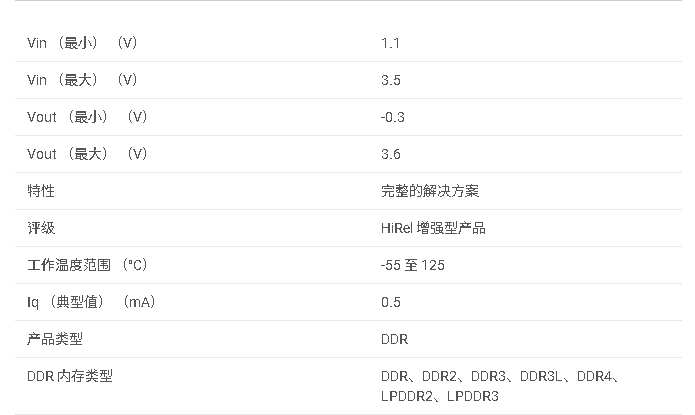

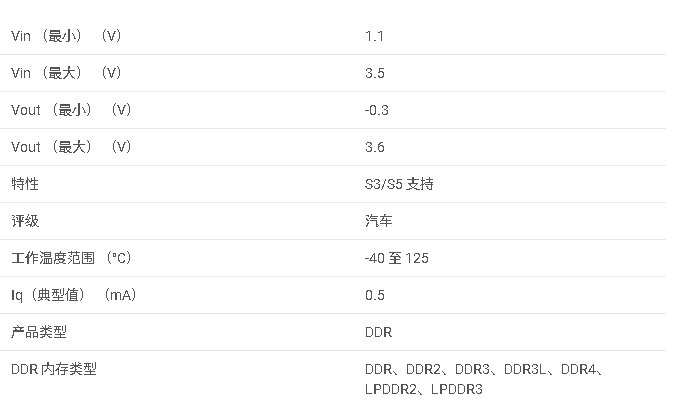

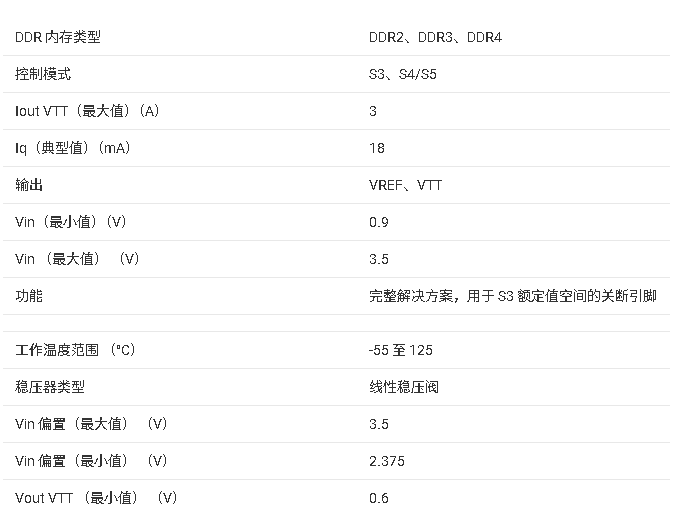

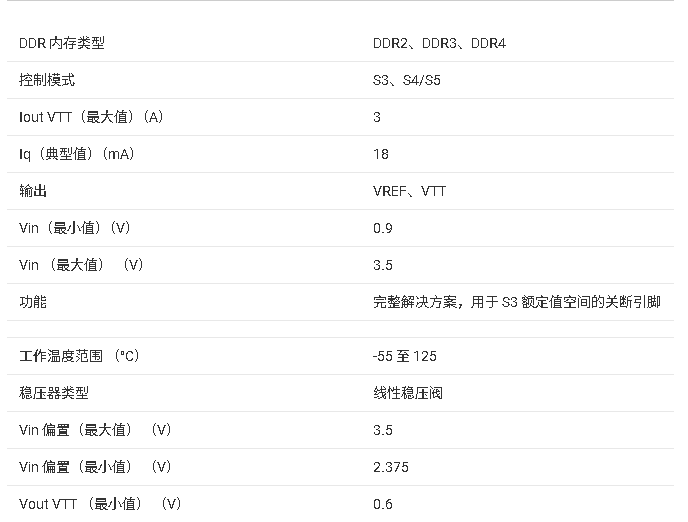

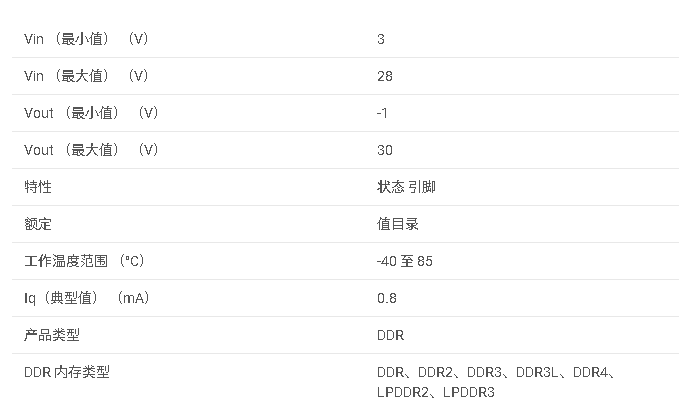

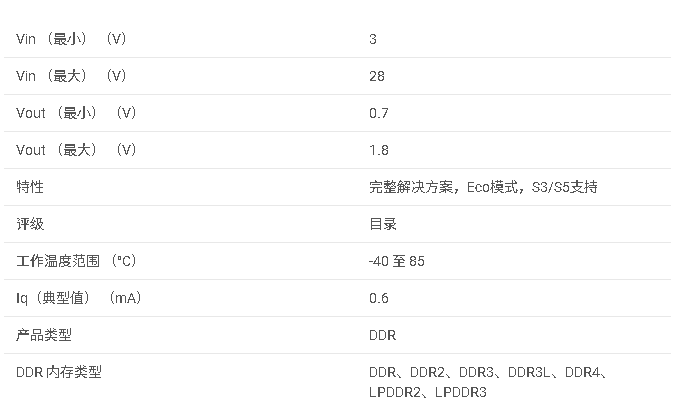

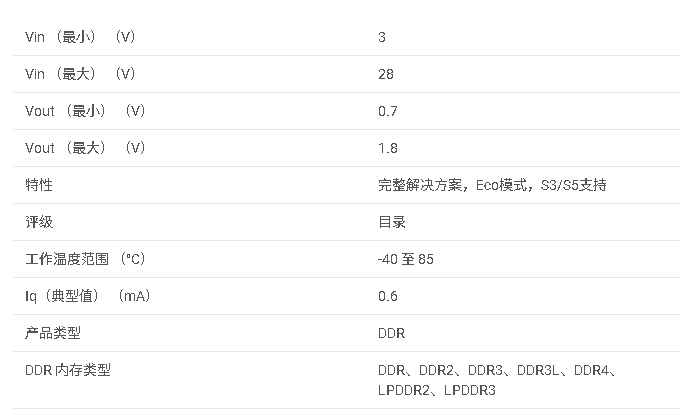

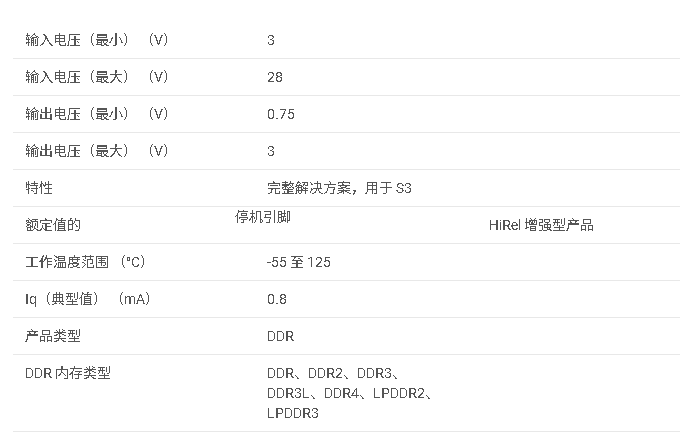

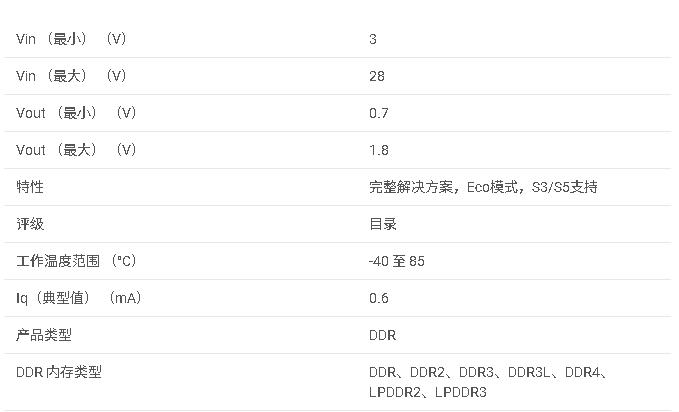

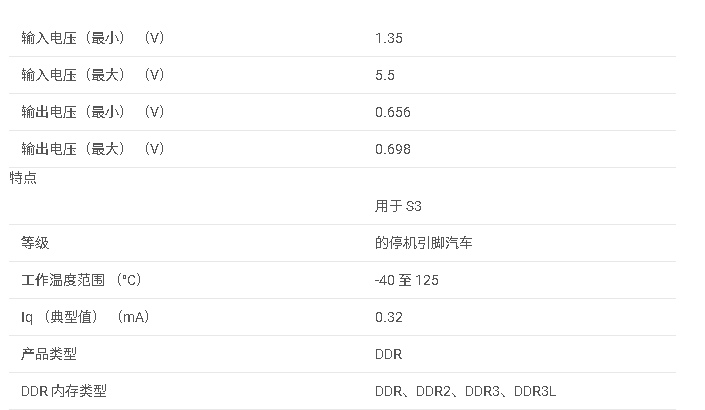

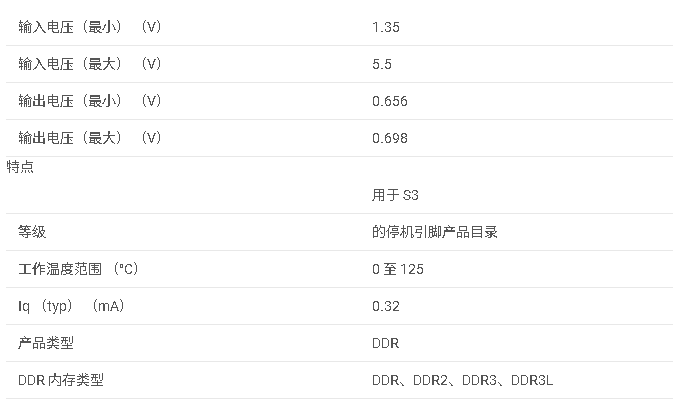

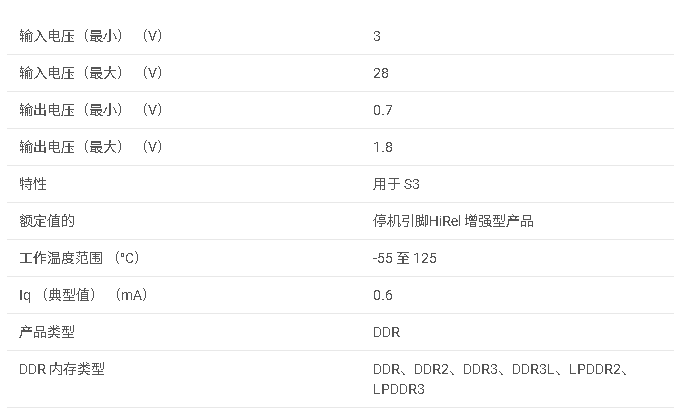

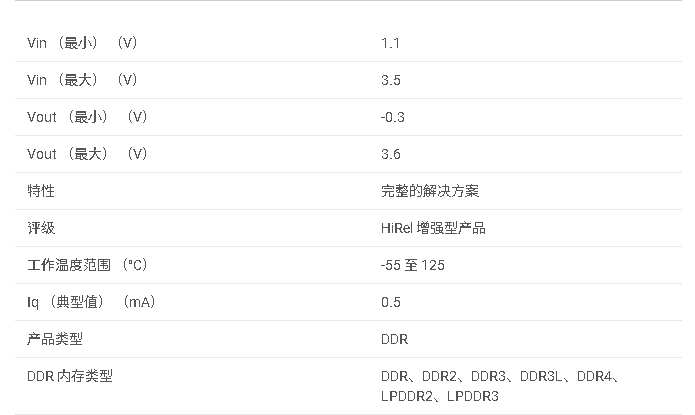

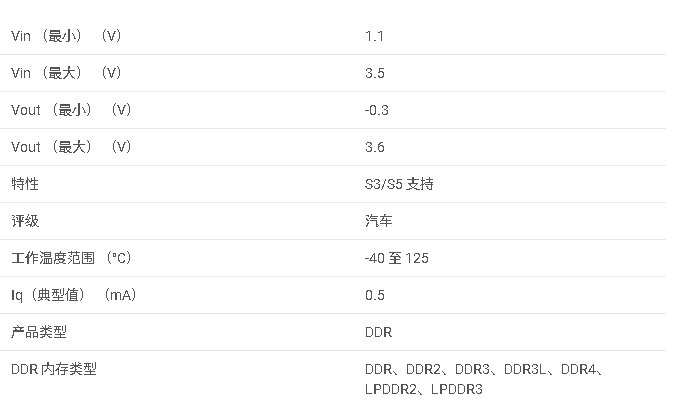

TPS7H3301-SP 支持使用 DDR、DDR2、DDR3、DDR4 的 DDR VTT 端接應用。TPS7H3301-SP VTT 穩壓器的快速瞬態響應允許在讀/寫條件下提供非常穩定的電源。在

2025-09-09 14:45:15 719

719

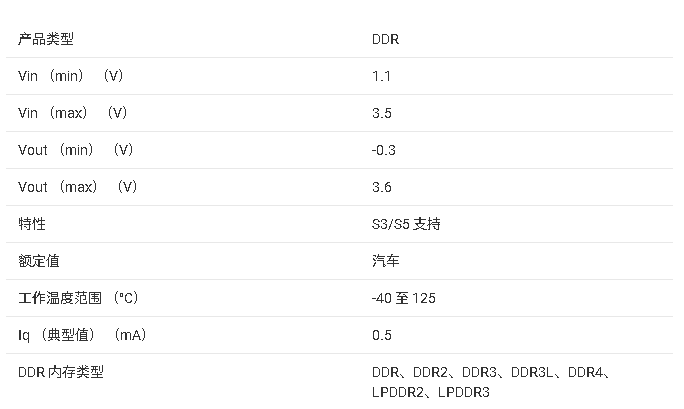

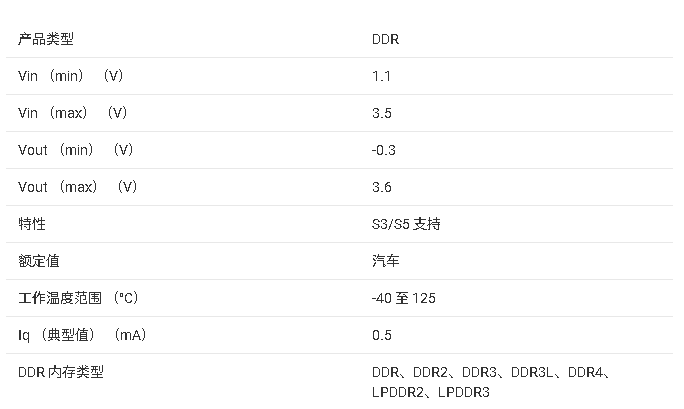

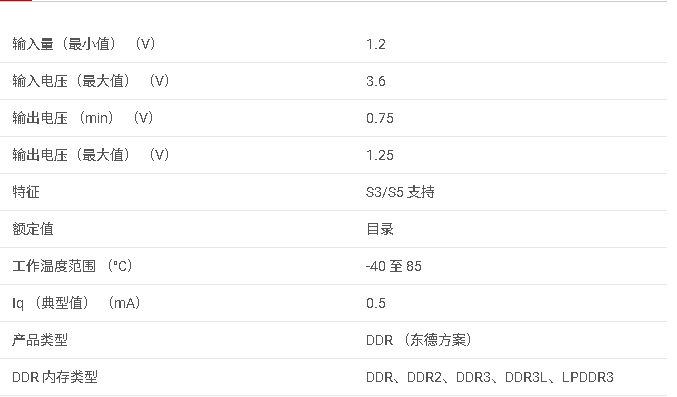

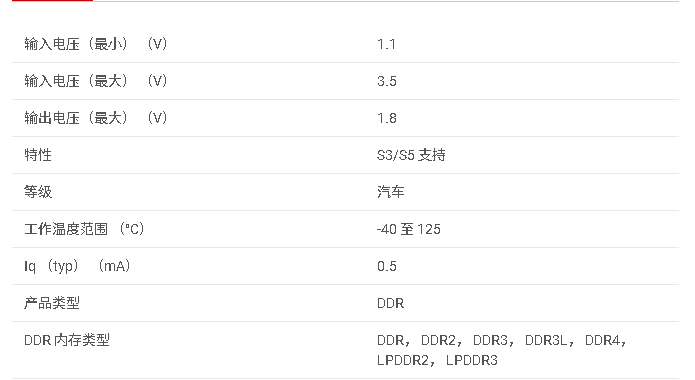

20 μF。該器件支持遙感功能以及 DDR、DDR2、DDR3 以及低功耗 DDR3 和 DDR4 VTT 總線端接的所有電源要求。

2025-09-09 14:28:07 713

713

該TPS7H3302支持使用 DDR、DDR2、DDR3、DDR3L 和 DDR4 的 DDR VTT 端接應用。TPS7H3302 VTT 穩壓器的快速瞬態響應允許在讀/寫條件下提供非常穩定的電源

2025-09-09 13:48:37 756

756

很多現在都在建設標準化考場,標準化考場究竟是什么呢?

2025-09-05 16:45:58 1228

1228

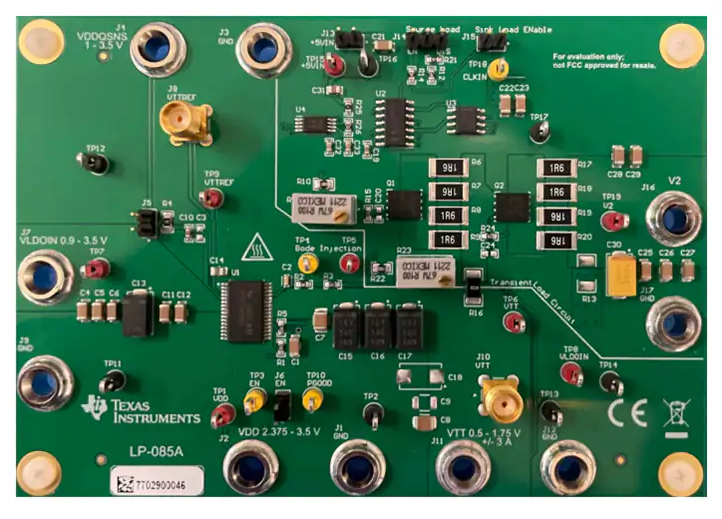

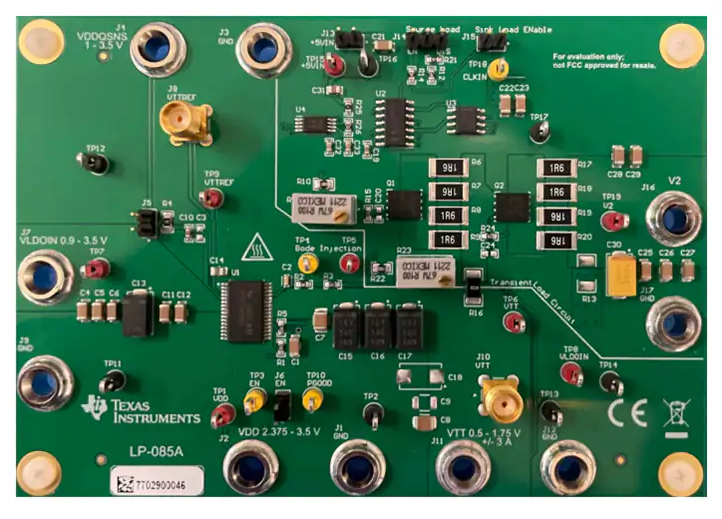

3A,支持測試DDR、DDR2、 DDR3、DDR3L和DDR4。該評估模塊配有方便的測試點和跳線,用于評估TPS7H3302-SEP DDR端子。TPS7H3302EVM評估模塊非常適合用于抗輻射DDR電源應用以及用于DDR、DDR2、DDR3和DDR4的存儲器終端穩壓器。

2025-08-27 16:14:21 833

833

憑借與紫光國芯的緊密合作,貞光科技能夠為客戶提供DDR3、LPDDR4及LPDDR4X全系列車規級存儲產品。在產品覆蓋、技術支持和供應保障等方面的綜合優勢,使貞光科技成為車載電子領域可靠且高效

2025-08-26 16:12:15 1430

1430

無人機在天空中自由穿梭、穩穩懸停,背后究竟是什么在發揮關鍵作用呢?這就不得不提到一個重要部件 ——IMU。

2025-08-12 14:27:24 1264

1264 在現代制造業中,數控機床的應用極為廣泛,其加工精度直接影響著產品的質量和性能。而多摩川高分辨率編碼器的出現,為數控機床的超精密運動控制帶來了新的突破。那么,它究竟是如何實現這一賦能的呢?讓我們一探究竟。

2025-08-04 17:59:29 887

887 本文緊接著前一個文檔《AD設計DDR3時等長設計技巧-數據線等長 》。本文著重講解DDR地址線、控制信號線等長設計,因為地址線、控制信號線有分支,SOC有可能帶有2片DDR或者更多,我們叫做T型分支

2025-07-29 16:14:51 2

2 的講解數據線等長設計。? ? ? 在另一個文件《AD設計DDR3時等長設計技巧-地址線T型等長》中著重講解使用AD設計DDR地址線走線T型走線等長處理的方法和技巧。

2025-07-28 16:33:12 4

4 技術手冊,適用于使用LogiCORE IP核(如DDR3/DDR2 SDRAM、RLDRAM II、QDRII+)進行存儲器接口設計26。核心功能:IP核配置與時序:詳細說明Xilinx MIG(Memory Interface Generator)IP核的使用方法,包括信號定義、時序約束、物理層(PHY

2025-07-28 16:17:45 3

3 ASIC設計服務暨IP研發領導廠商智原科技(Faraday Technology Corporation)宣布推出可支持第三至第五代DDR/LPDDR的通用物理層IP,適用于聯電(UMC)22ULP

2025-07-25 16:41:25 939

939 Training

DDR3 最快速率達 1066 Mbps

3.工程說明

PDS 安裝后,需手動添加 DDR3 IP,請按以下步驟完成:

DDR3 IP 文件:PG2L_IP\\\\PG2L_IP

2025-07-10 10:46:48

站在戰略升級的關鍵節點,聞泰科技正在全力聚焦半導體業務,開啟全新發展階段。值此之際,公司特別推出 《探秘“芯”世界》系列專題,邀您一同探索半導體的奧秘,見證聞泰科技以創新引領行業的 "芯" 力量。

2025-07-09 11:42:19 1137

1137 。

src\\\\DDR3\\\\DDR3ControllerGWTopLite.v: DDR3內存控制器IP核。它將AXI總線協議轉換為DDR3芯片能理解的底層讀寫命令。

src\\\\DDR3

2025-07-06 15:18:53

實現將SC130GS采集的黑白圖像數據緩存進DDR3,并以1024600@60的視頻時序輸出到LVDS

屏幕顯示。其中,DDR3工作頻率為600MHz,SC130GS輸入的圖像數據大小為

2025-07-02 10:26:48

DDR內存占據主導地位。全球DDR內存市場正經歷一場前所未有的價格風暴。由于原廠加速退出DDR3/DDR4市場,轉向DDR5和HBM(高帶寬內存)生產,DDR3和DDR4市場呈現供不應求、供需失衡、漲勢延續的局面。未來,DDR5滲透率將呈現快速提升,市場份額增長的趨勢。

2025-06-25 11:21:15 2013

2013

turbo譯碼器IP核,控制接口配置了flush、standard、size,輸入接口送的是編碼后量化的數據,因為編碼輸出的是1bit(0或1),量化為5位有符號數,小數部分配0,對應fix8_3

2025-06-23 17:39:24

隨著汽車產業向智能化、網聯化加速轉型,高級駕駛輔助系統(ADAS)和智能駕駛技術已成為現代汽車不可或缺的核心組件。紫光國芯作為國內領先的存儲器芯片制造商,其車規級DDR3存儲產品在智能駕駛和ADAS

2025-06-05 16:50:17 1225

1225

物理層的位置,一種是物理層在JESD204 IP里;另外一種是物理層在JESD204 IP外部,需要再配置JESD204 phy IP核進行使用。

2025-05-24 15:05:00 1827

1827

ADC 江湖風云變幻,局勢不斷升級,緊張刺激!究竟是內置 ADC 更勝一籌還是外置 ADC 棋高一著?

2025-05-14 15:24:42 1309

1309 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布率先推出基于臺積公司 N3 工藝的 DDR5 12.8Gbps MRDIMM Gen2 內存 IP 解決方案。該新解決方案可滿足

2025-05-09 16:37:44 905

905 學習FOC電機控制究竟是學哪些內容?

電機知識

軟件知識

純分享貼,有需要可以直接下載附件獲取完整資料!

(如果內容有幫助可以關注、點贊、評論支持一下哦~)

2025-05-09 14:09:43

繼電保護是電力系統中的“安全衛士”,其核心任務是?快速檢測故障并隔離故障區域?,確保電力設備免遭損壞、防止停電范圍擴大,同時維護電網的穩定運行。在現代電力系統中,繼電保護裝置如同人體的免疫系統,能夠在毫秒級時間內識別異常并采取行動,是保障供電安全的核心技術之一。

一、繼電保護的四大核心功能

?故障檢測?

實時監測電流、電壓、頻率等電氣參數,精準識別短路、過載、接地故障等異常狀態。例如:

短路故障:電流驟增至正常值的數倍至數十倍。

接地故障:中性點電壓偏移或零序電流異常。

?故障隔離?

通過控制斷路器在?20-100毫秒內?切斷故障線路,避免故障蔓延。例如:

輸電線路發生短路時,距離保護裝置可迅速定位故障點并跳閘。

?告警與記錄?

觸發聲光報警,并記錄故障波形、動作時間等數據,為后續故障分析提供依據。

?系統自愈支持?

配合自動化設備(如重合閘裝置),在故障清除后嘗試恢復供電,減少停電時間。

二、繼電保護的組成與工作原理

?系統架構

?組件

?功能?

?測量元件

采集電流互感器(CT)、電壓互感器(PT)信號

?邏輯判斷單元

分析參數是否符合故障特征(如過流、差動)

?執行元件

驅動斷路器或發信裝置動作

?

?典型保護原理?

?過電流保護?:檢測電流超過設定閾值(如1.2倍額定電流),適用于配電網線路。

?差動保護?:比較設備兩端電流差值,若差值超限則判定內部故障(常用于變壓器、發電機)。

?距離保護?:通過阻抗計算定位故障點位置,適用于長距離輸電線路。

三、繼電保護的應用場景

?發電環節?

發電機保護:定子接地保護、轉子過負荷保護、失磁保護等。

案例:某水電站因差動保護動作,0.1秒內隔離發電機內部短路,避免機組燒毀。

?輸電與變電環節?

輸電線路:縱聯保護、光纖差動保護,保障跨區域電網安全。

變壓器:瓦斯保護(非電量)、比率制動差動保護,防止絕緣油分解或繞組故障。

?配電環節?

配網饋線:過流保護配合自動重合閘,減少用戶停電時間。

數據:90%的配電故障可在300毫秒內隔離并恢復供電。

四、繼電保護的技術演進

?從電磁式到數字化?

?早期電磁繼電器?:依靠機械觸點動作,響應速度慢(>100ms),維護頻繁。

?微機保護裝置?:集成DSP芯片,支持多判據融合計算,動作時間縮短至20ms以內。

?智能化升級?

?廣域保護系統?:基于5G通信實時共享電網狀態,實現跨區域協同控制。

?AI故障預測?:利用機器學習分析歷史數據,提前預警絕緣老化風險。

?挑戰與突破?

新能源并網:光伏、風電的波動性要求保護裝置具備自適應能力。

解決方案:引入“方向性過流保護”應對分布式電源雙向電流沖擊。

五、總結

繼電保護是電力系統安全運行的基石,其價值體現在三個方面:

?經濟性?:減少設備損壞帶來的巨額維修成本(如一臺500kV變壓器損壞損失超千萬元)。

?可靠性?:保障99.99%以上的供電可用性,支撐現代社會穩定運轉。

?智能化?:隨著數字孿生、邊緣計算等技術的融合,繼電保護正從“被動響應”邁向“主動防御”。

未來,繼電保護將與能源互聯網深度結合,成為構建新型電力系統的核心防線。

2025-05-06 10:32:41

下面是調用的DDR3模塊的,模塊的倒數第二行是,模塊的時鐘輸入,時鐘源來自PLL產生的系統時鐘的倍頻。

2025-05-03 10:21:00 1339

1339

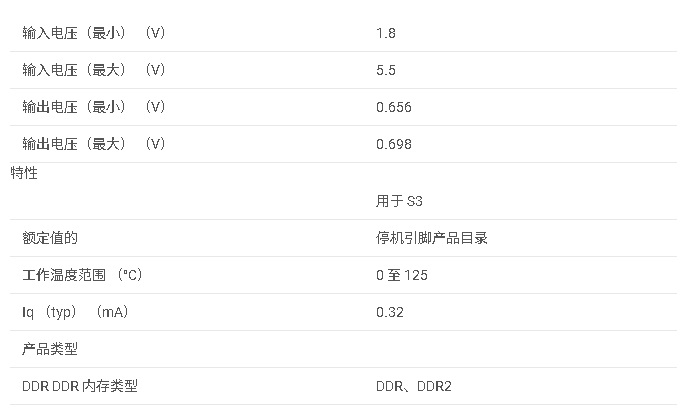

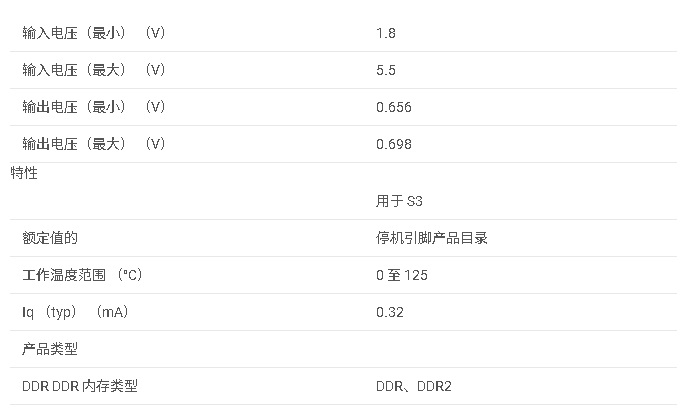

LP2996-N 和 LP2996A 線性穩壓器旨在滿足 JEDEC SSTL-2 標準 DDR-SDRAM 終止規范。該器件還支持 DDR2,而 LP2996A 支持 DDR3 和 DDR3

2025-04-29 18:11:05 834

834

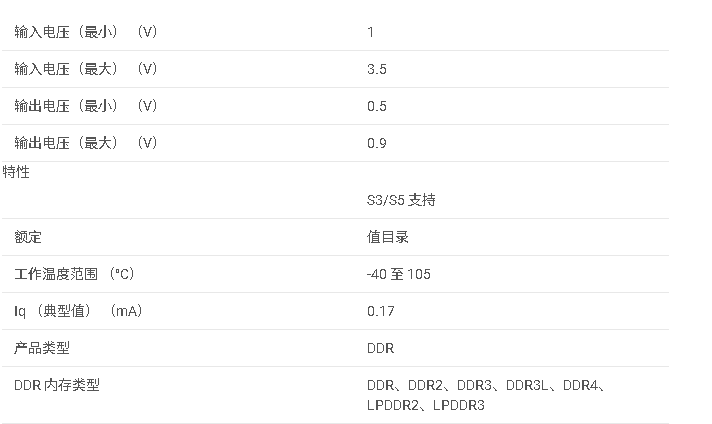

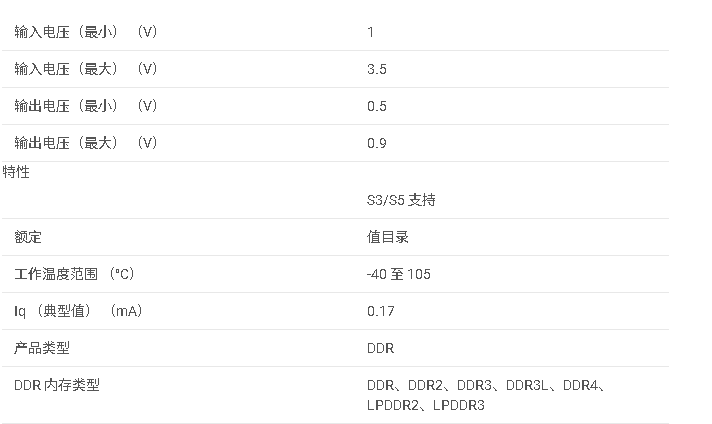

終端供電。這 該器件還支持 DDR3 VTT 端接,VDDQ 電壓為 1.5 V(典型值)。此外,TPS51100 包括集成的睡眠狀態控制、在 S3 中將 VTT 置于 Hi-Z(暫停到 RAM)和軟

2025-04-29 17:15:20 774

774

TPS51116為 DDR/SSTL-2、DDR2/SSTL-18、DDR3/SSTL-15、DDR3L、LPDDR3 和 DDR4 內存系統提供完整的電源。它將同步降壓控制器與 3A 灌電流/拉

2025-04-29 16:38:02 1031

1031

在高速PCB設計中,DDR模塊是絕對繞不過去的一關。無論你用的是DDR、DDR2還是DDR3,只要設計不規范,后果就是——信號反射、時序混亂、系統頻繁死機。

2025-04-29 13:51:03 2491

2491

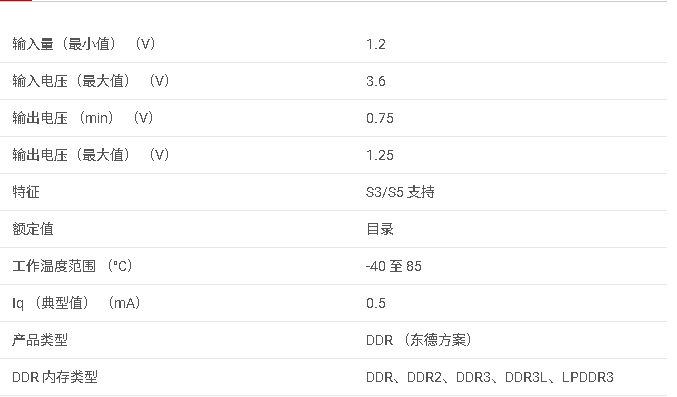

LP2998 線性穩壓器旨在滿足 JEDEC SSTL-2 和 JEDEC SSTL-18 標準 DDR-SDRAM 和 DDR2 內存終止的規范。該器件還支持 DDR3 和 DDR3L VTT

2025-04-29 11:34:59 810

810

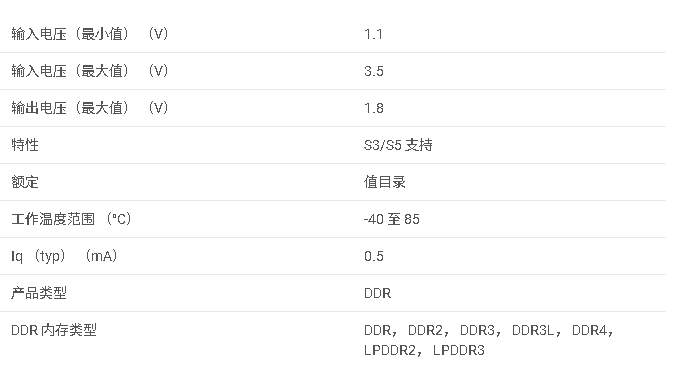

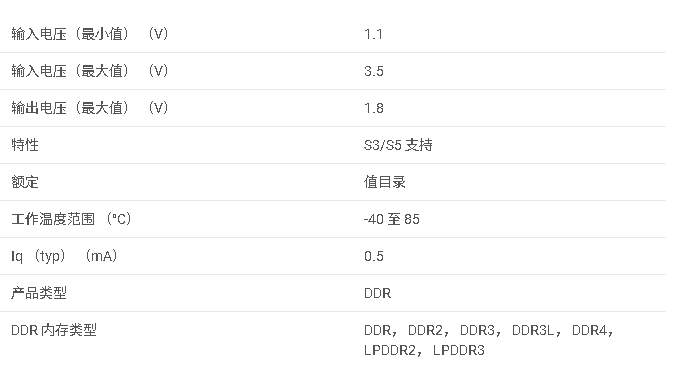

僅為 20 μF。該TPS51200支持遠程感應功能以及 DDR、DDR2、DDR3、DDR3L、低功耗 DDR3 和 DDR4 VTT 總線終端的所有電源要求。

2025-04-29 09:59:25 1345

1345

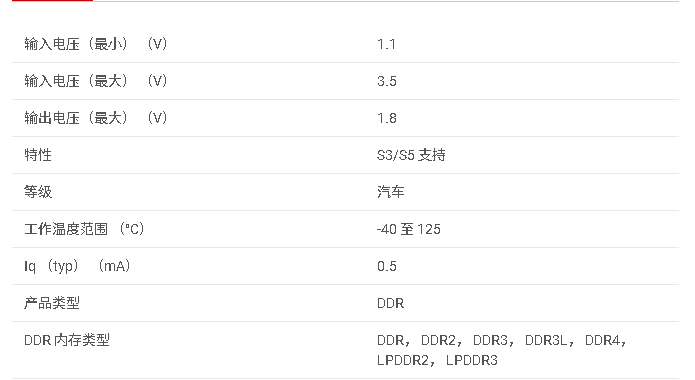

只需要 20 μF 的最小輸出電容。TPS51200-Q1 器件支持遠程感應功能以及 DDR、DDR2、DDR3、DDR3L、低功耗 DDR3 和 DDR4 VTT 總線終端的所有電源要求。

2025-04-28 16:21:07 852

852

TPS59116 為 DDR/SSTL-2、DDR2/SSTL-18 和 DDR3 內存提供完整的電源 系統。它將同步降壓控制器與 3A 灌電流/拉電流跟蹤線性穩壓器和緩沖低噪聲基準集成在一起

2025-04-28 13:54:45 814

814

TPS51216 以最低的總成本和最小的空間為 DDR2、DDR3 和 DDR3L 內存系統提供完整的電源。它將同步降壓穩壓控制器 (VDDQ) 與 2A 灌/拉跟蹤 LDO (VTT) 和緩

2025-04-28 11:09:05 663

663

TPS51916 器件以最低的總成本和最小的空間為 DDR2、DDR3、DDR3L 和 DDR4 內存系統提供完整的電源。它集成了同步降壓穩壓控制器 (VDDQ),具有 2A 灌電流和 2A 源跟蹤 LDO (VTT) 和緩沖低噪聲基準 (VTTREF)。

2025-04-28 10:58:44 657

657

快速瞬態響應,并且只需要 1 × 10μF 的陶瓷輸出電容。該器件支持遠程感應功能以及 DDR2、DDR3 和低功耗 DDR3 (DDR3L) 以及 DDR4 VTT 總線的所有電源要求。VTT 電流

2025-04-28 10:04:48 685

685

TPS51116為 DDR/SSTL-2、DDR2/SSTL-18、DDR3/SSTL-15、 和 LPDDR3 內存系統。它將同步降壓控制器與 1A 灌電流/拉電流集成在一起 跟蹤線性穩壓器和緩

2025-04-27 13:35:32 741

741

TPS51716為 DDR2、DDR3、DDR3L、LPDDR3 和 DDR4 提供完整的電源 以最低的總成本和最小空間實現內存系統。它集成了一個同步降壓 具有 2A 灌電流/拉電流跟蹤 LDO

2025-04-27 11:36:05 763

763

LP2998 線性穩壓器旨在滿足 JEDEC SSTL-2 和 JEDEC SSTL-18 標準 DDR-SDRAM 和 DDR2 內存終止的規范。該器件還支持 DDR3 和 DDR3L VTT

2025-04-27 09:40:04 874

874

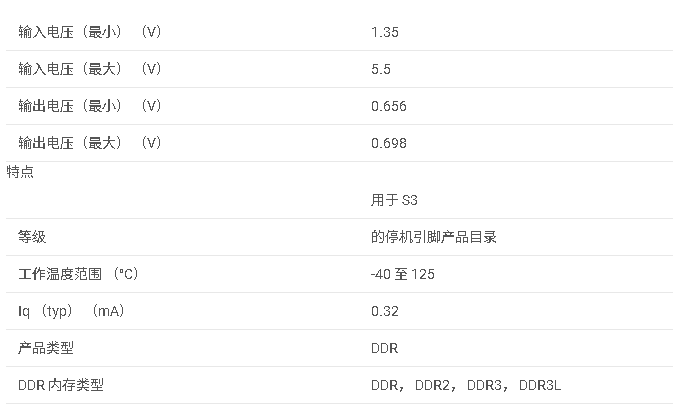

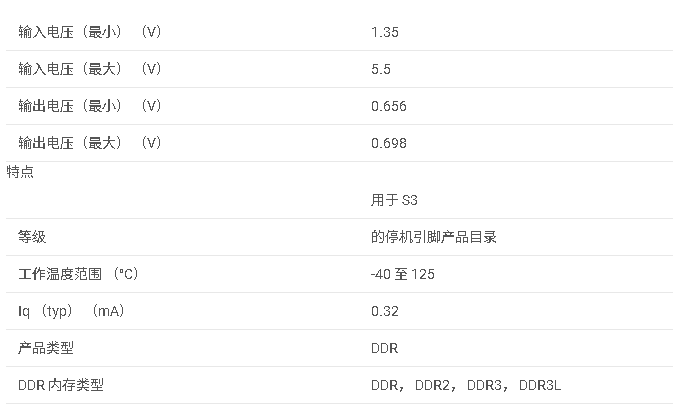

LP2996A 線性穩壓器旨在滿足 JEDEC SSTL-2 規范 DDR-SDRAM 終止。該器件還支持 DDR2、DDR3 和 DDR3L VTT 總線端接,帶 V~DDQ~最小為 1.35V

2025-04-26 15:02:50 746

746

TPS51216-EP 以最低的總成本和最小的空間為 DDR2、DDR3 和 DDR3L 內存系統提供完整的電源。它將同步降壓穩壓控制器 (VDDQ) 與 2A 灌/拉跟蹤 LDO (VTT) 和緩

2025-04-26 11:12:30 681

681

只需要最小輸出 電容為 20 μF。TPS51200-EP 支持遙感功能和所有功率要求 用于 DDR、DDR2、DDR3、低功耗 DDR3 和 DDR4 VTT 總線終端。

2025-04-26 10:26:35 1335

1335

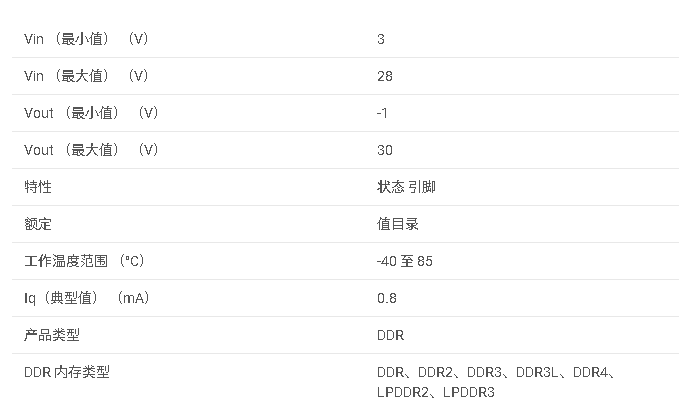

的最小輸出電容。該器件支持遠程感應功能以及 DDR、DDR2、DDR3 以及低功耗 DDR3 和 DDR4 VTT 總線終端的所有電源要求。

2025-04-25 10:07:15 1054

1054

在全球科技競爭加劇、國產替代加速推進的背景下,紫光國芯憑借其在DDR3與RDIMM等高端內存芯片領域的技術積累,不斷實現突破,推動國產存儲芯片向高端市場邁進。作為其核心代理商,貞光科技在市場推廣

2025-04-16 16:39:30 1343

1343

DDR3 SDRAM(Double-Data-Rate ThreeSynchronous Dynamic Random Access Memory)是DDR SDRAM的第三代產品,相較于DDR2,DDR3有更高的運行性能與更低的電壓。

2025-04-10 09:42:53 3930

3930

Video In to AXI4-Stream IP核用于將視頻源(帶有同步信號的時鐘并行視頻數據,即同步sync或消隱blank信號或者而后者皆有)轉換成AXI4-Stream接口形式,實現了接口轉換。該IP還可使用VTC核,VTC在視頻輸入和視頻處理之間起橋梁作用。

2025-04-03 09:28:14 2418

2418

我們目前正在使用 iMX6UL DDR 寄存器編程輔助工具為 U-Boot 生成 DCD 表。我們的設備使用的是 MT41K128M16JT-107,即 DDR3-1866,這意味著它的時鐘周期頻率

2025-03-27 07:16:35

燦芯半導體(上海)股份有限公司(燦芯股份,688691)宣布推出基于28HKD 0.9V/2.5V 平臺的DDR3/4, LPDDR3/4 Combo IP。該IP具備廣泛的協議兼容性,支持DDR3

2025-03-21 16:20:03 984

984 初次使用XC7A35T-FGG484做設計,用的是25MHZ有源晶振,有源晶振3.3V供電,DDR3的供電1.35V,現在接上晶振后,DDR3的供電變成1.8V

求助怎么解決。

2025-03-21 14:25:05

很多工程師在產品選型的時候會疑惑,究竟是選CAN接口卡還是CANFD接口卡呢?兩者之間有什么區別呢?影響選擇的關鍵因素又是什么?我們今天一個一個來拆解。1.波特率傳統的CAN接口卡僅有一個波特率,即

2025-03-21 11:37:40 790

790

在日常生活中,我們可能很少直接接觸到氣密性檢測儀,但在工業生產、汽車制造、醫療器械等領域,它卻是不可或缺的"神器"。那么,這個看似神秘的設備究竟是如何工作的?它又是如何精準

2025-03-15 16:13:23 1047

1047

那么,究竟是什么促使創作者們選擇了Dell PowerScale?而它所具備的特性又能為影視行業帶來怎樣的價值呢?

2025-03-07 14:57:22 1029

1029 如下圖所示,這個二極管是做什么的呢?歡迎大家交流。

2025-03-06 07:00:47

,如圖電路;

結果發現在3.3V這一側,也就是RXD位置還是測到毛刺;

有誰知道這究竟是為什么嗎?

2025-03-06 06:24:41

DDR內存控制器是一個高度集成的組件,支持多種DDR內存類型(DDR2、DDR3、DDR3L、LPDDR2),并通過精心設計的架構來優化內存訪問效率。

2025-03-05 13:47:40 3573

3573

Xilinx的FIR IP核屬于收費IP,但是不需要像 Quartus那樣通過修改license文件來破解。如果是個人學習,現在網絡上流傳的license破解文件在破解Vivado的同時也破解

2025-03-01 14:44:19 2709

2709

世界移動通信大會展示了最前沿的無線產品和技術,匯聚了有史以來最先進的一些通信設備。但究竟是什么保證了這些設備在現實環境中每次都能無縫運行呢?

2025-02-25 16:43:39 884

884 生效,IO不會有高電平輸出

如果步驟3、4 之間增加一點點延時,sleep(10),Trigger Out 1才可以生效。

該問題在我們以前的板子上不存在,最近生產的板子才出現,所以想查出究竟是哪里的問題? 配置 Write Operating Mode Select 后,一般需要delay多長時間?

2025-02-21 07:23:59

據報道,業內人士透露,全球三大DRAM內存制造商——三星電子、SK海力士和美光,有望在2025年內正式停產已有多年歷史的DDR3和DDR4兩代內存。 隨著技術的不斷進步和消費級平臺的更新換代

2025-02-19 11:11:51 3465

3465 作為物聯網智能硬件的引領者,云里物里當然不是來聊電影的,而是想借此機會,和大家探討一下:室內導航究竟是如何實現的?它背后的技術原理是什么?接下來,讓我們一起揭開室內導航的神秘面紗。

2025-02-12 13:50:31 961

961

PACE_OUT1和PACE_OUT2這兩條引腿究竟是輸入還是輸出?有什么用?怎樣使用?

2025-02-12 07:56:43

;MTA9ASF1G72AZ-3G2R1是一款高性能的DDR3 SDRAM內存模塊,專為滿足現代計算需求而設計。該產品以其高帶寬和低功耗的特性,廣泛應用于個人電腦、服務器和嵌入式系統中,成為市場上備

2025-02-10 20:10:39

板子上正負10V電壓已加,USBStyx driver 已經安裝,通過母板供電,但最后 軟件界面上的Acquire 按鍵呈現灰白色,無法按下,如下圖紅圈區域所示:

有哪位能告訴我究竟是哪里出了問題?該不會是硬件壞了吧?

2025-01-22 07:54:30

) ADC 和片上傳感器。其中12位指的是ADC轉換的精度,1MSPS說的是采樣速率。如圖所示,是XADC在FPGA內部電路的邏輯示意,注意區別于IP核形成的電路。 1.圖中1部分是溫度傳感器和電壓傳感器,可監測如圖所示的多組電壓。 2.圖中2部分是FPGA bank上的引腳。可以用來接模擬源,總共有

2025-01-15 16:53:59 2235

2235

ALINX近日宣布,基于AMD 100G以太網MAC IP,成功開發出全新的100G以太網UDP/IP協議棧IP核。該IP核在數據傳輸方面表現出色,MTU支持高達9000Bytes,采用標準

2025-01-07 11:25:25 1254

1254 AI工作流自動化是指利用人工智能技術,對工作流程中的重復性、規則明確的任務進行自動化處理的過程。那么,AI工作流自動化是做什么的呢?接下來,AI部落小編為您分享。

2025-01-06 17:57:59 1581

1581

電子發燒友App

電子發燒友App

評論