本章的實驗任務是在 PL 端自定義一個 AXI4 接口的 IP 核,通過 AXI_HP 接口對 PS 端 DDR3 進行讀寫測試,讀寫的內存大小是 4K 字節。

2025-11-24 09:19:42 3467

3467

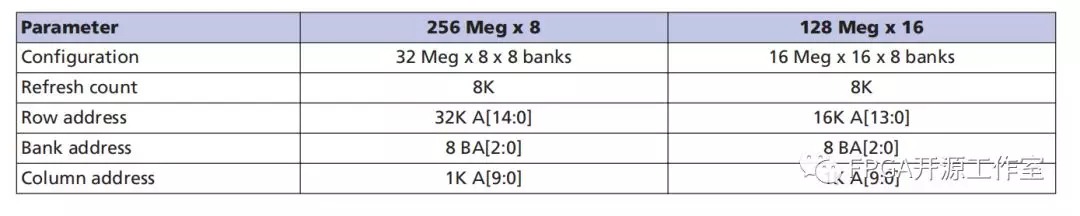

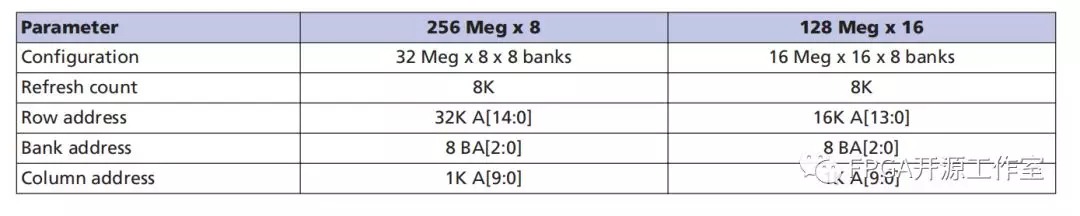

本文以Kintex-7系列XC7K410T FPGA芯片和兩片MT41J128M16 DDR3 SDRAM芯片為硬件平臺,設計并實現了基于FPGA的視頻圖形顯示系統的DDR3多端口存儲管理。##每片

2015-04-07 15:52:10 13985

13985

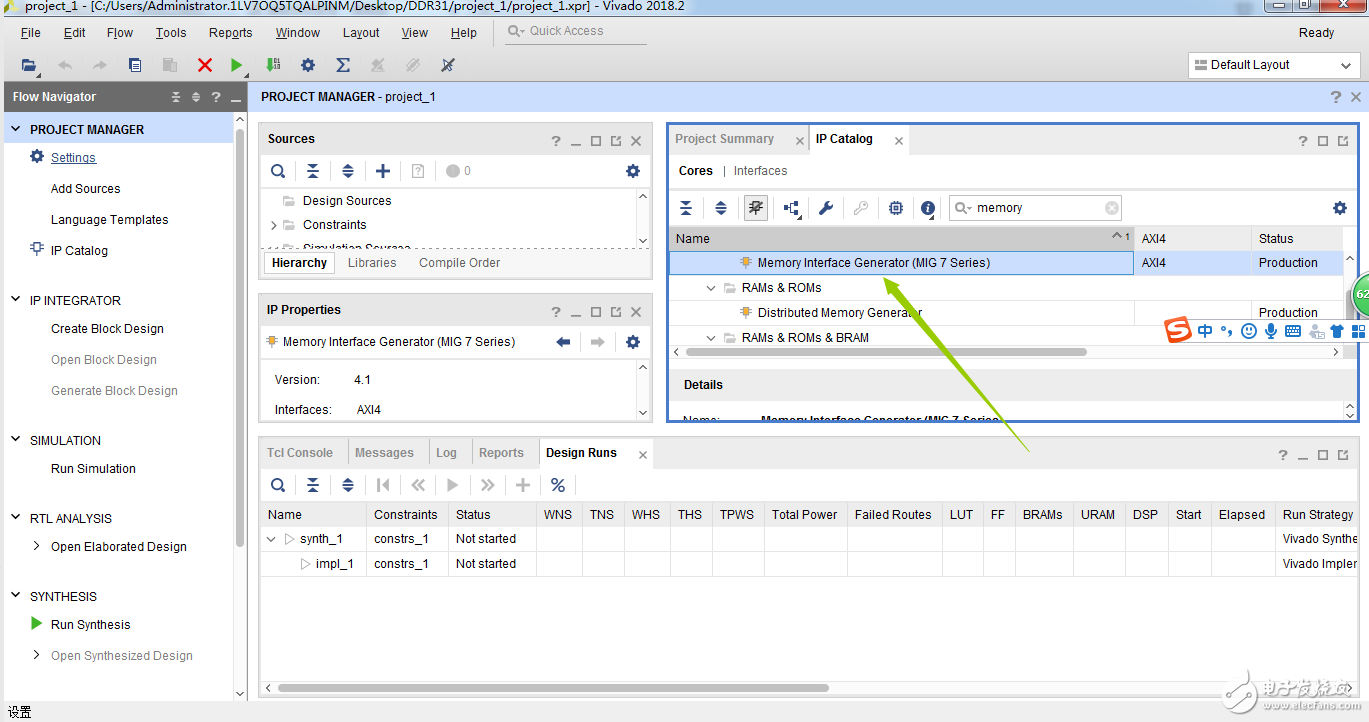

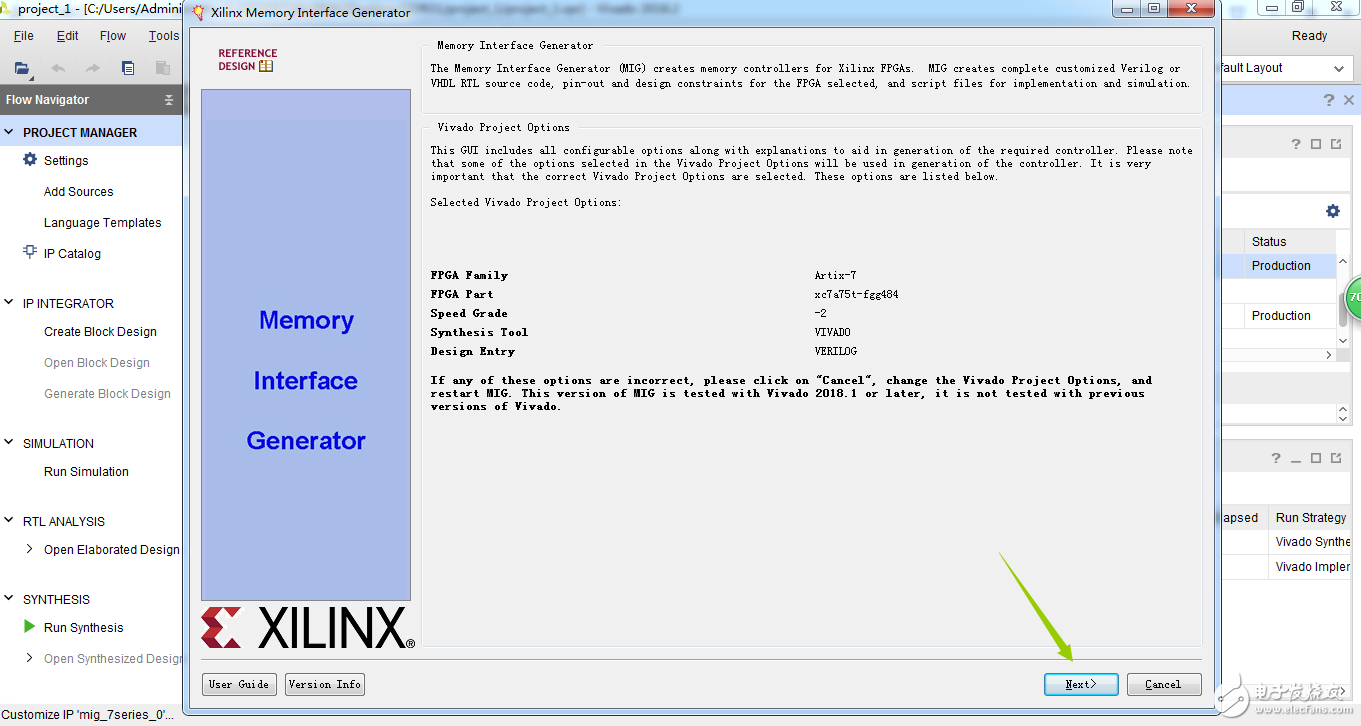

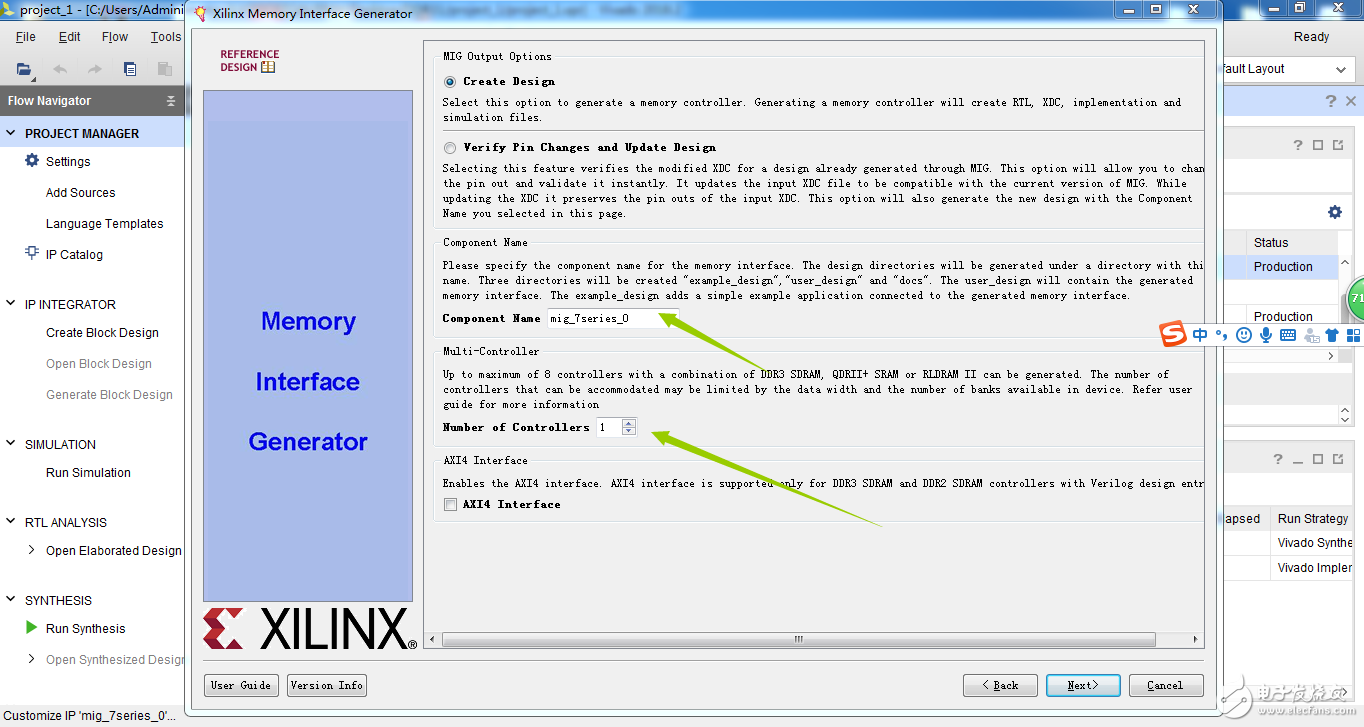

講解xilinx FPGA 使用mig IP對DDR3的讀寫控制,旨在讓大家更快的學習和應用DDR3。 本實驗和工程基于Digilent的Arty Artix-35T FPGA開發板完成。 軟件

2021-01-01 10:09:00 5266

5266

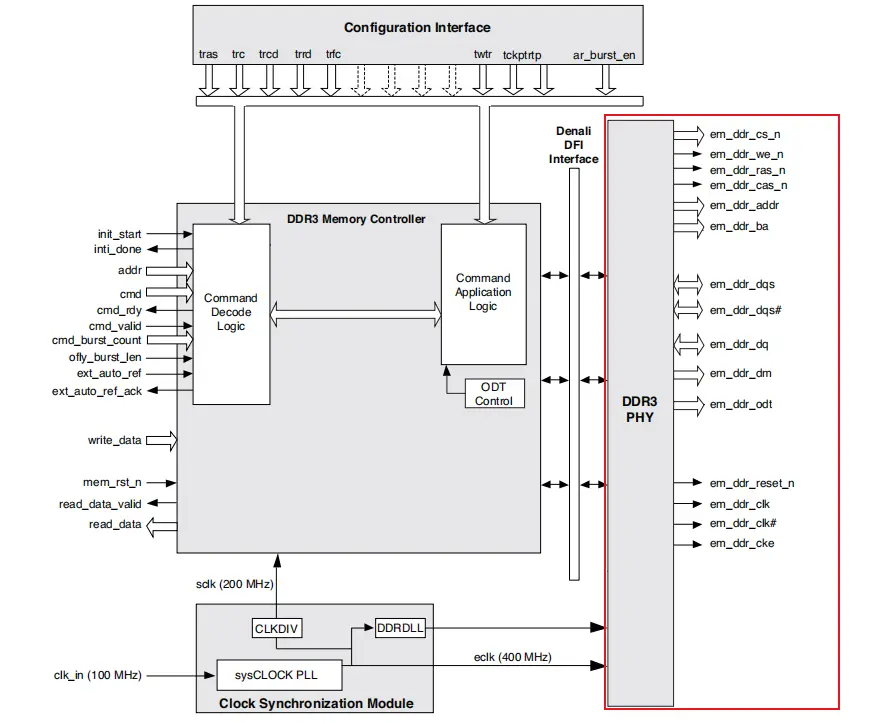

用戶端使用的,框圖如圖1所示。 如圖1 所示的中間部分為我們調取的IP 核,user FPGA Logic 為用戶端邏輯,DDR2/DDR3 SDRAM 為存儲芯片。其中IP 核與存儲芯片之間的總線大部分

2020-12-31 11:17:02 6783

6783

本實驗為后續使用DDR3內存的實驗做鋪墊,通過循環讀寫DDR3內存,了解其工作原理和DDR3控制器的寫法,由于DDR3控制復雜,控制器的編寫難度高,這里筆者介紹采用第三方的DDR3 IP控制器情況下的應用,是后續音頻、視頻等需要用到DDR3實驗的基礎。

2021-02-05 13:27:00 10988

10988

2、512Mb-2Gb LP DDR2,以及?LP DDR4x、LP DDR3、LP DDR、SDRAM,適用于需配備4Gb 或以下容量DRAM 的應用,?如人工智能加速器、物聯網、汽車、工業用、電信、

2022-04-20 16:04:03 3594

3594

DDR內存1代已經淡出市場,直接學習DDR3 SDRAM感覺有點跳躍;如下是DDR1、DDR2以及DDR3之間的對比。

2023-04-04 17:08:47 5108

5108

DDR3 SDRAM(Double-Data-Rate ThreeSynchronous Dynamic Random Access Memory)是DDR SDRAM的第三代產品,相較于DDR2,DDR3有更高的運行性能與更低的電壓。

2025-04-10 09:42:53 3930

3930

DDR31.DDR3概述DDR3內存控制器主要用于以JESD79-3C標準做SDRAM設備的外部存儲接口。支持的內存類型有DDR1 SDRAM,SDRSDRAM, SBSRAM。DDR3內存控制器

2018-01-18 22:04:33

嗨,我是FPGA領域的新手。現在我正在使用Genesys2。我必須控制DDR3內存。我在Digilent網站上找到了一些使用micrlaze處理器的DDR3示例。但是,在我的情況下,我不必

2019-05-05 15:29:38

為了實現更強大的系統操作,DDR3 SDRAM驅動器設計通過降低電容得到了增強,動態片上端接(ODT)和新的校準方案。電容減少來自于使用新的合并驅動器。使用新驅動程序,組成輸出驅動程序的電路共享用于ODT。DDR2上使用單獨的結構作為輸出驅動器和終端阻抗。

2019-05-23 08:20:56

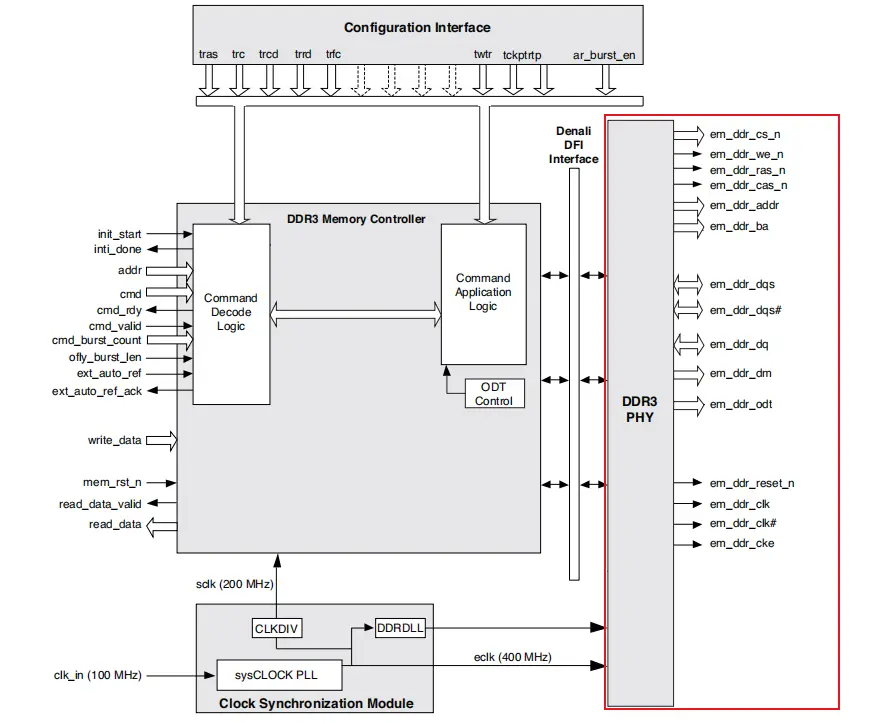

為任意或所有DDR3 SDRAM器件提供單獨的終端阻抗控制,提高了存儲器通道的信號完整性。圖2:DDR3存儲器控制器IP核框圖DDR3存儲器控制器應支持廣泛的存儲器速率和配置,以滿足各種應用需求。例如

2019-05-24 05:00:34

DDR4,DDR3,DDR2,DDR1及SDRAM有什么不同之處?

2021-03-12 06:22:08

在使用DDR3 SDRAM Controller with Uniphy ip(quartus prime 17.1 )核時卡在如下情況,無法生成(持續一晚上), 且軟件沒有報錯誤及其它提示。再換用

2018-05-14 19:29:26

因為工作的需要,最近做了下DDR3 IP核的讀寫仿真,仿真過程中DDR寫數據正常,但在對DDR讀取數據時出現以下的情況:1.MEM_DQ、MEM_DQS、MEM_DQSN始終為高阻態

2019-12-26 23:11:56

DDR3 SDRAM內存的總線速率達到600 Mbps to 1.6 Gbps (300 to 800 MHz),1.5V的低功耗工作電壓,采用90nm制程達到2Gbits的高密度。這個架構毫無疑問

2019-04-22 07:00:08

FPGA選用alter公司的cyclone V系列,DDR3外接2片,程序調用DDR3 ip核UniPHY,程序綜合編譯沒有問題,只配置了幾個引腳定義,就出現了如下錯誤:Error (14566

2018-04-16 16:35:13

=1.5V;但我看了一篇FPGA的DDR3 IP核例化文章,上面寫FPGA的BANK1,3連接外部存儲控制器(如下圖,且只有四個BANK),所以要將DDR3連接在BANK3上。所以DDR3如何與FPGA芯片

2021-11-29 16:10:48

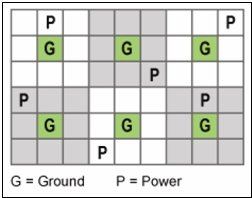

如果沒有將均衡功能直接設計到FPGA I/O架構中,那么任何設備連接到DDR3 SDRAM DIMM都將是復雜的,而且成本還高,需要大量的外部元器件,包括延時線和相關的控制。

2019-08-21 07:21:29

流程。下圖所示是7系列的MIG IP核結構圖。MIG IP核對外分出了兩組接口,左側是用戶接口,右側是DDR物理芯片接口,負責產生具體的操作時序,并直接操作芯片管腳。

DDR3的讀寫都包含寫命令操作

2025-10-21 10:40:28

求助大神!!!FPGA對于DDR3讀寫,FPGA是virtex6系列配置MIG IP 核時,需要管腳分配1.原理圖上dm是直接接地,管腳分配那里該怎么辦2.系統時鐘之類的管腳分配,是需要在原理圖上找FPGA與DDR3之間的連線嗎?還是?

2018-03-16 18:45:10

我DDR3 IP核設置了兩套avalon端口,端口0只寫 端口1只讀;我得工作流程是:端口0寫完整一幀數據到DDR3,大約15ms,然端口1開始讀這一幀數據大約需要25ms;但是我的幀周期是35ms

2019-06-19 10:41:29

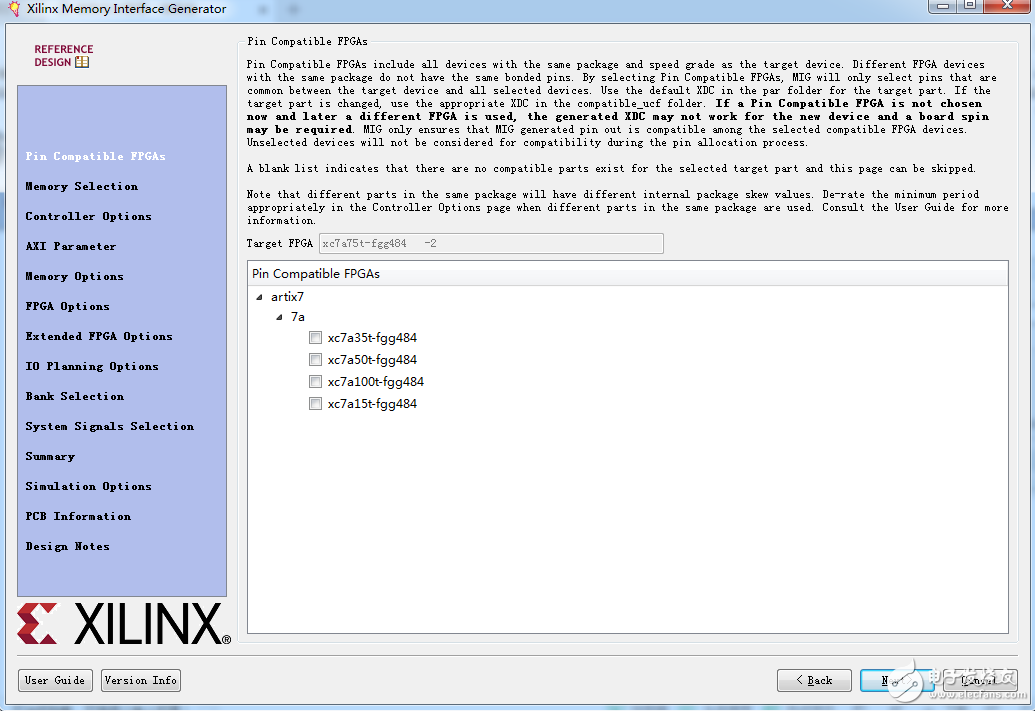

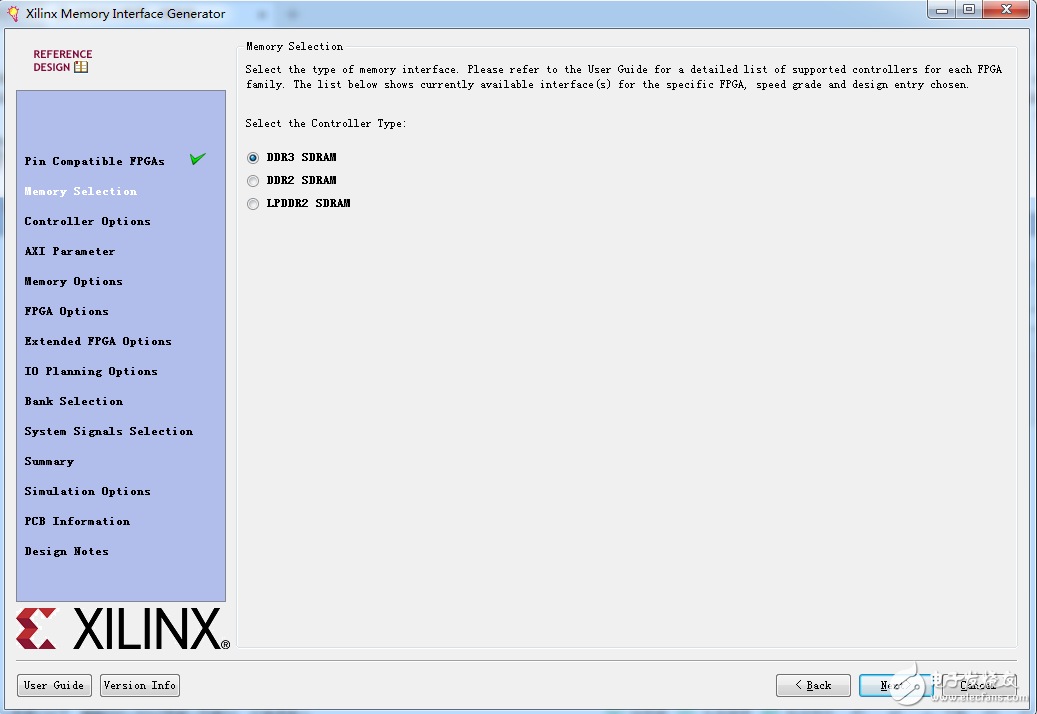

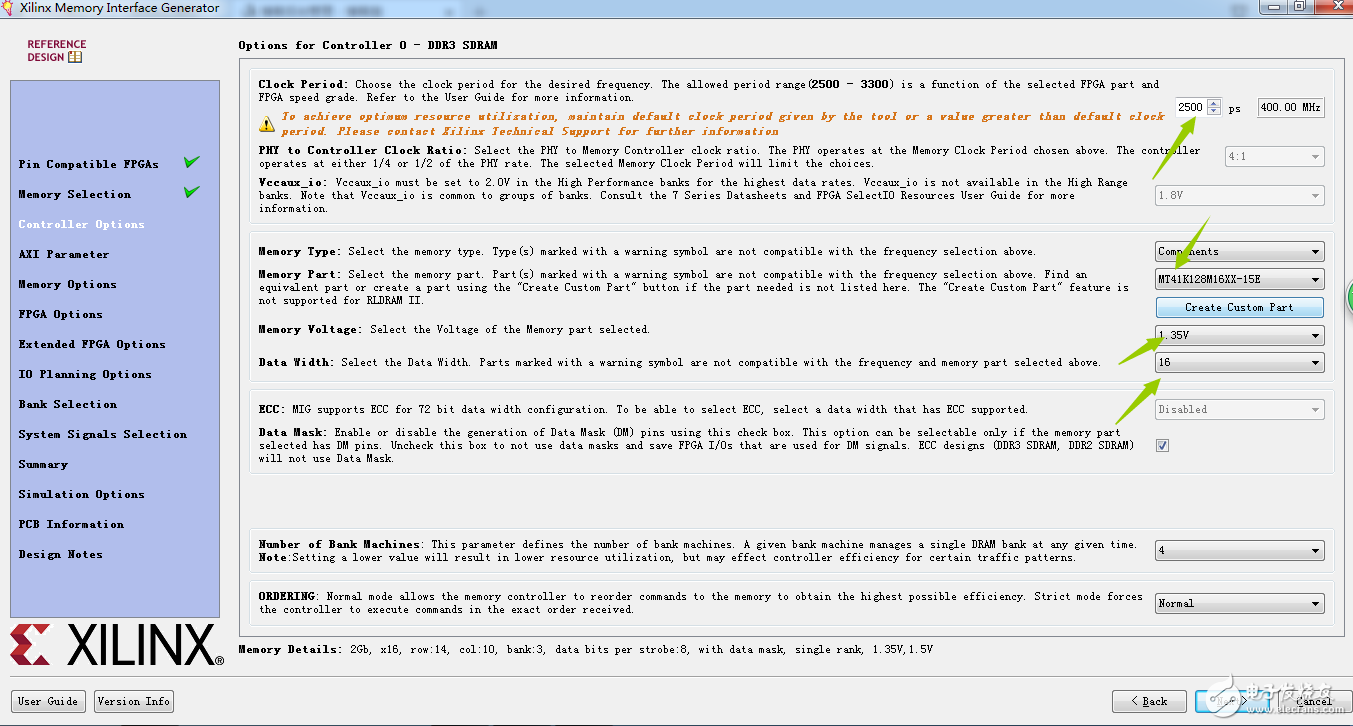

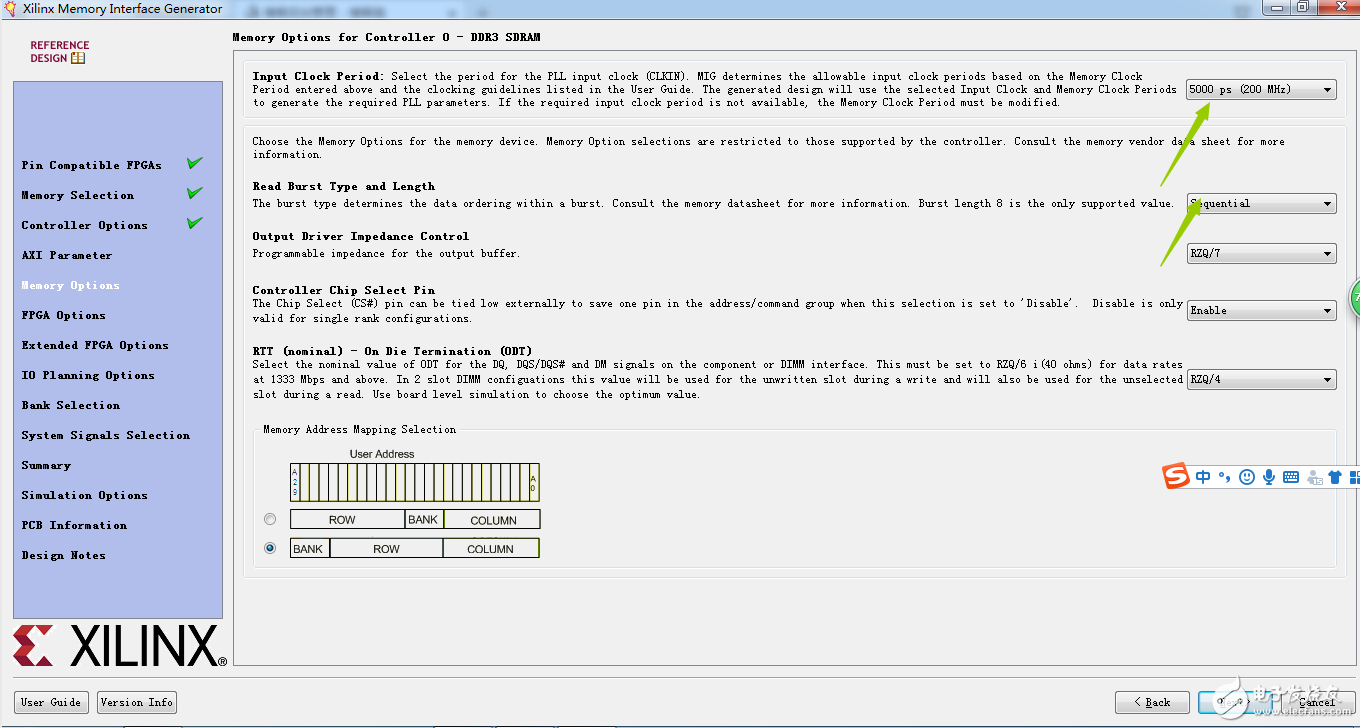

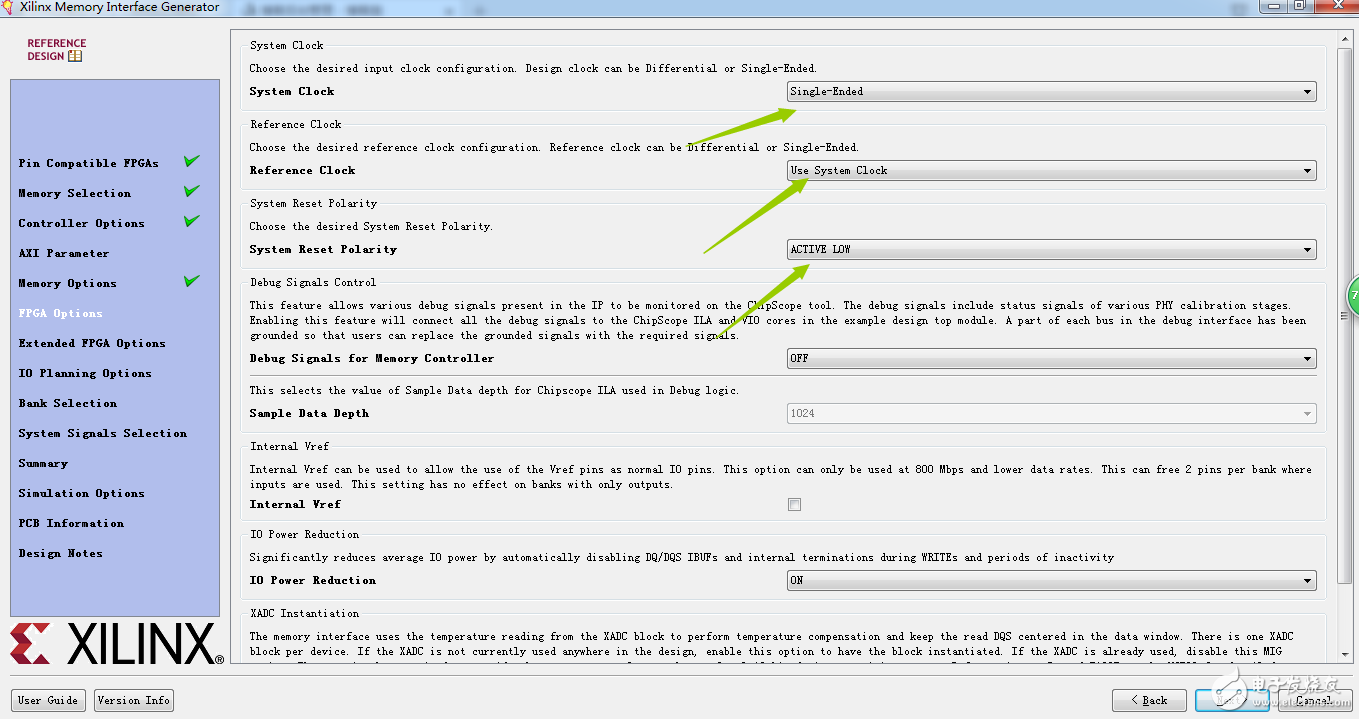

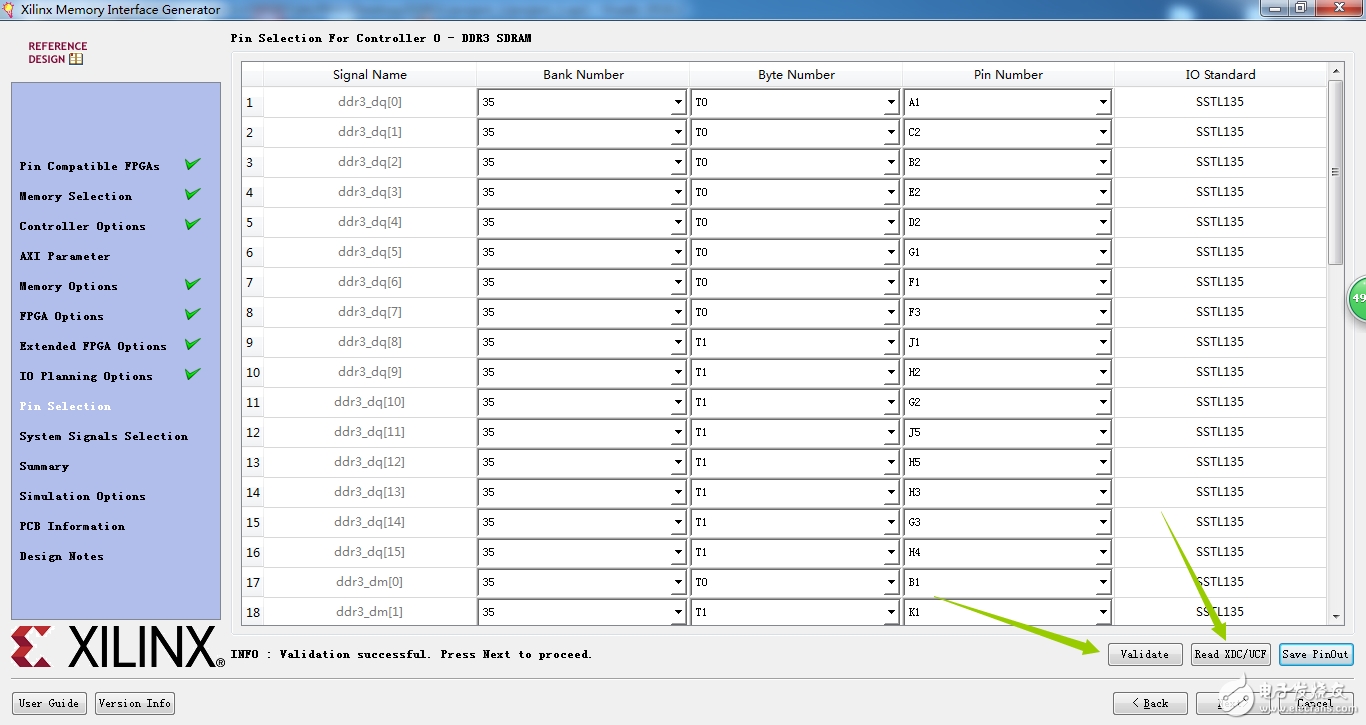

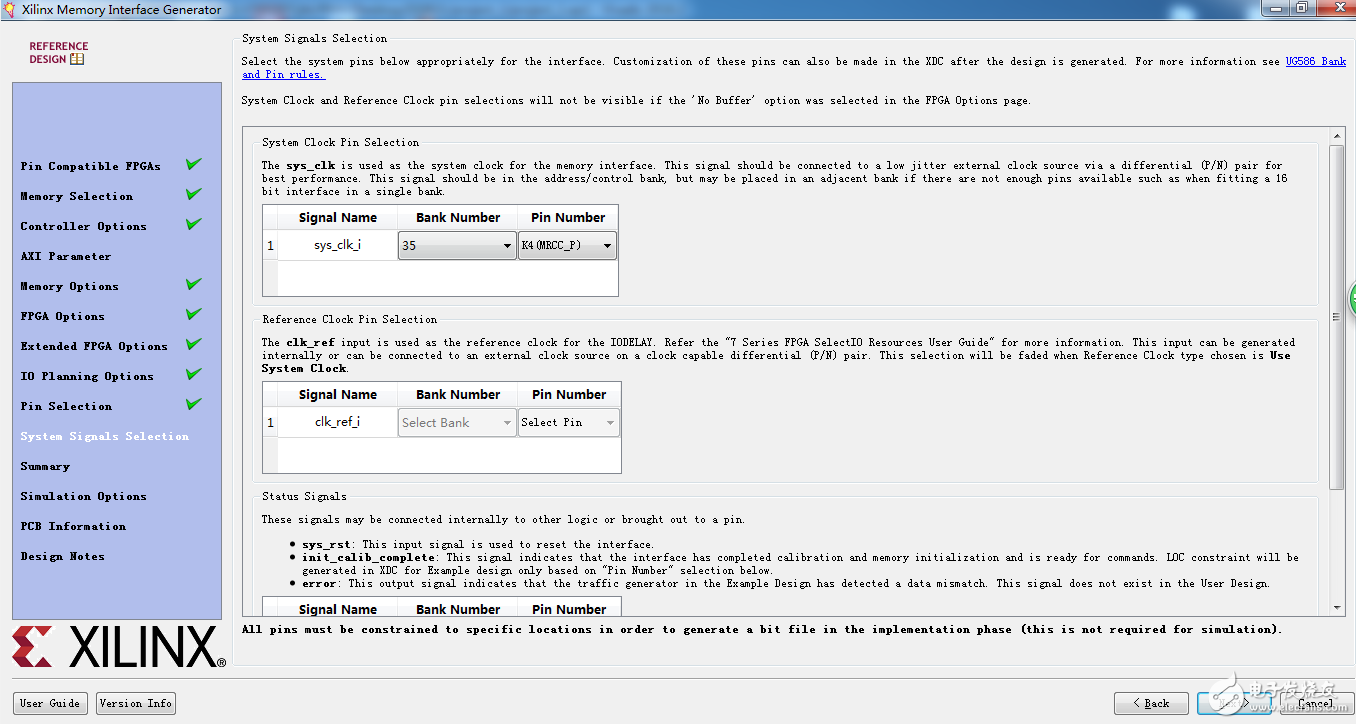

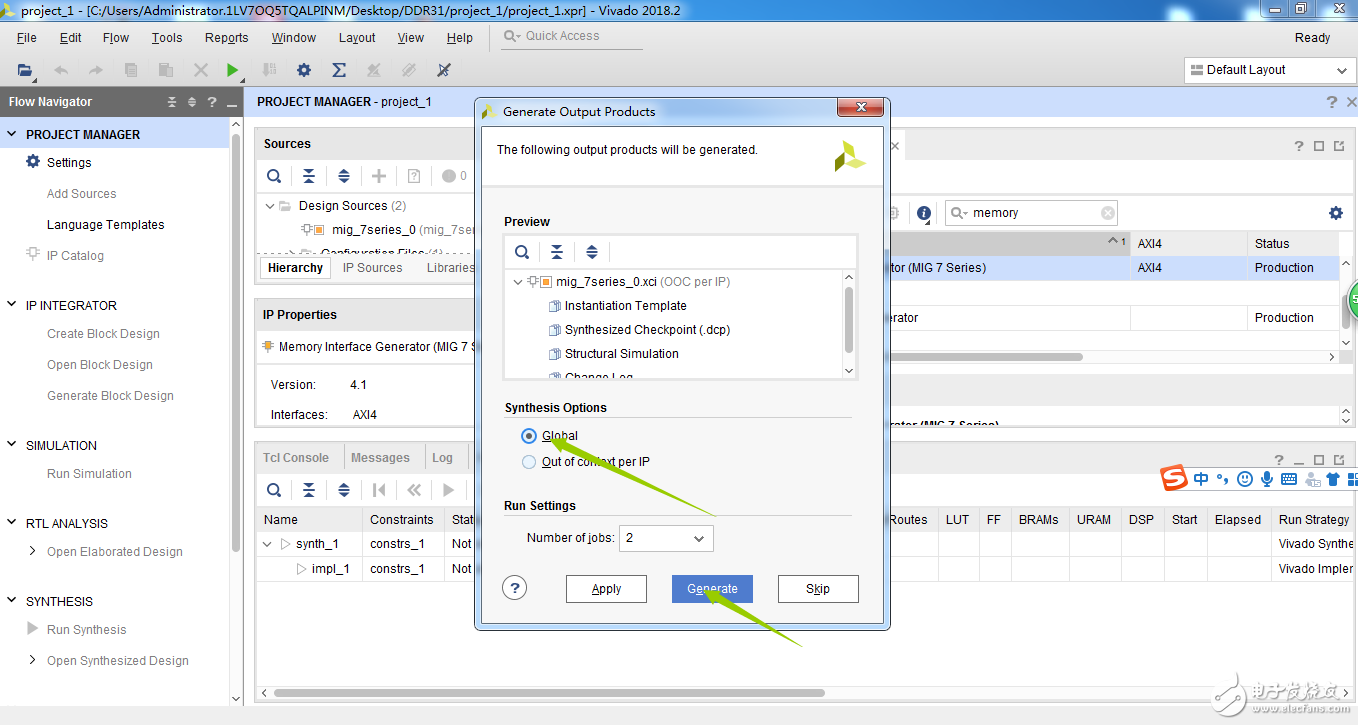

”。13.點擊“Generate”生成MIG控制器。四、生成文檔點擊“Generate”,生成MIG控制器相關的設計文檔。以上就是基于Xilinx 的K7 DDR3 IP核的生成配置過程。

2019-12-19 14:36:01

大家好,應用altera Cyclone V外接DDR3,啟用HMC實現硬核控制,IP核在設計生成時出現如下錯誤:Error: Error during execution of script

2018-04-25 10:28:52

RASn,CASn等,是IP核自動產生的么?要如何配置條件,給DDR3寫入數據并讀取DDR3的數據,謝謝,現在頭緒不清,第一次做,拜托各位解惑了

2016-01-14 18:15:19

請教各位大神,小弟剛學FPGA,現在在用spartan-3E的板子,想用上面的DDR SDRAM進行簡單的讀寫,用MIG生成DDR核之后出現了很多引腳,看了一些資料也不是很清楚,不知道怎么使用生成的這個IP核控制器來進行讀寫,希望大神們稍作指點

2013-06-20 20:43:56

`本開發板板載了一片高速 DDR3 SDRAM, 型號:MT41J128M16JT-093, 容量:256MByte(128M*16bit),16bit 總線。開發板上 FPGA 和 DDR3

2021-07-30 11:23:45

的總線寬度共為 16bit。DDR3 SDRAM 的最高數據速率 1066Mbps。

2.1. DDR3 控制器簡介

PG2L50H 為用戶提供一套完整的 DDR memory 控制器解決方案,配置

2025-07-10 10:46:48

后點擊“OK”:四、配置IP核在配置界面,“Memory Protocol”選擇“DDR3”;在“General”頁面“Clocks”“Memory clock frequency”配置DDR的速率為

2019-12-19 10:16:43

為任意或所有DDR3 SDRAM器件提供單獨的終端阻抗控制,提高了存儲器通道的信號完整性。圖2:DDR3存儲器控制器IP核框圖DDR3存儲器控制器應支持廣泛的存儲器速率和配置,以滿足各種應用需求。例如

2019-05-27 05:00:02

IP DDR3控制器 RISC-V

基于DDR200T開發板原理圖,找到所需要使用的DDR引腳,制成DDR.ucf文件方便在添加管腳約束時使用。在使用MIG IP核時,為了方便使用DDR產生的時鐘

2025-10-21 12:43:40

進行了DDR3 SDRAM控制器的編寫,分析并提出了提高帶寬利用率的方法。最終將其進行類FIFO接口的封裝,屏蔽掉了DDR3 IP核復雜的用戶接口,為DDR3數據流緩存的實現提供便利。系統測試表明,該

2018-08-02 09:34:58

優仲裁模塊、讀寫邏輯控制模塊和DDR3存儲器控制模塊。DDR3存儲控制器模塊采用Xilinx公司的MIG核,用戶只需要通過IP核的GUI選擇內存芯片并進行相關參數設置,即可完成DDR3的配置工作[6

2018-08-02 09:32:45

Xilinx Virtex-6系列FPGA中使用MIG3.7 IP核實現高速率DDR3芯片控制的設計思想和設計方案。針對高速實時數字信號處理中大容量采樣數據通過DDR3存儲和讀取的應用背景,設計和實現了

2018-08-30 09:59:01

DDR讀寫操作的控制流程。下圖所示是7系列的MIG IP核結構圖。MIG IP核對外分出了兩組接口,左側是用戶接口,右側是DDR物理芯片接口,負責產生具體的操作時序,并直接操作芯片管腳。

DDR3的讀寫

2025-10-21 14:30:16

選擇。視頻處理和圖形生成需要存儲海量數據,FPGA內部的存儲資源無法滿足存儲需求,因此需要配置外部存儲器。與DDR2 SDRAM相比,DDR3 SDRAM帶寬更好高、傳輸速率更快且更省電,能夠滿足

2019-06-24 06:07:53

均衡的定義和重要性是什么如何實現FPGA和DDR3 SDRAM DIMM條的接口設計?

2021-05-07 06:21:53

,以及對應的波形圖和 Verilog HDL 實現。我們調取的 DDR3 SDRAM 控制器給用戶端預留了接口,我們可以通過這些預留的接口總線實現對該 IP 核的控制,本章節將會講解如何根據

2022-02-08 07:08:01

大家好 我的問題是DDR3校準完成失敗。調試結果:dbg_wrcal_err = 1,通過波形,我們可以看到寫入模式不匹配。 我的問題是MIG IP Core配置中是否有任何參數可以調整它?或者我

2020-07-23 10:09:37

的控制流程。下圖所示是7系列的MIG IP核結構圖。MIG IP核對外分出了兩組接口,左側是用戶接口,右側是DDR物理芯片接口,負責產生具體的操作時序,并直接操作芯片管腳。

DDR3的讀寫都包含寫

2025-10-21 08:43:39

Write Leveling 和 DQS Gate Training

?DDR3 最快速率達 800 Mbps

三、實驗設計

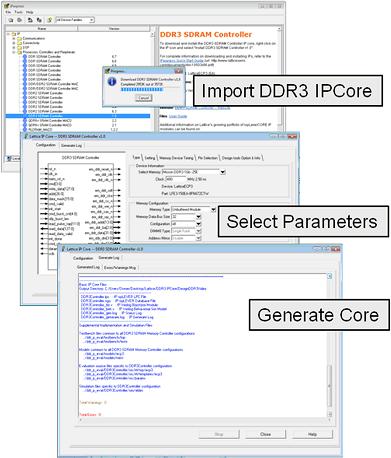

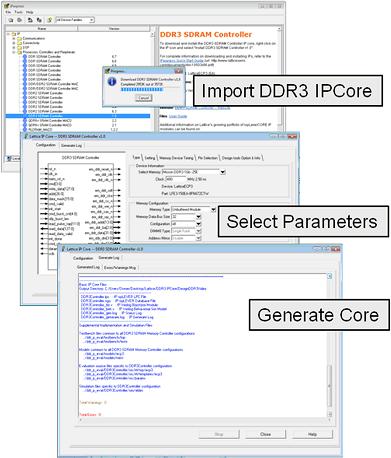

a. 安裝 DDR3 IP 核

PDS 安裝后,需手動添加 DDR3 IP,請按

2023-05-19 14:28:45

和 DQS Gate Training

?DDR3 最快速率達 800 Mbps

三、實驗設計

a. 安裝 DDR3 IP 核

PDS 安裝后,需手動添加 DDR3 IP,請按以下步驟完成:

(1

2023-05-31 17:45:39

我需要在V7中實現與DDR3 SDRAM相同的功能和接口。這意味著命令/地址,讀取數據和寫入數據流的方向與MIG的方向不同。這可以實現嗎?

2020-07-14 16:18:04

本文介紹了DDR3 SDRAM 的基本特點和主要操作時序,給出了一種基于ALTMEMPHY宏功能的DDR3 SDRAM控制器的設計方法。詳述了控制器基本結構和設計思想,分析了各模塊功能與設計注意事項,并

2010-07-30 17:13:55 30

30 不只計算機存儲器系統一直需要更大、更快、功率更低、物理尺寸更小的存儲器,嵌入式系統應用也有類似的要求。本應用指南介紹了邏輯分析儀在檢驗DDR, DDR2 和DDR3 SDRAM 命令和

2010-08-06 08:29:49 81

81 Quamtum-SI DDR3仿真解析

Automated DDR3 Analysis

2010-04-29 09:00:11 4760

4760

DDR3存儲器系統可以大大提升各種數據處理應用的性能。然而,和過去幾代(DDR和DDR2)器件相比,DDR3存儲器器件有了一些新的要求。為了充分利用和發揮DDR3存儲器的優點,使用一

2010-07-16 10:46:05 2064

2064

采用90nm工藝制造的DDR3 SDRAM存儲器架構支持總線速率為600 Mbps-1.6 Gbps (300-800 MHz)的高帶寬,工作電壓低至1.5V,因此功耗小,存儲密度更可高達2Gbits。該架構無疑速度更快,容量

2010-11-07 10:39:57 4472

4472

從那時起,采用DDR2、甚至最新的DDR3 SDRAM的新設計讓DDR SDRAM技術黯然失色。DDR內存主要以IC或模塊的形式出現。如今,DDR4雛形初現。但是在我們利用這些新技術前,設計人員必須了解如何

2011-07-11 11:17:14 6408

6408

SDRAM, DDR, DDR2, DDR3 是RAM 技術發展的不同階段, 對于嵌入式系統來說, SDRAM 常用在低端, 對速率要求不高的場合, 而在DDR/DDR2/DDR3 中,目前基本上已經以DDR2 為主導,相信不久DDR3 將全面取代

2012-01-16 14:53:01 0

0 用ise工具調用DDR3 IP核教程,內容非常的詳細

2015-11-20 11:56:20 0

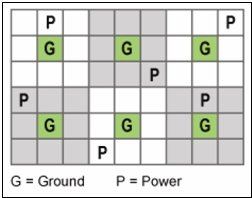

0 UltraScale架構PCB設計用戶指導手冊(UG583)會給你提供很多不同的設計建議,頁數多達122頁。當然不僅僅局限于存儲器的連接設計,我發現對于DDR3與DDR4 SDRAM的連接設計也特別的有意思

2017-02-08 10:04:09 2134

2134

和PL端的Master IP核,共同訪問操作一個Slave端即DDR3 Controllor。 本次實驗就是構建一個這樣的驗證系統。當然了在真正的工程系統中,還需要設計良好的讀寫同步,防止競爭沖突,這就屬于系統設計層面的了,本實驗依靠按鈕觸發有用戶來進行讀寫同步。

2017-09-15 16:35:01 25

25 DDR3是目前DDR的主流產品,DDR3的讀寫分離作為DDR最基本也是最常用的部分,本文主要闡述DDR3讀寫分離的方法。最開始的DDR, 芯片采用的是TSOP封裝,管腳露在芯片兩側的,測試起來相當方便;但是,DDRII和III就不一樣了,

2017-11-06 13:44:10 9412

9412

雖然新一代電腦/智能手機用上了DDR4內存,但以往的產品大多還是用的DDR3內存,因此DDR3依舊是主流,DDR4今后將逐漸取代DDR3,成為新的主流,下面我們再來看看DDR4和DDR3內存都有哪些區別。相比上一代DDR3,新一代DDR4內存主要有以下幾項核心改變:

2017-11-08 15:42:23 32469

32469 為解決超高速采集系統中的數據緩存問題,文中基于Xilinx Kintex-7 FPGA MIG_v1.9 IP核進行了DDR3 SDRAM控制器的編寫,分析并提出了提高帶寬利用率的方法。最終將其進行

2017-11-16 14:36:41 25160

25160

DDR3 SDRAM(Double Data Rate Three SDRAM):為雙信道三次同步動態隨機存取內存。

DDR4 SDRAM(Double Data Rate Fourth

2017-11-17 13:15:49 28010

28010 為了滿足高速圖像數據采集系統中對高帶寬和大容量的要求,利用Virtex-7 系列FPGA 外接DDR3 SDRAM 的設計方法,提出了一種基于Verilog-HDL 語言的DDR3 SDRAM

2017-11-17 14:14:02 4071

4071

為了解決視頻圖形顯示系統中多個端口訪問DDR3的數據存儲沖突,設計并實現了基于FPGA的DDR3存儲管理系統。DDR3存儲器控制模塊使用MIG生成DDR3控制器,只需通過用戶接口信號就能完成DDR3

2017-11-18 18:51:25 7989

7989

DRAM (動態隨機訪問存儲器)對設計人員特別具有吸引力,因為它提供了廣泛的性能,用于各種計算機和嵌入式系統的存儲系統設計中。本文概括闡述了DRAM 的概念,及介紹了SDRAM、DDR SDRAM、DDR2 SDRAM、DDR3 SDRAM、DDR4 SDRAM、LPDDR、GDDR。

2018-06-07 22:10:00 95076

95076 DR3 在高頻時數據出現了交錯,因此,高速DDR3存儲器設計有一定的難度。如果FPGA I/O 結構中沒有直接內置調平功能,那么連接DDR3 SDRAM DIMM的成本會非常高,而且耗時,并且需要

2018-06-22 02:04:00 4421

4421 我們通過Configuration,Package,Speed...等DDR3的命名可知道DDR3的容量,封裝,速度等級等信息。

2019-03-03 11:04:15 2626

2626

SDRAM在計算機中被廣泛使用,從起初的SDRAM到之后一代的DDR(或稱DDR1),然后是DDR2和DDR3進入大眾市場,2015年開始DDR4進入消費市場。

2019-09-26 07:02:00 2717

2717

DDR3 SDRAM是DDR3的全稱,它針對Intel新型芯片的一代內存技術(但目前主要用于顯卡內存),頻率在800M以上。DDR3是在DDR2基礎上采用的新型設計,與DDR2 SDRAM相比具有功耗和發熱量較小、工作頻率更高、降低顯卡整體成本、通用性好的優勢。

2019-10-29 08:00:00 0

0 本文件定義了DDR3 SDRAM規范,包括特性、功能、交直流特性、封裝和球/信號分配。本文檔的目的是為符合jedec的512 MB到8 GB的x4、x8和x16 ddr3 sdram設備定義一組最低

2019-11-04 08:00:00 96

96 本文檔的主要內容詳細介紹的是DDR和DDR2與DDR3的設計資料總結包括了:一、DDR的布線分析與設計,二、DDR電路的信號完整性,三、DDR Layout Guide,四、DDR設計建議,六、DDR design checklist,七、DDR信號完整性

2020-05-29 08:00:00 0

0 從成本的角度來看,DDR3也許的確要比DDR4低一些,所以從這個角度可以講通。

2020-09-08 16:28:23 5265

5265 4Gb DDR3 SDRAM E-die是一個32Mbit x 16 I/Os x 8個存儲單元的設備。這種同步設備實現高速雙數據傳輸率高達2133Mb/秒/引腳(DDR3-2133)的一般應用。該

2021-01-22 08:00:00 13

13 這篇文章我們講一下Virtex7上DDR3的測試例程,Vivado也提供了一個DDR的example,但卻是純Verilog代碼,比較復雜,這里我們把DDR3的MIG的IP Core掛在Microblaze下,用很簡單的程序就可以進行DDR3的測試。

2021-05-02 09:05:00 4228

4228

DDR,DDR2,DDR3,DDR4,LPDDR區別作者:AirCity 2019.12.17Aircity007@sina.com 本文所有權歸作者Aircity所有1 什么是DDRDDR

2021-11-10 09:51:03 163

163 ,以及對應的波形圖和 Verilog HDL 實現。我們調取的 DDR3 SDRAM 控制器給用戶端預留了接口,我們可以通過這些預留的接口總線實現對該 IP 核的控制,本章節將會講解如何根據 Xilinx 官方提供的技術參數來實現對 IP 核的寫控制。寫命令和寫數據總線介紹DDR3 SDRAM控制器I

2021-12-04 19:21:05 4

4 車載視頻拼接的項目,該項目使用到了LVDS高速接口和DDR3接口,攝像頭采集的視頻圖像數據需要先存入DDR3中然后與通過LVDS傳輸的主機視頻數據進行拼接輸出,最終在屏幕上顯示畫中畫的效果。分享給大家

2022-03-14 14:46:06 1212

1212

本文以一個案例的形式來介紹lattice DDR3 IP核的生成及調用過程,同時介紹各個接口信號的功能作用

2022-03-16 14:14:19 2713

2713

本申請說明中提供的設計指南適用于利用DDR3 SDRAM IP核的產品,它們基于內部平臺的匯編由飛思卡爾半導體公司設計這些指導方針旨在最大限度地減少與董事會相關的問題多內存拓撲,同時允許最大董事會設計師的靈活性。

2022-03-31 15:28:58 0

0 日前,世界著名硬件網站TomsHardware上有消息表示,多家大廠都在考慮停止DDR3內存的生產。DDR3內存早在2007年就被引入,至今已長達15年,因為其不再泛用于主流平臺,即便退出市場也不會

2022-04-06 12:22:56 6223

6223 ??這篇文章我們講一下Virtex7上DDR3的測試例程,Vivado也提供了一個DDR的example,但卻是純Verilog代碼,比較復雜,這里我們把DDR3的MIG的IP Core掛在Microblaze下,用很簡單的程序就可以進行DDR3的測試。

2022-08-16 10:28:58 3160

3160 電子發燒友網站提供《Gowin DDR3 Memory Interface IP用戶指南.pdf》資料免費下載

2022-09-15 14:39:09 1

1 一、DDR3簡介 ? ? ? ? DDR3全稱double-data-rate 3 synchronous dynamic RAM,即第三代雙倍速率同步動態隨機存儲器。所謂同步,是指DDR3數據

2022-12-21 18:30:05 5149

5149 DDR3 SDRAM使用雙倍數據速率架構來實現高速操作。雙倍數據速率結構是一種8n預取架構,其接口經過設計,可在I/O引腳上每個時鐘周期傳輸兩個數據字。DDR3 SDRAM的單個讀或寫操作有效地包括

2023-02-06 10:12:00 14

14 視頻圖形顯示系統理想的架構選擇。視頻處理和圖形生成需要存儲海量數據,FPGA內部的存儲資源無法滿足存儲需求,因此需要配置外部存儲器。 ??? 與DDR2 SDRAM相比,DDR3 SDRAM帶寬更好高、傳輸速率更快且更省電,能夠滿足吞吐量大、功耗低的需求,因此

2023-06-08 03:35:01 2788

2788 本文開源一個FPGA項目:基于AXI總線的DDR3讀寫。之前的一篇文章介紹了DDR3簡單用戶接口的讀寫方式:《DDR3讀寫測試》,如果在某些項目中,我們需要把DDR掛載到AXI總線上,那就要通過MIG IP核提供的AXI接口來讀寫DDR。

2023-09-01 16:20:37 7275

7275

本文介紹一個FPGA開源項目:DDR3讀寫。該工程基于MIG控制器IP核對FPGA DDR3實現讀寫操作。

2023-09-01 16:23:19 3353

3353

DDR3是2007年推出的,預計2022年DDR3的市場份額將降至8%或以下。但原理都是一樣的,DDR3的讀寫分離作為DDR最基本也是最常用的部分,本文主要闡述DDR3讀寫分離的方法。

2023-10-18 16:03:56 1889

1889

DDR4和DDR3內存都有哪些區別? 隨著計算機的日益發展,內存也越來越重要。DDR3和DDR4是兩種用于計算機內存的標準。隨著DDR4內存的逐漸普及,更多的人開始對兩者有了更多的關注。 DDR3

2023-10-30 09:22:00 13835

13835 DDR內存與SDRAM的區別 1. 定義與起源 SDRAM (Synchronous Dynamic Random Access Memory) :同步動態隨機存取存儲器,是一種早期的內存技術,它與

2024-11-29 14:57:27 5087

5087 DDR3、DDR4、DDR5是計算機內存類型的不同階段,分別代表第三代、第四代和第五代雙倍數據速率同步動態隨機存取存儲器(SDRAM)。以下是它們之間的性能對比: 一、速度與帶寬 DDR3 :速度

2024-11-29 15:08:28 19706

19706 燦芯半導體(上海)股份有限公司(燦芯股份,688691)宣布推出基于28HKD 0.9V/2.5V 平臺的DDR3/4, LPDDR3/4 Combo IP。該IP具備廣泛的協議兼容性,支持DDR3

2025-03-21 16:20:03 984

984 電子發燒友網站提供《DDR3 SDRAM參考設計手冊.pdf》資料免費下載

2025-11-05 17:04:01 4

4

電子發燒友App

電子發燒友App

評論