大家好,歡迎Vivado的一個快速演示,它是xilinx新的設計套件,應用到7系列和以上的系列器件。

2012-04-25 08:55:55 3049

3049 Xilinx的FIR IP核屬于收費IP,但是不需要像 Quartus那樣通過修改license文件來破解。如果是個人學習,現在網絡上流傳的license破解文件在破解Vivado的同時也破解

2025-03-01 14:44:19 2709

2709

你好,我在使用Xilinx網站的IP核時遇到了一些問題。我已經下載了Vivado Webpack,也為此同時下載了IP-Core的許可證。Vivado Webpack工作正常,但我看不到我下載

2018-12-24 13:50:01

發生IP核鎖定,一般是Vivado版本不同導致的,下面介紹幾種方法: 1 常用的方法 1)生成IP核的狀態報告 Report -》 Report IP Status 2)點擊

2021-01-08 17:12:52

在模擬模型方面,Vivado提供的IP似乎有一些根本性的變化。在將工作設計從ISE 14.4轉換為Vivado 2013.2之后,然后按照建議的方式升級大部分Xilinx IP,例如基本乘法器,除法

2019-02-26 10:42:23

——點評:Vivado界面清爽,流程清晰,完敗Q2。再也不會因ISE的低集成度,再在各組件中調來調去了。2、加入代碼——點評:Add Source無明顯區別。3、添加IP核——點評:由于core gen

2021-01-08 17:07:20

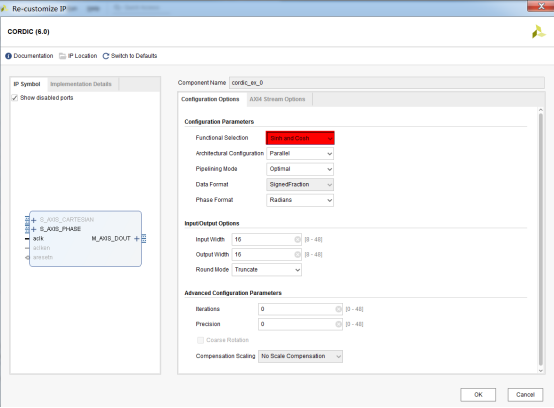

Vivado中xilinx_courdic IP核(求exp指數函數)使用

2021-03-03 07:35:03

Vivado浮點數IP核的一些設置注意點

我們在vivado2018.3中使用了Floating-point(7.1)IP核,可以自定義其計算種類及多模式選擇。有時多種計算可以用同一個IP核實

2025-10-24 06:25:22

Vivado浮點數IP核的握手信號

我們的設計方案中,FPU計算單元將收到的三條數據和使能信號同步發給20多個模塊,同時只有一個模塊被時鐘使能,進行計算,但結果都會保留,發給數選。計算單元還需接受

2025-10-24 07:01:36

在vivado生成ip核后缺少一大片文件,之前是可以用的,中途卸載過Modelsim,用vivado打開過ISE工程,因為工程中很多IP核不能用所以在重新生成過程中發現了這個問題,還請大神告知是怎么回事?

2023-04-24 23:42:21

你好,我們在2016年3月購買了Xilinx-Vivado / Ise的完整版本。我的同事將我添加為“管理員”,因此我也可以創建許可證。但它沒有顯示在我的xilinx帳戶中,因此我無法生成許可證。我

2018-12-21 11:00:57

`Xilinx系列FPGA芯片IP核詳解(完整高清書簽版)`

2017-06-06 13:15:16

各位大神,請教一個問題。目前正在使用Xilinx新出的Vivado 軟件生成DMA和PCIE集成的IP核,在此基礎上又生成了一個example design,但是在仿真的時候報錯。是Xilinx的這款產品不夠成熟還是我操作有錯誤??各位大神有沒有遇到此類問題的??

2017-01-13 21:56:41

,int b);最后經過編譯可以生成VHDL等硬件描述文件與IP核文件.我想調用自己寫的IP核(add函數)我在vivado 中添加了自定義IP核與PS(處理系統)我知道網上說用AXI Steam? 來連接

2016-01-28 18:40:28

,int b);最后經過編譯可以生成VHDL等硬件描述文件與IP核文件.我想調用自己寫的IP核(add函數)我在vivado 中添加了自定義IP核與PS(處理系統)我知道網上說用AXI Steam? 來連接

2016-01-28 18:39:13

大家伙,又到了每日學習的時間了,今天咱們來聊一聊vivado 調用IP核。首先咱們來了解一下vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如

2018-05-15 12:05:13

vivado的三速以太網IP核接口太多了,完全不知道應該怎么用,哪位大佬能發我一份設計或者仿真嗎?簡單的就好

2021-04-15 12:58:00

請教一下,vivado怎么把帶ip核的工程進行封裝,保證代碼不可見,可以通過端口調用。我嘗試了以下方法,ippackage,如果要在另一個程序里調用,也要提供源代碼;另一個方法是將網表文件edf文件與端口聲明結合,這種方法只能實現不帶ip核的封裝

2017-07-14 09:18:30

運算器等)、信號處理(FFT、DFT、DDS等)。IP核類似編程中的函數庫(例如C語言中的printf()函數),可以直接調用,非常方便,大大加快了開發速度。今天介紹的是vivado的三種常用IP核:...

2021-07-29 06:07:16

邏輯,例化了一個bRAM的ip核 ;2.封裝ip:選擇固定文件路徑進行封裝3.在封裝ip界面調了一個相同的bram的IP核 ,封裝完成;4.下面在編譯和仿真的時候就會報錯說 找不到這個bramIP核 請有這方面經驗的吧友幫忙解答一下該怎么做?

2018-12-11 10:25:41

用vivado2019.2建立工程,工程中調用cordic IP核進行atan求解,功能仿真時正常且滿足要求;綜合時正常;實現時報錯提示多重驅動。

如果經cordic計算后的輸出值不用于后續的操作

2023-06-06 17:17:37

用的xilinx的FFT 9.1版本的ip核 , 仿真出來的結果和我MATLAB算出來的結果差的很多,也沒有倍數關系,scaled因數改了好幾次,沒有溢出,波形大致相同,但是數值上差的太多,已經弄了快兩周了,求做過這個的講講經驗。

2018-07-10 16:16:31

有沒有大神可以提供xilinx FPGA的FFT IP核的調用的verilog 的參考程序,最近在學習FFT的IP核的使用,但是仿真結果有問題,所以想找些參考設計,謝謝

2016-12-25 17:05:38

大家伙,又到了每日學習的時間了,今天咱們來聊一聊vivado 調用IP核。首先咱們來了解一下vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如

2018-05-16 11:42:55

BRAM IP核包括哪幾種類型?Vivado中xilinx_BRAM IP核怎么使用?

2021-03-08 07:11:54

的情況時,總會遇到一些以前未曾接觸過的新內容,這些新內容會讓我們感到陌生和恐懼,不知道該如何下手。

那么今天以xilinx vivado 為例分享學習FPGA 新IP核的正確打開方式。

一、常規

2023-11-17 11:09:22

除了在Xilinx官網上在哪里能下載到Xilinx IP Core 及license? 如FFTFIRCORDIC核等!

2013-06-20 23:51:39

為什么vivado2016調用MIG ip核會收到嚴重警告呢?這個critical warning會有影響嗎,要怎么解決呢?

2021-10-18 09:41:21

本例程主要使用Vivado 調用ROM IP核,用含有正弦曲線的.coe文件初始化ROM,最終通過仿真實現波形的顯示 一、首先建立工程 二、選擇芯片的型號 我

2021-01-08 17:16:43

請問我修改完MIG IP核以后,該如何進行更新呢?搗鼓了半天,要么更新為源代碼,要么就是提示我自己添加的端口不存在

2018-11-12 19:46:15

請問有哪位大神,可以幫忙破解一個vivado的IP核。不勝感激,聯系QQ397679468

2017-11-24 09:30:30

來看比較完善的有Xilinx和Gowin這兩家體驗挺好。其中Vivado中開發目前比較廣泛及方便。今天介紹幾個基于ARM M0/M3的開源項目。基于 ARM Cortex-M3 處理器與 FPGA

2022-08-25 16:31:14

%91/vivado2016-%E8%B0%83%E7%94%A8MIG-ip%E6%A0%B8%E4%B8%A5%E9%87%8D%E8%AD%A6%E5%91%8A-Project-1-19/m-p/884989鏈接不管用的話就按照下圖自己找吧。回復: vivado2016 調用MIG ip核

2021-07-28 07:16:27

`基于 FPAGxilinx vivado 仿真模式介紹本文介紹一下xilinx的開發軟件 vivado 的仿真模式, vivado的仿真暫分為五種仿真模式。分別為:1. run

2018-01-24 11:06:12

16bit,定點signed(1.15),即最高位符號位,15位小數。同時,繪制出matlab中cos時域和頻域的波形如下。 3 Vivado中添加配置FFT IP核Vivado中,打開IP

2019-08-10 14:30:03

HI, 我正在嘗試使用浮點IP在Zedboard上生成一個系統(SoC)(使用VIVADO 2016.4)。由于這個IP具有分層接口,我使用AXI DMA將此ip添加到AXI系統總線。但現在我的問題是如何使用Xilinx SDK檢查此IP? (表示如何向IP發送輸入以及如何檢查輸出)。謝謝

2020-05-26 14:04:10

我正在嘗試將Xilinx MIG IP Core從1.7版升級到1.9版。 Coregen UI左側有一個方便的“升級IP核”按鈕,但它顯示為灰色。我需要做什么才能進行IP核升級?我在Kintex

2019-11-04 09:26:19

Xilinx 官方提供的技術參數來實現對 IP 核的寫控制。寫命令和寫數據總線介紹DDR3 SDRAM控制器IP

2022-02-08 07:08:01

前 言本文主要介紹HLS案例的使用說明,適用開發環境:Windows 7/10 64bit、Xilinx Vivado 2017.4、Xilinx Vivado HLS 2017.4、Xilinx

2021-11-11 09:38:32

是對的,請糾正我,但我認為這一步只需按一個按鈕)3 - 將IP內核導入Vivado并: a-生成塊設計(這是我最不舒服的步驟,我會很高興獲得一些好的建議,因為算法很復雜且IP核不是基本的) b-合成,實現

2020-03-24 08:37:03

嗨,我想創建一個設計,我需要2Mhz clk,我想用16Mhz輸入時鐘的vivado套裝中的“時鐘向導”IP核生成它。根據Xilinx手冊(下面的鏈接),這可以通過CLKOUT4_CASCADE選項

2020-07-27 06:32:48

://pan.baidu.com/s/1XTQtP5LZAedkCwQtllAEyw提取碼:ld9c1概述Vivado標準IP核的移植可謂簡單至極。簡單3步,拷貝IP文件夾到當前工程目錄下;在Vivado的IP Sources中

2019-09-04 10:06:45

cos時域和頻域的波形如下。 3 Vivado中添加配置FFT IP核Vivado中,打開IP Catalog,搜索FFT或者找到分類Core àDigital Signal Processing

2020-01-07 09:33:53

我已獲得Xilinx HDMI IP內核的評估許可證,并已將其加載到許可證管理器中。我的IP經理似乎缺少實際的IP本身。我已經檢查了計算機上的Xilinx文件夾,但找不到任何文件。我找到了名為

2019-01-02 15:02:41

請教大家誰用過 Xilinx PCIe IP 核啊?

2014-01-15 14:38:28

Xilinx FPGA工程例子源碼:PCI Express IP核應用參考設計

2016-06-07 14:13:43 14

14 Xilinx FPGA工程例子源碼:USB IP核

2016-06-07 14:41:57 13

13 介紹如何設計HLS IP,并且在IP Integrator中使用它來作一個設計——這里生成兩個HLS blocks的IP,并且在一個FFT(Xilinx IP)的設計中使用他們,最終使用RTL

2017-02-07 17:59:29 4760

4760

本文基于xilinx 的IP核設計,源于音頻下采樣這一需求。 創建vivado工程 1. 首先打開vivado,創建一個新的project(勾選create project subdirectory

2017-02-08 02:25:09 5883

5883

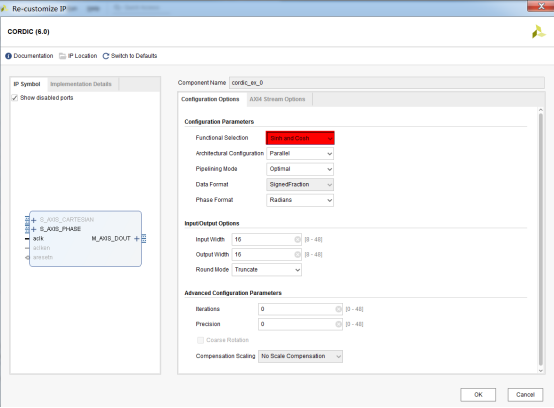

本文介紹如何調用Xilinx的CORDIC IP核生成某一頻率的正弦波和余弦波。 主要是CORDIC IP核的設置,下面對其具體參數的設置進行了說明。 標注1:選擇函數的類型,這里選擇sin和cos

2017-02-08 15:24:09 8277

8277

? 無縫集成在其設計中的工作。該 ?IP? 集成工具支持針對所有 ?Xilinx? 器件提供,其中包括最新 ?UltraScale? 器件系列,可充分滿足 ?Vivado? 設計套件工具 ?2014.4? 以及更高版本的要求。 了解更多 ??

2017-02-09 08:12:36 466

466

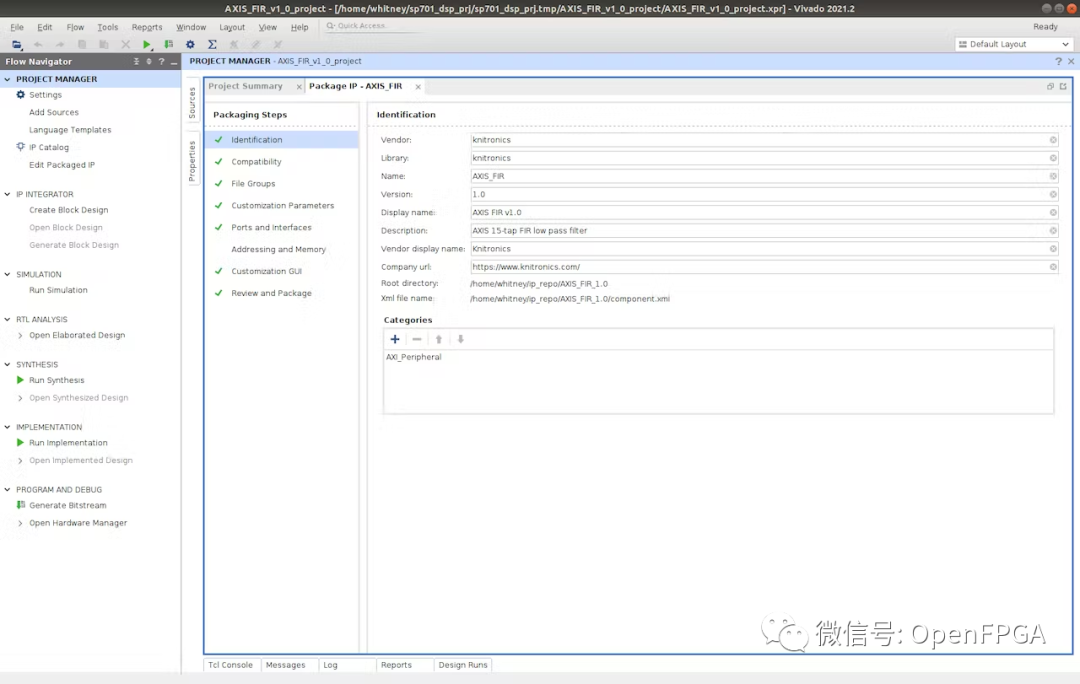

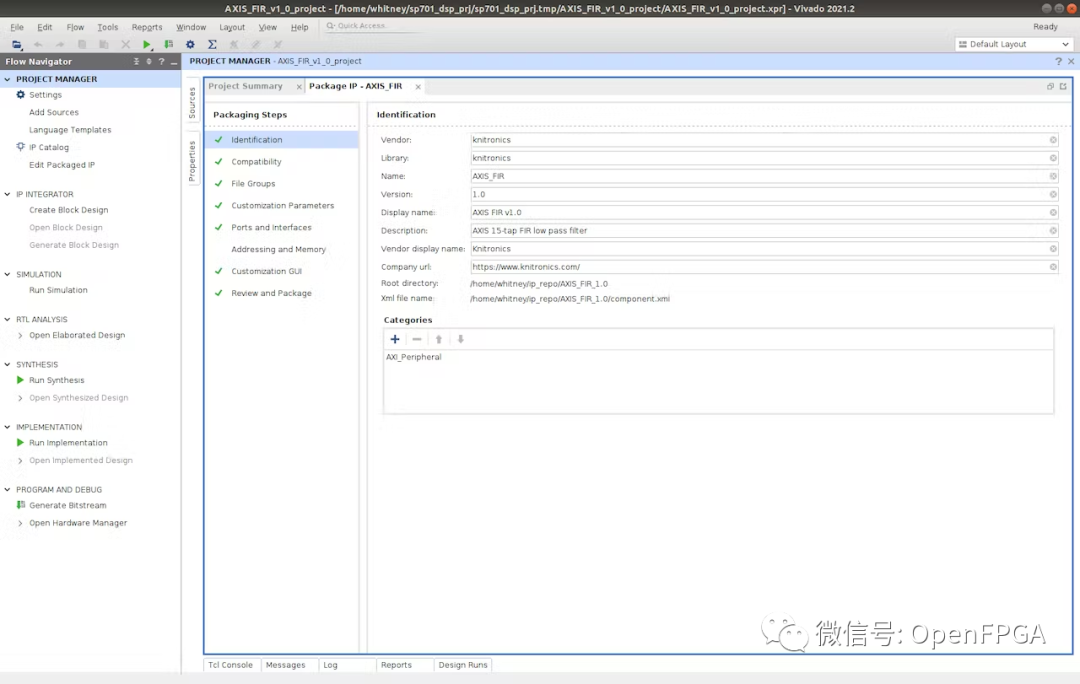

Xilinx的Vivado采用原理圖的設計方式,比較直觀適合大型項目,我們自己的code都需要封裝成user IP。這里主要介紹怎么把多個關聯管腳合并成類似bus的大端口。

2017-09-15 16:54:34 42

42 IP核(IP Core) Vivado中有很多IP核可以直接使用,例如數學運算(乘法器、除法器、浮點運算器等)、信號處理(FFT、DFT、DDS等)。IP核類似編程中的函數庫(例如C語言

2017-11-15 11:19:14 10744

10744 提出一種便于用戶操作并能快速運用到產品的DDR2控制器IP核的FPGA實現,使用戶不需要了解DDR2的原理和操作方式的情況下,依然可以通過IP核控制DDR2。簡單介紹了DDR2的特點和操作原理,并

2017-11-22 07:20:50 5930

5930

IP核(IP Core) Vivado中有很多IP核可以直接使用,例如數學運算(乘法器、除法器、浮點運算器等)、信號處理(FFT、DFT、DDS等)。IP核類似編程中的函數庫(例如C語言

2017-11-28 15:49:58 2339

2339 在給別人用自己的工程時可以封裝IP,Vivado用封裝IP的工具,可以得到像xilinx的ip一樣的可以配置參數的IP核,但是用其他工程調用后發現還是能看到源文件,如何將工程源文件加密,暫時沒有找到方法,如果知道還請賜教。

2018-06-26 11:33:00 8932

8932 大家好,又到了每日學習的時間了,今天咱們來聊一聊vivado 調用IP核。 首先咱們來了解一下vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如

2018-05-28 11:42:14 38569

38569 本文檔的主要內容詳細介紹的是MicroBlaze(Vivado版)設置說明詳細資料免費下載開始IP綜合設計(步驟)

1、在工作流導向面板中的IP Integrator中,點擊Create

2018-09-05 08:00:00 0

0 本文通過一個簡單的例子,介紹Vivado 下的仿真過程。主要參考了miz702的教程,同時也參考了Xilinx的ug937, xapp199.。

2018-11-10 10:53:51 38382

38382 了解如何使用Vivado設計套件的電路板感知功能快速配置和實施針對Xilinx評估板的設計。

2018-11-26 06:03:00 3838

3838 在開發PL時一般都會用到分頻或倍頻,對晶振產生的時鐘進行分頻或倍頻處理,產生系統時鐘和復位信號,下面就介紹一下在vivado2017.3中進行PL開發時調用IP的方法。

2018-12-22 14:26:38 5200

5200 學完SDRAM控制器后,可以感受到SDRAM的控制器的書寫是十分麻煩的,因此在xilinx一些FPGA芯片內已經集成了相應的IP核來控制這些SDRAM,所以熟悉此類IP核的調取和使用是非常必要的。下面我們以A7的DDR3 IP核作為例子進行IP核調取。

2019-11-10 10:28:45 5993

5993

DDR對于做項目來說,是必不可少的。一般用于數據緩存和平滑帶寬。今天介紹下Xilinx DDR控制器MIG IP核的例化及仿真。 FPGA芯片:XC7K325T(KC705) 開發工具:Vivado

2020-11-26 15:02:11 10426

10426

? Xilinx公司的FPGA中有著很多的有用且對整個工程很有益處的IP核,比如數學類的IP核,數字信號處理使用的IP核,以及存儲類的IP核,本篇文章主要介紹BRAM ?IP核

2020-12-29 15:59:39 13270

13270 由于Verilog/Vhdl沒有計算exp指數函數的庫函數,所以在開發過程中可利用cordic IP核做exp函數即e^x值;但前提要保證輸入范圍在(-pi/4—pi/4)。在cordic核中e^x = sinh + cosh所以在配置cordic時點選sinh and cosh即可 如下圖

2022-07-25 16:51:14 5458

5458

Vivado2017.2 中BRAM版本為 Block Memory Generator Specific Features 8.3。BRAM IP核包括有5種類型:Single-port RAM

2021-03-10 06:15:56 19

19 前年,發表了一篇文章《VCS獨立仿真Vivado IP核的一些方法總結》(鏈接在參考資料1),里面簡單講述了使用VCS仿真Vivado IP核時遇到的一些問題及解決方案,發表之后經過一年多操作上也有

2021-03-22 10:31:16 5360

5360 這篇文章原名為《最新 Xilinx vivado IP許可申請》,在很久之前發布于博客園和CSDN上發布了,后來被某公眾號博主盜取發布為自己的原創,現在我轉載我自己的文章反而引用他的。當時剛寫博客

2021-03-29 14:09:52 20069

20069

Xilinx_Vivado_zynq7000入門筆記說明。

2021-04-08 11:48:02 71

71 vivado提供了DDS IP核可以輸出正余弦波形,配置方法如下

2021-04-27 15:52:10 12327

12327

vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如數學運算(乘法器、除法器、浮點運算器等)、信號處理(FFT、DFT、DDS等)。IP核類似編程中的函數庫(例如C語言中的printf()函數),可以直接調用,非常方便,大大加快了開發速度。

2021-04-27 15:45:12 25681

25681

,以及對應的波形圖和 Verilog HDL 實現。我們調取的 DDR3 SDRAM 控制器給用戶端預留了接口,我們可以通過這些預留的接口總線實現對該 IP 核的控制,本章節將會講解如何根據 Xilinx 官方提供的技術參數來實現對 IP 核的寫控制。寫命令和寫數據總線介紹DDR3 SDRAM控制器I

2021-12-04 19:21:05 4

4 在FPGA實際的開發中,官方提供的IP并不是適用于所有的情況,需要根據實際修改,或者是在自己設計的IP時,需要再次調用時,我們可以將之前的設計封裝成自定義IP,然后在之后的設計中繼續使用此IP。因此本次詳細介紹使用VIvado來封裝自己的IP,并使用IP創建工程。

2022-04-21 08:58:05 7941

7941 前年,發表了一篇文章《VCS獨立仿真Vivado IP核的一些方法總結》(鏈接在參考資料1),里面簡單講述了使用VCS仿真Vivado IP核時遇到的一些問題及解決方案,發表之后經過一年多操作上也有些許改進,所以寫這篇文章補充下。

2022-08-29 14:41:55 4676

4676 移植之后,.v和.vhd代碼保持不變,但ISE和vivado的ip核是不一樣的,有很多都不一樣,這里我遇到的是其中一個 : DDS

2022-09-05 15:46:26 5010

5010 今天介紹的是vivado的三種常用IP核:時鐘倍頻(Clocking Wizard),實時仿真(ILA),ROM調用(Block Memory)。

2023-02-02 10:14:01 5002

5002 AMD-Xilinx 的 Vivado 開發工具具有很多方便FPGA開發功能,我最喜歡的功能之一是block design的設計流程。Vivado 中的block design是使用RTL IP形式

2023-02-10 14:51:19 1994

1994

最近,需要使用VCS仿真一個高速并串轉換的Demo,其中需要用到Vivado的SelectIO IP核以及IDELAYCTRL,IDELAY2原語。而此前我只使用VCS仿真過Quartus的IP核。

2023-06-06 11:09:56 4032

4032

使用VCS仿真Vivado里面的IP核時,如果Vivado的IP核的仿真文件只有VHDL時,仿真將變得有些困難,VCS不能直接仿真VHDL

2023-06-06 11:15:35 3576

3576

在仿真Vivado IP核時分兩種情況,分為未使用SECURE IP核和使用了SECURE IP核。

2023-06-06 14:45:43 2875

2875

筆者在校的科研任務,需要用FPGA搭建OFDM通信系統,而OFDM的核心即是IFFT和FFT運算,因此本文通過Xilinx FFT IP核的使用總結給大家開個頭,詳細內容可查看官方文檔PG109。

2023-07-10 10:43:18 2064

2064

DDS(Direct Digital Frequency Synthesizer) 直接數字頻率合成器,本文主要介紹如何調用Xilinx的DDS IP核生成某一頻率的Sin和Cos信號。

2023-07-24 11:23:29 8502

8502

Vivado IP核提供了強大的FIFO生成器,可以通過圖形化配置快速生成FIFO IP核。

2023-08-07 15:36:28 7270

7270

FPGA開發中使用頻率非常高的兩個IP就是FIFO和BRAM,上一篇文章中已經詳細介紹了Vivado FIFO IP,今天我們來聊一聊BRAM IP。

2023-08-29 16:41:49 10361

10361

在給Vivado中的一些IP核進行配置的時候,發現有Shared Logic這一項,這里以Tri Mode Ethernet MAC IP核為例,如圖1所示。

2023-09-06 17:05:12 3014

3014

Vivado是Xilinx公司2012年推出的新一代集成開發環境,它強調系統級的設計思想及以IP為核心的設計理念,突出IP核在數字系統設計中的作用。

2023-09-17 15:37:31 3220

3220

Xilinx公司的FPGA中有著很多的有用且對整個工程很有益處的IP核,比如數學類的IP核,數字信號處理使用的IP核,以及存儲類的IP核,本篇文章主要介紹BRAM IP核的使用。 BRAM是FPGA

2023-12-05 15:05:02 3291

3291 在使用FPGA的時候,有些IP核是需要申請后才能使用的,本文介紹如何申請xilinx IP核的license。

2024-10-25 16:48:32 2275

2275

本文介紹了Vidado中FFT IP核的使用,具體內容為:調用IP核>>配置界面介紹>>IP核端口介紹>>MATLAB生成測試數據>>測試verilogHDL>>TestBench仿真>>結果驗證>>FFT運算。

2024-11-06 09:51:43 5640

5640

電子發燒友App

電子發燒友App

評論