今天我們要介紹的時序分析概念是 min pulse width ,全稱為最小脈沖寬度檢查。這也是一種非常重要的timing arc check,經常用在時序器件或者memory上面。

一般情況下,由于cell本身有變異,rise和fall delay不相同,這樣可能會造成時鐘信號脈沖寬度減小。

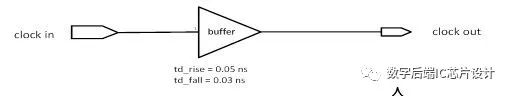

如下圖一個周期為1ns,duty cycle 為50%的clock信號

在經過一個buffer(rise delay: 0.05, fall delay:0.03)

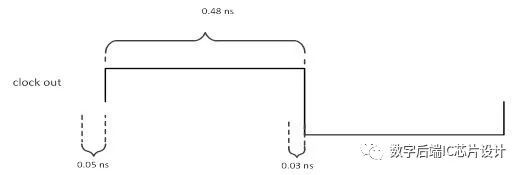

clock信號波形變成如下圖所示:

因此,可以知道,如果某個cell的rise delay大于fall delay,那么輸出時鐘的脈沖寬度要比輸入時鐘小。如果時鐘信號經過一系列相同類型的單元,則時鐘信號的脈沖寬度將會持續減小。如果小于某個最小寬度,可能會導致器件不能正常的捕獲數據。

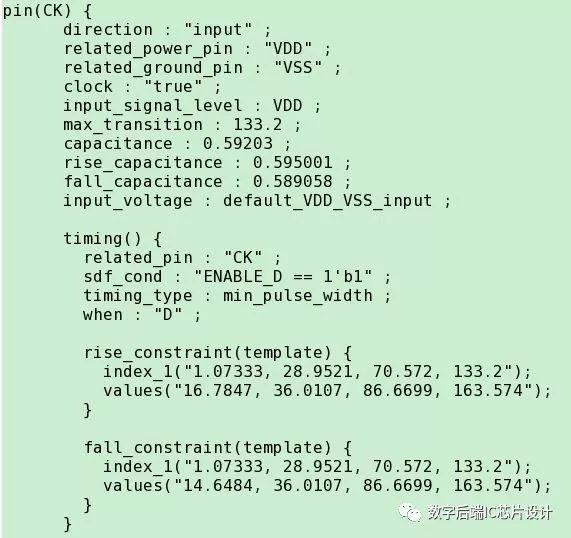

因此,在做timing分析時,我們是必須對cell的pin做min pulse width檢查。通常有兩類方法:

1) sdc里面定義

set_min_pulse_width 2.0 [get_clocks CK1]

2)library里面定義

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

時鐘信號

+關注

關注

4文章

504瀏覽量

29967 -

時序分析器

+關注

關注

0文章

24瀏覽量

5477

發布評論請先 登錄

相關推薦

熱點推薦

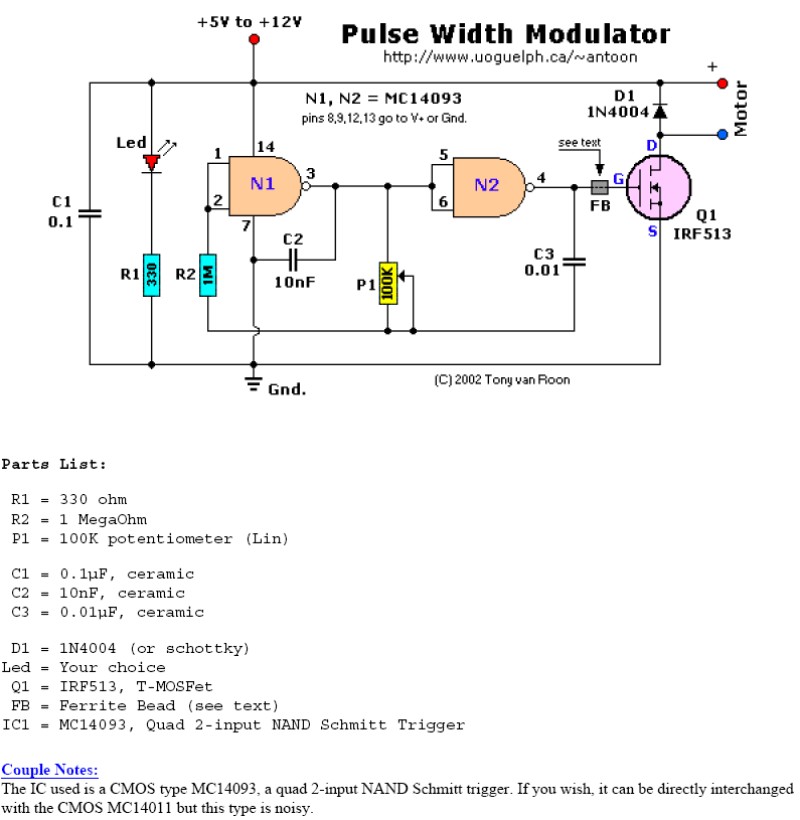

Pulse Width Modulator circuits

Pulse Width Modulator circuits:Couple Notes:The ic used is a CMOS type MC14093a quad 2-input NAND

發表于 03-14 08:31

?2024次閱讀

脈寬調制器工作在不同層次的頻率和功耗-Pulse-Width

Abstract: Build a general-purpose pulse-width modulator using three op amps from a quad-op-amp

發表于 05-03 14:33

?758次閱讀

Pulse Width Modulation

Pulse Width Modulation.多種集合,符合熱愛PCB繪圖的學習者的胃口,喜歡的朋友下載來學習。

發表于 03-21 15:14

?0次下載

時序分析基本概念介紹

今天我們要介紹的時序分析概念是Combinational logic. 中文名組合邏輯單元。這是邏輯單元的基本組成器件。比如我們常見的and, or, not, nand,nor等門電

什么是Min Period檢查?

???????? : true; ????????????????? min_pulse_width_low?? : 0.126; ????????????????? min_pu

clock gate時序分析概念介紹

今天我們要介紹的時序分析概念是clock gate。 clock gate cell是用data signal控制clock信號的cell,它被頻繁地用在多周期的時鐘path,可以節省

時序分析概念min pulse width介紹

時序分析概念min pulse width介紹

評論