Vivado Simulator基本操作

Vivado Simulator是一款硬件描述語言事件驅動的仿真器,支持功能仿真和時序仿真,支持VHDL、Verilog、SystemVerilog和混合語言仿真。點擊運行仿真后,工具欄中顯示了控制仿真過程的常用功能按鈕:

這些控制功能依次是:

- Restart:從0時刻開始重新運行仿真;

- Run All:運行仿真一直到處理完所有event或遇到指令指示停止仿真 ;

- Run For:按照設定的時間運行仿真,每點擊一次都運行指定時長;

- Step:運行仿真直到下一個HDL狀態;

- Break:暫停仿真運行;

- Relaunch Simulation:重新編譯仿真源文件且restart仿真,當修改了源代碼并且保存了文件后,只需要Relaunch即可,而不必關閉仿真再重新打開運行。

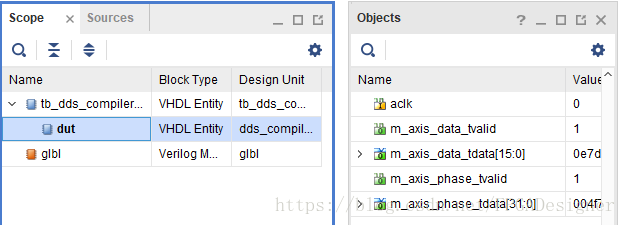

Scope窗口

Vivado Simulator中將HDL設計中的一個層次劃分稱作一個scope,比如實例化一個設計單元便創建了一個scope。在Scope窗口中可以看到設計結構,選中一個scope后,該scope中所有的HDL對象都會顯示在Object窗口中。可以選擇將Object窗口中的對象添加到波形窗口中,這樣便可以觀察到設計中的內部信號。

- Add to Wave Window:將所有狀態為可見的HDL對象添加到波形窗口,值從添加到仿真波形的時刻開始顯示,想要顯示插入之前的值,必須restart(注意不是relaunch,否則會耗費更多的時間);

- Go to Source Code:打開定義選中scope的源代碼;

- Go to Instantiation Source Code:打開實例化選中實例的源代碼(對于Verilog而言是module,對于VHDL而言是entity)

- Log to Wave Database:可以選中記錄當前scope的對象,或者記錄當前scope的對象與所有下級的scope。相關數據會存儲在project_name.sim/sim_1/behav目錄下的wdb文件中。

Objects窗口

該窗口中顯示了當前選中的scope所包含的HDL對象,不同類型或端口的對象顯示為不同的圖標,在Settings中可以設置顯示的類型:

Object的右鍵菜單中有一些新的設置功能:

- Show in Wave Window:在波形窗口中高亮選定的對象;

- Radix:設置Objects窗口中選定對象的值的顯示數字格式,包括默認、2進制(Binary)、16進制(Hexadecimal)、8進制(Octal)、ASCII碼、無符號10進制(Unsigned Decimal)、帶符號10進制(Signed Decimal)和符號量值(Signed Magnitude)。注意此處設置不會影響到波形窗口中的顯示方式;

- Defult Radix:設置Radix中Default所表示的值;

- Show as Enumeration:顯示SystemVerilog枚舉信號的值,不選中時,枚舉對象的值按radix的設置方式顯示;

- Force Constant:將選中對象的值強行定義為一個常量;

- Force Clock:將選中對象強行設定為一個來回振蕩的值(像時鐘一樣);

- Remove Force:移除選定對象的所有Force設置。

Wave窗口

當運行仿真后,會自動打開一個波形窗口,默認顯示仿真頂層模塊中的HDL對象的波形配置。如果關閉了波形窗口,可以點擊Window->Waveform重新打開。

窗口中的HDL對象和分組情況稱作一個波形配置,可以將當前配置保存為wcfg文件,下次運行仿真時就不需要重新添加仿真對象或分組。窗口中還有游標、記號、時間尺等功能幫助設計者測量時間。右鍵菜單中有一些新的設置功能:

- Show in Wave Window:在Object窗口中高亮選定的對象;

- Find/Find Value:前者是搜尋某一對象,后者是搜索對象中的某一值;

- Ungroup:拆分group或虛擬總線(virtual bus);

- Rename/Name:前者設置用戶自定義的對象顯示名稱,后者選中名稱的顯示方式:long(顯示所處層次結構)、short(僅顯示信號名稱)、custom(Rename設置的名稱);

- Waveform Style:設置波形顯示為數字方式或模擬方式;

- Signal Color:設置波形的顯示顏色;

- Divider Color:設置隔離帶的顏色;

- Reverse Bit Order:將選定對象的數值bit顯示順序反轉;

- New Virtual Bus:將選定對象的bit組合為一個新的邏輯向量;

- New Group:將選定對象添加到一個group中,可以像文件夾一樣排列;

- New Divider:在波形窗口中添加一個隔離帶,將信號分開,便于觀察。

Vivado Simulator會將配置(用戶接口控制和Tcl命令)保存到仿真運行目錄的xsimSettings.ini文件中,下此打開仿真時就會自動恢復相關設置。使用此功能時在Simulation Settings中關閉clean up simulation files,以防止重新運行仿真時配置文件被刪除。如果想要恢復默認設置,則開啟clean up simulation files,或直接刪除xsimSettings.ini文件即可。

本文只對Wave窗口做了簡單介紹,本系列第20篇對其中的具體術語和功能使用做了詳細描述。

運行功能和時序仿真

工程創建好后,便可運行行為級仿真(behavioral simulation),在成功地綜合和實現之后,可以運行功能仿真(functional simulation)和時序仿真(timing simulation)。在Flow Navigator中點擊Run Simulation,彈出菜單中選擇需要運行的仿真:

- 綜合后功能仿真:綜合后,通用的邏輯轉換為器件相關的原語,綜合后功能仿真可以確保綜合優化不會影響到設計的功能性。運行時,會生成一個功能網表,并使用UNISIM庫。

- 實現后功能仿真:實現后,設計已經在硬件中完成布局和布線工作,實現后功能仿真可以確保物理優化不會影響到設計的功能性。運行時,會生成一個功能網表,并使用UNISIM庫。

- 綜合后時序仿真:該仿真使用器件模型中估算的時間延遲,并且不包括內部連線延遲。通用的邏輯轉換為器件相關的原語后,可以使用估算的布線和組件間延遲。使用此仿真可以在實現之前查看潛在的時序嚴苛路徑。

- 實現后時序仿真:該仿真使用真實的時間延遲。使用該仿真來檢查設計功能是否能工作在設定的速度上,可以檢測出設計中未約束的路徑、異步路徑時序錯誤(比如異步復位)。

添加仿真啟動腳本文件

設計者可以創建一個批處理文件,添加到工程中,其中的命令將在仿真開始后運行,常用的流程步驟如下所示:

1. 創建一個包含仿真命令的Tcl腳本,比如如果想仿真運行到5μs,添加“run 5us”命令;如果想監測設計內部信號,將其添加到波形窗口中,添加“add_wave/top/I1/signalName”命令;

2. 將腳本文件命名為post.tcl并保存;

3. 將post.tcl文件以仿真源文件的形式添加到工程中,會顯示在Sources窗口的Simulation文件夾下;

4. 在仿真工具欄中點擊“Relaunch”重新編譯運行仿真,Vivado會自動讀取并執行文件中的命令。

編輯:hfy

-

控制仿真

+關注

關注

0文章

7瀏覽量

8359 -

Vivado

+關注

關注

19文章

857瀏覽量

71104 -

時序仿真

+關注

關注

0文章

14瀏覽量

7592

發布評論請先 登錄

Vivado時序約束中invert參數的作用和應用場景

利用 NucleiStudio IDE 和 vivado 進行軟硬件聯合仿真

Vivado仿真之后沒有出現仿真結果的解決方法

vivado時序分析相關經驗

在VIVADO中對NICE進行波形仿真的小問題的解決

vcs和vivado聯合仿真

在vivado上基于二進制碼對指令運行狀態進行判斷

Nucleistudio+Vivado協同仿真教程

AMD Vivado設計套件2025.1版本的功能特性

翼輝信息飛行仿真平臺DEEP UAV Simulator介紹

一文詳解Vivado時序約束

使用Vivado Simulator運行功能和時序仿真案例

使用Vivado Simulator運行功能和時序仿真案例

評論