UltraFast設計方法對您在Vivado Design Suite中的成功至關重要。 介紹UltraFast for Vivado并了解可用的材料,以幫助您在整個設計周期中應用UltraFast方法。在本次視頻中還將了解:HDL 代碼建議目標硬件、約束生成和驗證最佳方法、使用物理約束的規劃和分析工具,如時鐘和引腳規劃,以及最佳性能的布局規劃。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

賽靈思

+關注

關注

33文章

1798瀏覽量

133588 -

設計

+關注

關注

4文章

827瀏覽量

71412 -

design

+關注

關注

0文章

165瀏覽量

47702

發布評論請先 登錄

相關推薦

熱點推薦

AMD Versal CPM5 QDMA Gen4x8 ST Only Performance Design CED示例

本篇博文演示了在AMD Vivado Design Suite 2024.1 中生成 CPM5_QDMA_Gen4x8_ST_Only_Performance_Design 并使用為

【請教】FPGA燒錄軟件工具二次開發問題

請教各位大佬:

Vivado 2018.3和Pango Design Suite 2025.1 這兩款FPGA燒錄軟件工具能夠二次開發嗎?實現上位機控制軟件調用它們,實現自動化的FPGA測試程序燒錄和燒錄成功的反饋信號。

發表于 03-17 16:34

奇捷科技EasyAI ECO Suite即將發布

奇捷科技將于1月29日正式發布集成AI引擎的智能ECO解決方案包——EasyAI ECO Suite。在芯片設計關鍵的后期階段,ECO可能成為決定產品上市速度與成敗的“終極挑戰”。面對復雜ECO設計挑戰,傳統方法依賴人工試錯或衍生工具,效率低下,結果難以預測,成為困擾芯片

AMD Vivado Design Suite 2025.2版本現已發布

AMD Vivado Design Suite 2025.2 版本現已發布,新增對 AMD Versal 自適應 SoC 的設計支持,包含新器件支持、QoR 功能及易用性增強。

Vivado仿真之后沒有出現仿真結果的解決方法

;Run Behavioral Simulation之后,會出現如下圖界面,此時,在Tcl Console中并沒有出現仿真結果。

沒有出現仿真結果的原因是沒有給Vivado時間進行仿真,解決方法

發表于 10-31 06:24

vivado時序分析相關經驗

vivado綜合后時序為例主要是有兩種原因導致:

1,太多的邏輯級

2,太高的扇出

分析時序違例的具體位置以及原因可以使用一些tcl命令方便快速得到路徑信息

發表于 10-30 06:58

Windows系統下用vivado將電路燒寫到MCU200T板載FLASH的方法

在Windows操作系統下使用vivado將設計的電路燒寫到MCU200T開發板上的FLASH中的方法。通過將硬件電路的比特流文件燒寫到板載FLASH內,開發板上電時將自動地從FLASH中讀取比特流

發表于 10-29 08:21

AMD Vivado設計套件2025.1版本的功能特性

隨著 AMD Spartan UltraScale+ 系列現已投入量產,解鎖其功能集的最快途徑便是采用最新 AMD Vivado 工具版本( 2025.1 或更高版本)和全新操作指南資源。該集

在AMD Versal自適應SoC上使用QEMU+協同仿真示例

Cortex A72 (QEMU) 上運行的固件進行仿真,該固件會訪問當前 AMD Vivado Design Suite 仿真中正在進行仿真的 PL 中的 IP。本文將使用 Versal VCK190 和

Vivado無法選中開發板的常見原因及解決方法

在使用 AMD Vivado Design Suite 對開發板(Evaluation Board)進行 FPGA 開發時,我們通常希望在創建工程時直接選擇開發板,這樣 Vivado

AMD Vivado Design Suite 2025.1現已推出

AMD Vivado Design Suite 2025.1 現已推出,支持 AMD Spartan UltraScale+ 和新一代 Versal 器件。這一最新版本還新增了多項功能,可顯著提升 Versal SSIT 器件的

如何使用AMD Vitis HLS創建HLS IP

本文逐步演示了如何使用 AMD Vitis HLS 來創建一個 HLS IP,通過 AXI4 接口從存儲器讀取數據、執行簡單的數學運算,然后將數據寫回存儲器。接著會在 AMD Vivado Design Suite 設計中使用此

如何使用One Spin檢查AMD Vivado Design Suite Synth的結果

本文講述了如何使用 One Spin 檢查 AMD Vivado Design Suite Synth 的結果(以 Vivado 2024.2 為例)。

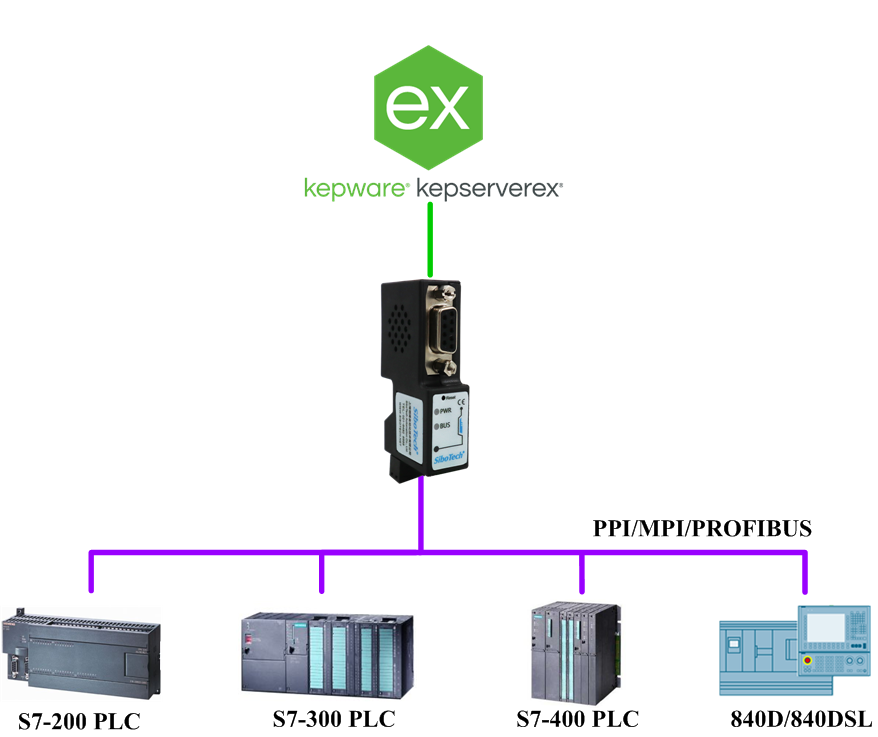

Kepware Siemens Suite

Siemens Suite for KEPServerEX 是 Siemens 設備驅動的集合,為了方便而將它們捆綁在一起。它提供一種簡單且可靠的方法將基于 Siemens Ethernet

Vivado Design Suite設計套件的UltraFast設計方法的介紹

Vivado Design Suite設計套件的UltraFast設計方法的介紹

評論