摘 要: 由于同步動態隨機存儲器SDRAM 內部結構原因導致其控制邏輯比較復雜。現場可編程邏輯門陣列FPGA作為一種半定制電路具有速度快、內部資源豐富、可重構等優點。本文設計了一種基于FPGA 的SDRAM 控制器, 在介紹控制器的邏輯結構的基礎上, 對FPGA 與SDRAM 間數據通信進行了時序分析, 實現SDRAM 帶有自動預充電突發讀寫和非自動預充電整頁讀寫。

0 引 言

SDRAM( Synchronous Dy namic Random Access Memory) 具有價格低廉、容量大、速度快等優點, 但是SDRAM 的控制邏輯相對復雜, 對時序要求也比較嚴格, 這就需要有一個專門的控制器。而FPGA( Field Programmable Gate Array) 具有高速率、多接口、可重構等特點, 基于FPGA 的SDRAM 控制器設計能夠大大縮短開發周期, 簡化設計方法。以往有很多關于SDRAM 控制器設計的文章, 但很少從FPGA 時序分析的角度考慮讀寫數據的準確性, 本文應用FPGA 構建SDRAM 控制器, 并對FPGA 與SDRAM 構建模型進行時序分析, 完成功能仿真和時序仿真, 最終通過板級調試實現SDRAM 的正常讀寫。

1 控制器系統設計

1. 1 SDRAM 簡介

SDRAM 的功能管腳可分為控制信號、地址信號和數據信號三類。

控制信號主要有片選信號、時鐘信號、時鐘使能信號、行列地址選擇信號、讀寫信號及數據有效信號。

地址信號分為塊地址、行地址和列地址, 其中行列地址是分時復用的。在行激活命令時鎖存行地址, 在讀寫命令時鎖存列地址。

數據信號為雙向信號以減少管腳連接, 受數據有效信號控制。

SDRAM 在正常工作前需要有初始化過程:

( 1) 上電后等待200us 使電源及時鐘信號穩定。

( 2) 對SDRAM 所有的BANK 進行一次預充電, 使器件中的存儲陣列處于準備狀態。

( 3) 完成至少8 次自動刷新操作, 使SDRAM 內部的刷新及計數器處于正常運行狀態。

( 4) 配置工作模式寄存器。

SDRAM 要周期性進行自動刷新操作以保證內部數據不會丟失, 目前公認的行刷新周期為64ms,既可集中刷新也可以分散刷新, SDRAM 內部有刷新地址計數器, 每完成一次自動刷新計數器會自動加1。

SDRAM 的讀寫通過寄存器配置可以實現突發長度及突發類型的設置。

突發讀寫長度為1, 2, 4, 8 或整頁模式。通過在讀寫命令有效時設置地址位的第10 位可以實現帶預充電的突發讀寫, 預充電命令可以用來結束當前活動行的操作。對于正常突發讀寫在同一行操作時只需在第一次進行行激活, 以后的若干次操作中寫入列地址即可。若要進行不同行間的切換首先需要預充電關閉當前活動行, 然后在執行行激活命令激活下一操作行。而帶有預充電的突發讀寫在每次操作完成后自動進行一次預充電關閉當前活動行, 因此在每次讀寫時首先都要進行行激活然后再發出讀寫命令。

整頁讀寫模式可以實現整頁內任意長度的讀寫, 最大長度為一般為256, 在每次讀寫完成后需要發出突發終止命令來結束讀寫, 若要進行下一行操作要發出預充電命令關閉當前行。

1. 2 SDRAM 控制器結構

系統采用模塊化設計, 可劃分為4 個模塊, 如圖1 所示, 包括系統控制接口模塊、命令解析與刷新控制模塊、操作信號生成模塊和數據通路模塊。系統控制接口模塊主要由狀態機完成初始化工作及生成CMD 命令; 命令解析與刷新控制模塊主要將CMD的命令解析發出命令請求同時根據刷新計數器發出刷新請求; 操作信號產生模塊由仲裁器仲裁請求生成各種命令信號送給SDRAM 器件; 數據通路模塊控制數據流的傳輸方向并產生有效地數據輸入輸出。

1. 3 各模塊設計

1. 3. 1 系統控制接口模塊

該模塊通過狀態機實現SDRAM 初始化和控制指令產生功能, 圖2 為狀態機圖。SDRAM 初始化過程主要包括: 在系統上電后通過計數器產生200us 等待時間, 其次執行一次預充電命令, 然后完成8 次自刷新操作, 最后配置寄存器。

在控制接口模塊根據接收外部命令和后端模塊響應信號生成CMD 命令送入后端模塊進行相應操作, 表1 為CMD 信號真值表。

1. 3. 2 命令解析與刷新控制模塊

此模塊主要將CMD 命令進行解碼送入下一模塊中, 同一時刻只允許一種命令請求輸出。在寄存器配置過程中將控制器參數配置值和刷新計數器值加載到內部寄存器中。此時刷新控制模塊開始計數, 當達到寄存器內預設值時發出刷新請求, 當刷新響應后計數器繼續工作, 周而復始。

1. 3. 3 操作信號生成模塊

此模塊首先接收命令請求和刷新請求, 通過仲裁器根據刷新請求優先級高于命令請求的原則響應請求同時生成SDRAM 對應操作信號送到SDRAM中。同時此模塊生成數據使能信號OE 送到數據通路模塊控制數據流向。

由于SDRAM 地址信號是分時復用的, 控制器的地址信號ADDR 從高到低依次為SDRAM 的塊地址、行地址、列地址。在此模塊中將ADDR 中包含的塊、行、列地址寫入響應的寄存器中, 在行激活命令時將塊地址、行地址送入SDRAM, 在讀寫命令發出時將列地址送入SDRAM。

1. 3. 4 數據通路模塊

此模塊主要在讀寫操作期間處理數據路徑的操作, OE 信號作為三態門使能端, 寫操作時其為高有效數據DATAIN 經過SDRAM 雙向數據線DQ 寫入SDRAM; 讀操作時當OE 為低數據從DQ 讀到FPGA 內部DATAOU T 數據總線上。DQM 為數據掩碼, 當DQ 為16 位時, DQM 寬度為2, 通過設置DQM 不同位的值可以實現DQ 位高低8 位的讀寫;同時通過在不同的讀寫時刻設置DQM 的值可以實現SDRAM 任意地址的讀寫操作。

2 仿真驗證

2. 1 功能仿真

在控制器設計代碼完成后首先要進行功能邏輯仿真來檢查設計語法是否正確及設計功能是否完全實現。測試向量的編寫一定要具有完備性, 對SDRAM 的設計工作模式都要考慮進內。

圖3 為控制器的功能仿真。此時突發長度為8, tRCD 延遲為3 個時鐘, tCAS 延遲為3 個時鐘。寫命令發出后, 在寫數據使能信號有效時數據被寫進SDRAM; 讀命令發出后, 在讀數據使能信號有效時數據從SDRAM 中讀出。

2. 2 時序仿真

時序仿真是在設計完成綜合布局布線后將器件延時及布線延時反標到仿真文件中進行的一種仿真過程, 時序仿真更切近器件的實際行為。在時序仿真階段首先進行時序分析, 若信號不滿足的時序要求則添加相應時序約束, 再次仿真驗證以保證所有信號能夠正確寫入讀出。

2. 2. 1 時序分析

由于SDRAM 的管腳信號都是在時鐘信號的上升沿有效, 通過SDRAM 數據手冊得知各個信號建立保持時間。同樣從SDRAM 進入FPGA 的數據信號也必須滿足FPGA 的建立保持時間。

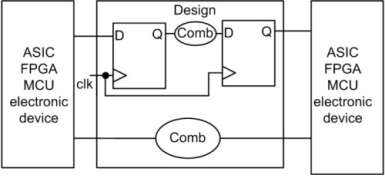

圖4 為FPGA 與SDRAM 數據傳輸模型, 其中:

T din 為數據從FPGA 的IO 口到內部寄存器的傳輸時間;

T 0co 為數據在FPGA 內部寄存器傳輸時間;

T out 為數據從FPGA 寄存器輸出端到IO 口的傳輸時間;

T pcb 為數據在PCB 板走線時間;

T 1co 為數據在SDRAM 內部寄存器傳輸時間。

假定所有信號在PCB 走線延時都是相等的。外部時鐘源經過全局時鐘網絡進入FPGA, 同時從FPGA 輸出時鐘信號到SDRAM。通過時鐘管理單元DCM 的設置可以實現clk 與s_clk 的零相偏移。

SDRAM 作為FPGA 下游器件時, 進入SDRAM的數據信號在時鐘上升沿需滿足建立保持時間。如圖5 所示, 當SSetup 和SHold 分別滿足SDRAM 中數據建立和保持時間時, 數據將正確寫入SDRAM中, 若不滿足要求時由于T0co 根據特定的器件其值一般是固定的, 可以適當約束Tout 時間來達到時序要求。

SDRAM 作為FPGA 上游器件時, 進入FPGA的數據信號在時鐘上升沿也必須滿足建立保持時間。若不滿足可以通過時序約束數據從FPGA 的IO 到內部寄存器的傳輸時間Tdin 來達到時間要求。

2. 2. 2 時序仿真與驗證

圖6 為SDRAM 控制器寫操作的時序仿真, 從波形中可以看出時鐘周期Tclk= 10000ps, SSetup=1763ps, SHold= 6799ps。查閱SDRAM 數據手冊得知滿足建立保持時間。

3 板級驗證

在完成仿真后生成下載文件加載到FPGA 中,添加測試邏輯使SDRAM 中無法觀測的數據通過如LED 顯示確保讀寫正確。同時可以借助在線邏輯分析儀ChipScope 快速檢測和定位問題所在。

4 結論與分析

本設計開發環境為ISE12. 2, 仿真環境為Modelsim6.5。FPGA 器件為XILINX- SPARTAN3 -XC3S400, 速度等級為- 4。SDRAM 型號為HYNIX-HY57V641620FTP- 6。表2 列出了控制器的資源利用率; 在讀寫帶寬方面系統主頻最高能達到100MHz, 表3 為在100MHz 主頻下各種模式的讀寫有效帶寬。

由于采用帶預充電的讀寫操作在每一次操作完成后SDRAM 會自動預充電, 相當于關閉當前活動行, 在執行下一次操作時即使是同一行操作也得先執行行激活命令, 再執行讀寫命令, 這在一定程度上影響了SDRAM 的有效帶寬。而整頁讀寫每次操作完一次進行一次預充電, 隨著突發長度的增加, 減少了一些命令操作和等待時間, 使帶寬大大增加。

本文按照FPGA 的開發流程設計了SDRAM 控制器, 對FPGA 與SDRAM 數據接口進行了時序分析, 并進行了時序仿真。通過板級驗證保證了設計的正確性。此控制器按照參數的設定能夠在不同的模式下工作, 具有一定通用性。

電子發燒友App

電子發燒友App

評論