1 簡(jiǎn)介

上電時(shí)序(Power-up Sequeence)是指各電源軌上電的先后關(guān)系。 與之對(duì)應(yīng)的是下電時(shí)序,但是在電路設(shè)計(jì)過程中,一般不會(huì)去考慮下電時(shí)序(特殊的場(chǎng)景除外)。今天,我們主要了解一下上電時(shí)序控制相關(guān)內(nèi)容。

2 時(shí)序電路設(shè)計(jì)

今天主要從通用設(shè)計(jì)方案和專用設(shè)計(jì)方案兩個(gè)方面進(jìn)行進(jìn)行講解:

- 通用設(shè)計(jì)方案

通用的設(shè)計(jì)方案可以通過分立器件實(shí)現(xiàn)和 通用延時(shí)芯片實(shí)現(xiàn) 。

- 分立器件實(shí)現(xiàn)延時(shí)

這種方式比較簡(jiǎn)單,就是利用電容的充電特性。延時(shí)的時(shí)長(zhǎng),通過改變電容值的大小來實(shí)現(xiàn)。具體電路見下:

這種上電方案主要特點(diǎn)是電路結(jié)構(gòu)簡(jiǎn)單,但上電延時(shí)時(shí)間難以精確控制,且可能導(dǎo)致上電的過程比較緩慢,在FPGA的上電過程中可以使用。

- 通用延時(shí)芯片

我們采用的LM3880芯片進(jìn)行電源時(shí)序控制,這種控制的方式比較簡(jiǎn)單。LM3880 簡(jiǎn)單電源時(shí)序控制器提供了最簡(jiǎn)單的方法來控制多個(gè)獨(dú)立電壓軌的上電時(shí)序和下電時(shí)序。通過錯(cuò)開啟動(dòng)序列,可以避免可能影響系統(tǒng)可靠性的鎖存情況或大 浪涌電流。

該芯片可以同時(shí)實(shí)現(xiàn)對(duì)上下電的控制,上電與下單的延時(shí)時(shí)間由EN管腳進(jìn)行控制,默認(rèn)是2ms。

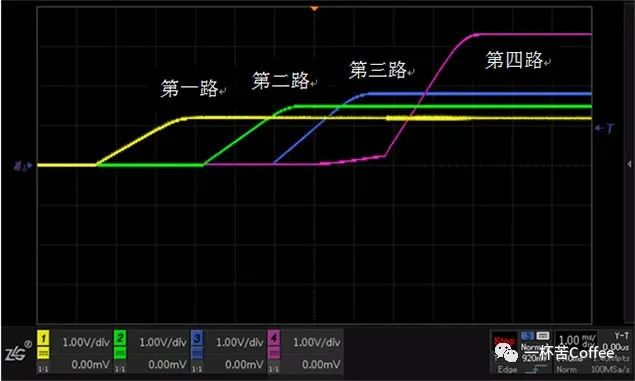

上電時(shí)序圖見下:

下電時(shí)序圖見下:

這款芯片還可以對(duì)延時(shí)的時(shí)間進(jìn)行調(diào)整,默認(rèn)為2ms。如需對(duì) VCC 電壓軌提供額外的延遲序列,在 EN 引腳上連接一個(gè)電容,見下圖:

在使用內(nèi)部上拉電流源為外部電容 (CEN) 充電的情況下,可通過下面公式來計(jì)算使能引腳延遲:

第一個(gè)計(jì)時(shí)器將在上升閾值開始計(jì)數(shù),但始終會(huì)在第一個(gè)輸出標(biāo)志 釋放之前 EN 引腳取消置位時(shí)復(fù)位:

- 專用設(shè)計(jì)方案

許多FPGA要求不同電源電壓軌以特定順序上電。內(nèi)核電壓的供應(yīng)往往需要早于I/O電壓的供應(yīng),否則一些FPGA會(huì)被損壞。為了避免這種情況,電源需要按正確的順序上電。使用標(biāo)準(zhǔn)DC-DC轉(zhuǎn)換器上的使能引腳,可以輕松實(shí)現(xiàn)簡(jiǎn)單的上電時(shí)序控制。器件關(guān)斷通常也需要時(shí)序控制,僅執(zhí)行使能引腳時(shí)序控制,很難取得良好的結(jié)果。更好的解決辦法是使用具有高級(jí)集成時(shí)序控制功能的PMIC,例如 ADP5014。

更多的內(nèi)容請(qǐng)參考設(shè)計(jì)手冊(cè)。

-

FPGA

+關(guān)注

關(guān)注

1660文章

22412瀏覽量

636309 -

電路設(shè)計(jì)

+關(guān)注

關(guān)注

6741文章

2702瀏覽量

219516 -

時(shí)序電路

+關(guān)注

關(guān)注

1文章

114瀏覽量

22297 -

上電時(shí)序

+關(guān)注

關(guān)注

0文章

20瀏覽量

12581 -

電源軌

+關(guān)注

關(guān)注

1文章

105瀏覽量

6247

發(fā)布評(píng)論請(qǐng)先 登錄

數(shù)字電路之時(shí)序電路

基本時(shí)序電路設(shè)計(jì)實(shí)驗(yàn)

Verilog設(shè)計(jì)初學(xué)者例程:時(shí)序電路設(shè)計(jì)

時(shí)序電路設(shè)計(jì)實(shí)例 (Sequential-Circuit D

時(shí)序電路設(shè)計(jì)串入/并出移位寄存器

時(shí)序電路設(shè)計(jì)串入/并出移位寄存器

基于FPGA技術(shù)的RS232接口時(shí)序電路設(shè)計(jì)方案

組合電路和時(shí)序電路的講解

同步時(shí)序電路設(shè)計(jì)

基本邏輯電路、時(shí)序電路、組合電路設(shè)計(jì)

什么是同步時(shí)序電路和異步時(shí)序電路,同步和異步電路的區(qū)別?

時(shí)序邏輯電路設(shè)計(jì)之同步計(jì)數(shù)器

硬件電路設(shè)計(jì)之時(shí)序電路設(shè)計(jì)

硬件電路設(shè)計(jì)之時(shí)序電路設(shè)計(jì)

評(píng)論