1997年,富士通公司研發(fā)出一種名為芯片上引線(Lead On Chip,LOC)的封裝形式,稱作LOC型CSP。為契合CSP的設(shè)計需求,LOC封裝相較于傳統(tǒng)引線框架CSP做出了一系列革新設(shè)計:將

2025-07-17 11:41:26 3725

3725

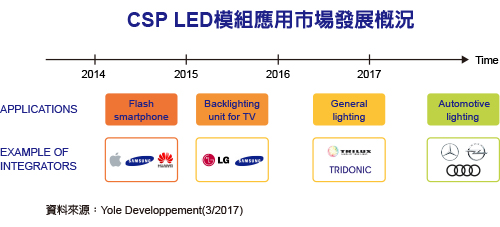

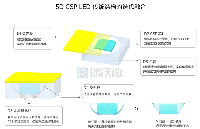

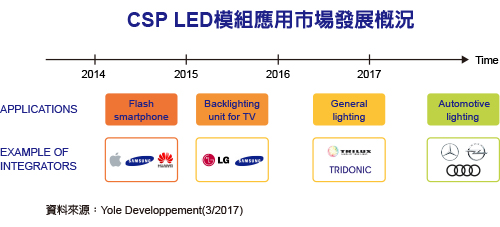

發(fā)光二極體(LED)封裝廠在生態(tài)系統(tǒng)將日趨邊緣化。上游LED晶粒廠為降低制造成本與微型化晶片尺寸,競相展開晶粒尺寸封裝(Chip Scale Package, CSP)技術(shù)布局,且該技術(shù)省略封裝制程,遂讓磊晶廠未來營運(yùn)模式將跳過封裝廠,直接與下游燈具系統(tǒng)商合作,導(dǎo)致封裝廠在供應(yīng)鏈的重要性大幅下降。

2014-05-06 09:03:50 3784

3784 LED封裝技術(shù)出現(xiàn)新面孔。一般半導(dǎo)體廠商已經(jīng)相當(dāng)熟悉的芯片級封裝(Chip Scale Package, CSP),正逐漸滲透到LED領(lǐng)域,如手機(jī)閃光燈與液晶電視背光用的LED皆已開始導(dǎo)入此一技術(shù)。

2017-03-27 09:32:36 3386

3386

1. BGA和CSP封裝技術(shù)詳解 2.?干貨分享丨BGA開路金相切片分析 (BGA Open Cross-Section) ? ? ? 審核編輯:彭靜

2022-07-26 14:43:18 7462

7462 ? 半導(dǎo)體器件有許多封裝形式,按封裝的外形、尺寸、結(jié)構(gòu)分類可分為引腳插入型、表面貼裝型和高級封裝三類。從DIP、SOP、QFP、PGA、BGA到CSP再到SIP,技術(shù)指標(biāo)一代比一代先進(jìn)。總體說來

2023-08-28 09:37:11 3275

3275

請問大家,0.4pitch的CSP封裝是怎么布線的,間距太小了

2016-06-29 21:36:01

在便攜式、低引腳數(shù)和低功率產(chǎn)品中應(yīng)用廣泛,主要用于閃存、RAM、DRAM存儲器等產(chǎn)品中。目前,超過100家公司開發(fā)CSP產(chǎn)品:Amkor、Tessera、Chip-scale、Sharp等,市場潛力巨大。

2020-03-18 09:01:54

csp模式不知道是哪里出現(xiàn)了問題?csp模式為什么不能讓電機(jī)轉(zhuǎn)起來?

2021-09-24 06:24:56

應(yīng)用集成無源(ASIP)陣列或集成無源器件(IPD)。某種程度上,CSP是一種“沒有封裝體”的產(chǎn)品,芯片就是它的封裝體。CSP-ASIP可以在目前許多無線手持設(shè)備中找到,掌上電腦、移動消費(fèi)類電子產(chǎn)品也

2018-11-23 16:58:54

剛安裝了protel,可是從sch轉(zhuǎn)換到pcb時,發(fā)現(xiàn)好多封裝都沒有,我加載了一下,但好像都不是最新的,哪位兄弟有啊?!

2011-11-26 14:26:54

、無阻抗IC白/藍(lán)膜片、長期高價求購封裝測試廠淘汰的廢舊QFN、PLCC、BGA、CSP、WL-CSP等各種封裝后的IC芯片、Blue tape、chip、wafer.藍(lán)膜片、白膜片、IC硅片、IC晶

2020-12-29 08:27:02

CYD3175PD做一個A口,CSP做A的地 還是GND 做地。CSP和GND之間需要串電阻嗎?

2025-06-03 12:10:28

在閱讀 CYPD3175 的文檔時,關(guān)于連接到 CSP 引腳的 5mΩ 或 10mΩ RS 電阻值,是否有更詳細(xì)的文檔可以幫助我了解如何選擇 RS 電阻值? 謝謝。

2025-05-22 07:40:31

= (VIN-VOUT)/(IOUT + IQ) 進(jìn)行計算。一般來說,封裝尺寸越小,功耗越小。但是QFN封裝可以提供極佳的散熱性能,這種性能完全可與尺寸是其1.5~2倍的眾多封裝相媲美。

2011-06-16 16:12:03

初學(xué)者,請老師們幫忙解疑!PBGA,CSP,SOP分別是什么意思.

2013-01-17 16:52:09

不足。板級可靠性主要取決于封裝類型,而CSP器件平均能經(jīng)受-40~125℃的熱周期800~1200次,可以無需下填充。然而,如果采用下填充材料,大多數(shù)CSP的熱可靠性能增加300%。CSP器件故障一般

2013-10-22 11:43:49

工藝后缺陷(如橋接和直立)的出現(xiàn),焊盤尺寸最優(yōu)化和元件間距是關(guān)鍵。只要設(shè)計合理,這些封裝可以緊貼著放置,間距可小至150?m。 另外,0201器件能貼放到BGA和較大的CSP下方。 CSP組件下面

2018-09-10 15:46:13

小,擊穿電壓穩(wěn)定,良率高,鉗位 電壓一般,電容有低容,普容和高容,6寸可以做回掃型ESD產(chǎn)品;第三代TVS主要以8寸晶圓流片為主,以CSP晶圓級封裝為主(DFN),這種產(chǎn)品是高性能的ESD,采用8寸的先進(jìn)

2020-07-30 14:40:36

`什么? 你對CSP的了解還不夠?趕快來圍觀吧! 首先,得知道什么叫CSPCSP(Chip Scale Package),又稱為芯片級封裝器件, 其技術(shù)性主要體現(xiàn)為讓芯片面積與封裝面積之比超過1

2017-02-24 16:36:32

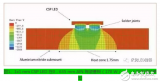

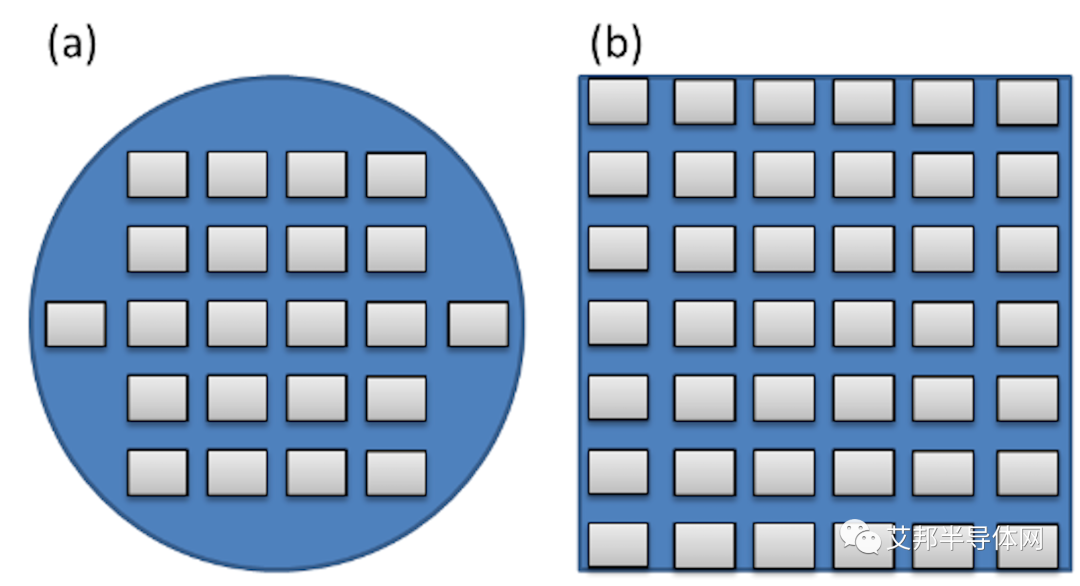

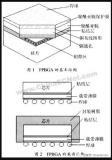

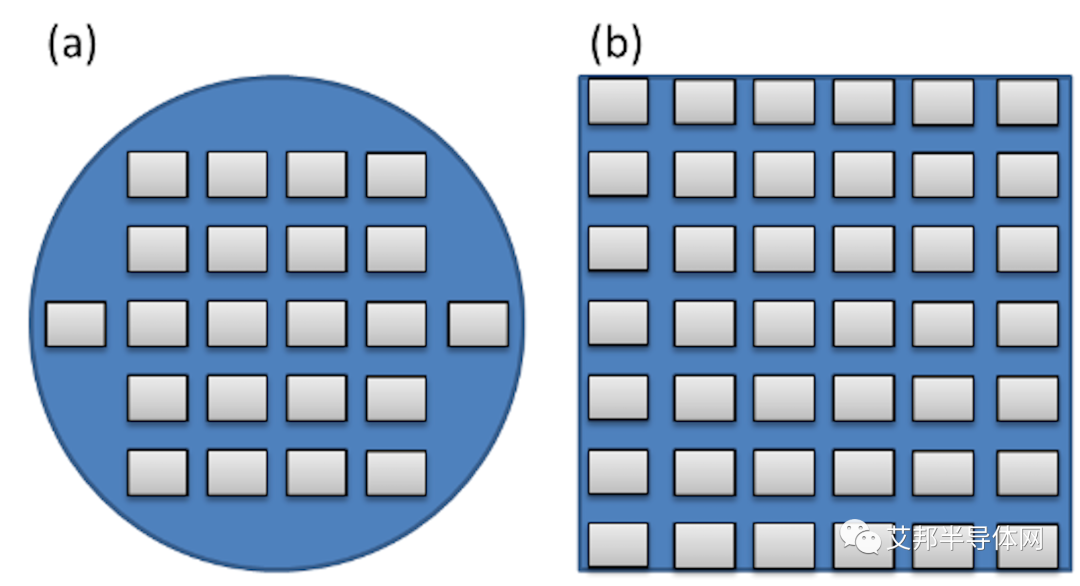

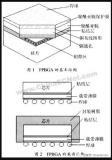

發(fā)展趨勢的推動下,制造商開發(fā)出更小的封裝類型。最小的封裝當(dāng)然是芯片本身,圖1描述了IC從晶片到單個芯片的實現(xiàn)過程,圖2為一個實際的晶片級封裝(CSP)。 晶片級封裝的概念起源于1990年,在1998年

2018-08-27 15:45:31

怎么選擇晶圓級CSP裝配工藝的錫膏?

2021-04-25 08:48:29

的內(nèi)存芯片封裝技術(shù),其技術(shù)性能又有了新的提升。CSP封CSP封裝裝可以讓芯片面積與封裝面積之比超過1:1.14,已經(jīng)相當(dāng)接近1:1的理想情況,絕對尺寸也僅有32平方毫米,約為普通的BGA的1/3,僅僅

2018-09-12 15:15:28

引言 無引線導(dǎo)線封裝(LLP)是一種基于導(dǎo)線架的晶片級封裝(CSP),它可以提高芯片的速度、降低熱阻并減小貼裝芯片所需要的PCB面積。由于這種封裝的尺寸小、高度很低,所以此封裝是高密度PCB

2018-09-10 16:37:26

晶圓級CSP的返修工藝包括哪幾個步驟?晶圓級CSP對返修設(shè)備的要求是什么?

2021-04-25 08:33:16

的問題。 由于設(shè)計的變更,制造過程中的缺陷或產(chǎn)品在使用過程中的失效,有時需要對CSP裝配進(jìn)行返修,而應(yīng)用傳 統(tǒng)的底部填充材料是不可以進(jìn)行返修的,原因是無法將己經(jīng)固化的填充材料從PCB上清除掉。目前市場上己 經(jīng)有

2018-09-06 16:32:17

的內(nèi)存芯片封裝技術(shù),其技術(shù)性能又有了新的提升。CSP封CSP封裝裝可以讓芯片面積與封裝面積之比超過1:1.14,已經(jīng)相當(dāng)接近1:1的理想情況,絕對尺寸也僅有32平方毫米,約為普通的BGA的1/3,僅僅

2023-12-11 01:02:56

芯片封裝測試流程詳解ppt?按封裝外型可分為:SOT 、QFN 、SOIC、TSSOP、QFP、BGA、CSP等;? 決定封裝形式的兩個關(guān)鍵因素:?封裝效率。芯片面積/封裝面積,盡量接近1:1

2012-01-13 11:46:32

請問ADN4670BCPZ焊接溫度曲線有么?以及這種CSP封裝的焊接需要注意的事項有哪些?

2019-01-18 16:44:20

大于晶片的20%,而且它必須屬于單晶片、直接表面安裝式封裝,具備“芯片尺寸”的要求。在這種寬泛的定義下,即使BGA封裝也可以歸屬到這一類別。事實上,我研究過超過50種不同類型的CSP。晶圓級芯片尺寸

2016-06-29 11:32:56

由于疊層CSP封裝的復(fù)雜性,其振動特性很難用精確的理論模型表示。同時,由于傳統(tǒng)的共振準(zhǔn)則沒有考慮到系統(tǒng)的變異性和模糊性,導(dǎo)致分析結(jié)果與真值具有較大偏差。該文利用

2009-02-27 15:37:11 9

9 基于進(jìn)程代數(shù)的CSP 方法是一種重要的形式化協(xié)議分析驗證方法。本文首先簡單介紹了CSP 相關(guān)理論,并以NSPK 協(xié)議為例系統(tǒng)概述了安全協(xié)議的CSP 建模方法。為更好的查明協(xié)議的安全缺

2009-08-06 11:22:16 12

12 Marki Microwave 的 ATN10-0050CSP1 是一種衰減器 MMIC,工作頻率范圍為 DC 至 50 GHz。它可以處理 1 W

2023-05-12 12:00:37

6 dB,功率 2 W,阻抗 50 歐姆。標(biāo)簽:表面貼裝,正增益斜率。MEQ6-26CSP1 的更多細(xì)節(jié)可以在下面看到。產(chǎn)品規(guī)格產(chǎn)品詳情零件號MEQ6-26CSP

2023-05-12 12:51:23

基于FPGA 的嵌入式ASIP 軟核設(shè)計與實現(xiàn)作者:李慶誠 任健 劉嘉欣 黃寶貞 來源:微計算機(jī)信息摘要:采用ASIP+FPGA 模式設(shè)計了一款嵌入式微處理器軟核,以該軟核為例從體系結(jié)構(gòu)和

2010-02-06 10:44:40 30

30 采用ASIP+FPGA模式設(shè)計了一款嵌入式微處理器軟核,以該軟核為例從體系結(jié)構(gòu)和指令集設(shè)計兩方面對ASIP+FPGA模式微處理器軟核的設(shè)計進(jìn)行了分析和驗證,最后通過與傳統(tǒng)微處理器對比

2010-07-28 17:41:46 17

17 半導(dǎo)體器件有許多封裝形式,按封裝的外形、尺寸、結(jié)構(gòu)分類可分為引腳插入型、表面貼裝型和高級封裝三類。從DIP、SOP、QFP、PGA、BGA到CSP再到SIP,技術(shù)指標(biāo)一代比一代先進(jìn)。總體

2010-11-14 21:35:09 55

55 加州微器件公司(California Micro Devices)推出的0.4mm間距芯片級封裝(CSP) Centurion電磁干擾(EMI)濾波器為業(yè)界開創(chuàng)新的價格/性能標(biāo)準(zhǔn)。該特定應(yīng)用集成無源(ASIP)

2006-03-13 13:07:37 749

749 摘要:本文詳細(xì)討論了Maxim的晶片級封裝(WL-CSP),其中包括:晶圓架構(gòu)、卷帶包裝、PCB布局、安裝及回流焊等問題。本文還按照IPC和JEDEC標(biāo)準(zhǔn)提供了可靠性測試數(shù)據(jù)。 注

2009-04-21 11:30:27 9869

9869

SMT最新技術(shù)之CSP及無鉛技術(shù)

CSP、0201無源元件、無鉛焊接和光電子,可以說是近來許多公司在PCB上實踐和積極*價的熱門先進(jìn)技術(shù)。

2009-11-16 16:41:10 1828

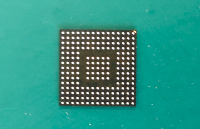

1828 CSP封裝內(nèi)存

CSP(Chip Scale Package),是芯片級封裝的意思。CSP封裝最新一代的內(nèi)存芯片封裝技術(shù),其技術(shù)性能又有了新的提升。CSP封裝可以讓芯片面積與封裝面積之比超

2009-12-25 14:24:49 810

810 高級封裝,高級封裝是什么意思

晶片級封裝CSP(Chip Scale Package)。幾年之前以上所有的封裝其封裝本體面積與芯片面積之比通常都是

2010-03-04 11:13:29 1774

1774 什么是CSP封裝

近幾年的硬件發(fā)展是日新月異,處理器已經(jīng)進(jìn)入G赫茲時代,封裝形式也是經(jīng)歷了數(shù)種變化。不過,光有一顆速急力猛的芯還遠(yuǎn)遠(yuǎn)不夠

2010-03-04 11:43:25 15859

15859 SIP(封裝系統(tǒng)),SIP(封裝系統(tǒng))是什么意思封裝概述 半導(dǎo)體器件有許多封裝型式,從DIP、SOP、QPF、PGA、BGA到CSP再到SIP,技術(shù)指標(biāo)一代比一代先進(jìn),這些都是前

2010-03-26 17:04:25 20775

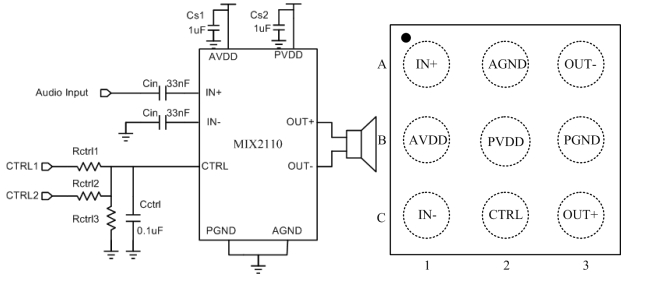

20775 上海矽諾微電子針對目前的便攜式市場推出全系列兼容的CSP-9封裝的D類音頻功放。該系列產(chǎn)品目前有三顆,分別是MIX

2011-01-11 09:15:17 1993

1993

Tensilica Xtensa體系結(jié)構(gòu)可配置、指令集可自定義處理器和Xplorer、XPRES、XEnergy等工具集大大提高了ASIP處理器開發(fā)速度,加快了針對不同應(yīng)用領(lǐng)域探索專用處理器設(shè)計空間的效率

2011-06-18 10:17:23 5087

5087

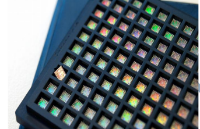

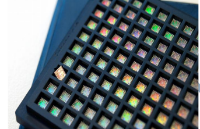

CSP封裝芯片的量產(chǎn)測試采用類似晶圓測試的方法進(jìn)行,但是兩者的區(qū)別在于:晶圓的測試,探針是扎在管芯的PAD(通常情況下為鋁金屬)上,而CSP封裝的測試座,探針是扎到CSP封裝的錫

2012-05-02 10:00:40 2018

2018 OV2715_CSP3_Datasheet

2016-12-25 23:00:49 5

5 芯片級封裝介紹本應(yīng)用筆記提供指引使用與PCB安裝設(shè)備相關(guān)的芯片級封裝。包括系統(tǒng)的PCB布局信息制造業(yè)工程師和制造工藝工藝工程師。 包概述 倒裝芯片CSP的包概述半導(dǎo)體封裝提供的芯片級封裝代表最小

2017-03-31 10:57:32 45

45 超級CSP——讓倒裝芯片獲得最大可靠性一種晶圓片級封裝

2017-09-14 11:31:37 22

22 CSP封裝的芯片測試,由于其封裝較小,采用普通的機(jī)械手測試無法實現(xiàn),目前主要采用類似晶圓測試的方法,在芯片完成置球封裝后,先不做劃片,而直接用探針卡進(jìn)行測試,測試完成后,再實行劃片、分選和包裝。

2017-10-27 15:11:10 8856

8856 模型檢測是通信順序進(jìn)程(communicatmg sequential processes,簡稱CSP)形式化驗證的重要手段.當(dāng)前,CSP模型檢測方法基于操作語義,需將進(jìn)程轉(zhuǎn)化為遷移系統(tǒng),進(jìn)而

2018-01-23 16:03:53 1

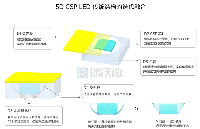

1 CSP(chip scale package)封裝是指一種封裝自身的體積大小不超過芯片自身大小的20%的封裝技術(shù)(下一代技術(shù)為襯底級別封裝,其封裝大小與芯片相同)。為了達(dá)成這一目的,LED制造商

2018-06-07 15:40:00 1640

1640

近幾年大陸背光產(chǎn)品價格持續(xù)下滑,億光等LED廠商在背光市場出貨比重仍不低,為避開陸廠價格競爭,今年億光將以mini LED、CSP封裝產(chǎn)品搶攻高端背光應(yīng)用。

2018-04-27 11:20:00 2917

2917 目前CSP LED的主流結(jié)構(gòu)可分為有基板和無基板,也可分為五面發(fā)光與單面發(fā)光。所說的基板自然可以視為一種支架。很顯然,為了滿足CSP對封裝尺寸的要求,傳統(tǒng)的支架,如2835,的確不能使用,但并不

2018-07-12 14:34:00 11195

11195 針對CSP技術(shù)難題,海迪科經(jīng)過技術(shù)團(tuán)隊的刻苦攻關(guān)之后,成功研發(fā)并推出了一款新型光源WLCSP,從而實現(xiàn)了CSP技術(shù)的大幅升級。

2018-07-17 14:21:20 5339

5339 CSP(chip scale package)封裝是指一種封裝自身的體積大小不超過芯片自身大小的20%的封裝技術(shù)(下一代技術(shù)為襯底級別封裝,其封裝大小與芯片相同)。為了達(dá)成這一目的,制造商盡可能

2018-08-10 15:43:52 16128

16128 CSP(Chip Scale Package)封裝,是芯片級封裝的意思。CSP封裝最新一代的內(nèi)存芯片封裝技術(shù),其技術(shù)性能又有了新的提升。CSP封CSP封裝裝可以讓芯片面積與封裝面積之比超過1

2018-08-17 15:25:38 18958

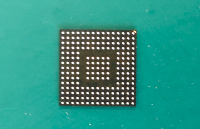

18958 CSP封裝是一種芯片級封裝,我們都知道芯片基本上都是以小型化著稱,因此CSP封裝最新一代的內(nèi)存芯片封裝技術(shù),可以讓芯片面積與封裝面積之比超過1:1.14,已經(jīng)相當(dāng)接近1:1的理想情況,被行業(yè)界評為單芯片的最高形式,與BGA封裝相比,同等空間下CSP封裝可以將存儲容量提高三倍。

2019-03-07 15:41:08 15220

15220 CSP封裝是最新一代的內(nèi)存芯片封裝技術(shù),其技術(shù)性能又有了新的提升。CSP封裝可以讓芯片面積與封裝面積之比超過1:1.14,已經(jīng)相當(dāng)接近1:1的理想情況,絕對尺寸也僅有32平方毫米,約為普通的BGA

2019-06-24 14:12:36 21830

21830 針對AI算法廠商紛紛將算法芯片化的趨勢,近期,全球知名的EDA工具廠商新思科技(Synopsys)推出了一套能夠?qū)崿F(xiàn)專用指令集處理器(ASIP)開發(fā)流程自動化的工具——ASIP Designer,可助力AI算法廠商快速的實現(xiàn)“算法芯片化”。

2019-06-26 08:41:52 5907

5907

在5G應(yīng)用相關(guān)的眾多封裝技術(shù)中,倒裝芯片技術(shù)的應(yīng)用需求越來越廣泛,隨之而來的是對底部填充材料提出了更高的要求,既要確保保護(hù)蓋或強(qiáng)化件與基材的良好粘合,又要減少芯片和封裝體在熱負(fù)荷下會發(fā)生翹曲的影響。

2021-04-08 16:22:43 5947

5947 電子發(fā)燒友網(wǎng)為你提供TE(ti)CAT-CSP-5T相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊,更有CAT-CSP-5T的引腳圖、接線圖、封裝手冊、中文資料、英文資料,CAT-CSP-5T真值表,CAT-CSP-5T管腳等資料,希望可以幫助到廣大的電子工程師們。

2021-07-08 21:00:04

隨著集成電路的廣泛應(yīng)用,集成度越來越高,在BGA技術(shù)開始推廣的同時,另外一種從BGA發(fā)展來的CSP封裝技術(shù)正在逐漸展現(xiàn)它的生力軍本色。作為新一代的芯片封裝技術(shù),CSP封裝可以讓芯片面積與封裝面積之比

2021-12-03 13:58:36 4048

4048 先進(jìn)封裝形式μBGA、CSP的回流焊接技術(shù)介紹說明。

2022-05-06 15:17:46 4

4 倒裝芯片 CSP 封裝

2022-11-14 21:07:58 22

22 CSP封裝(Chip Scale Package)是指芯片級封裝,其封裝尺寸和芯片核心尺寸基本相同,一般芯片面積與封裝面積的比例約在1:1.1。CSP封裝最先規(guī)模應(yīng)用在消費(fèi)電子和個人電腦,與我們的生活息息相關(guān)。

2023-03-28 14:52:09 17727

17727 CSP2510C 數(shù)據(jù)表

2023-04-26 19:29:44 1

1 CSP(Chip Scale Package)封裝芯片是一種高密度、小尺寸的封裝形式,它在集成電路行業(yè)中具有廣泛的應(yīng)用。對于CSP封裝芯片的測試方法而言,主要涉及到以下幾個方面:

2023-06-03 10:58:16 2565

2565 今天我們來介紹PLCSP(Panel Level Chip Scale Packaging)。同理,PLCSP是一種將面板級封裝(PLP)和芯片尺寸封裝(CSP)合為一體的封裝技術(shù)。芯片尺寸封裝(CSP)是指整個package的面積相比于silicon總面積不超過120%的封裝技術(shù)。

2023-06-19 11:31:46 2566

2566

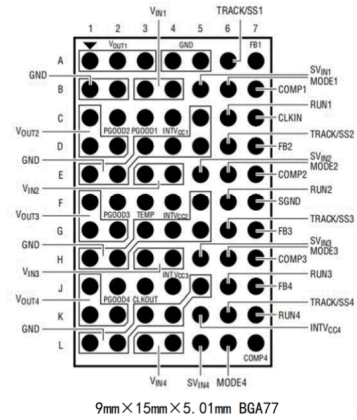

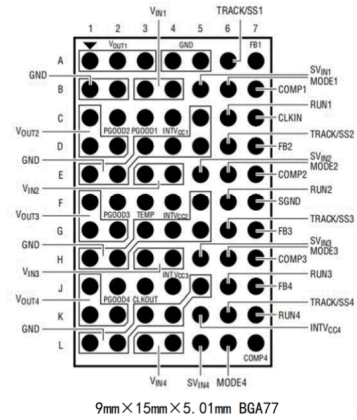

,ASIP0400AB產(chǎn)品相比ADI公司LTM4644IY產(chǎn)品參數(shù)接近,功能引腳兼容,可以完美支持PIN TO PIN替代 對比表如下: ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ASIP0400AB與LTM4644IY#PBF參數(shù)對比

2023-06-19 15:30:58 2034

2034

),是WL-CSP封裝類型的芯片,用膠位置是BGA芯片底部填充漢思BGA芯片底部填充膠應(yīng)用客戶芯片參數(shù):芯片主體厚度(不包含錫球):50微米因為有好幾種芯片,現(xiàn)在可以確定的是

2023-05-18 05:00:00 1791

1791

電子封裝是現(xiàn)代電子產(chǎn)品中不可或缺的一部分,它將電子元件組裝在一起,形成了一個完整的電子系統(tǒng)。其中,BGA和CSP是兩種常見的電子封裝技術(shù),它們各有優(yōu)缺點(diǎn),廣泛應(yīng)用于半導(dǎo)體制造、LCD顯示器等領(lǐng)域

2023-06-14 09:11:18 2824

2824

芯片封裝的發(fā)展歷程可以總結(jié)為七種類型:TO→DIP→SOP→QFP→PLCC→BGA→CSP。

2023-07-20 14:33:20 2232

2232 半導(dǎo)體器件有許多封裝形式,按封裝的外形、尺寸、結(jié)構(gòu)分類可分為引腳插入型、表面貼裝型和高級封裝三類。從DIP、SOP、QFP、PGA、BGA到CSP再到SIP,技術(shù)指標(biāo)一代比一代先進(jìn)。

2023-08-11 09:43:43 5233

5233

半導(dǎo)體器件有許多封裝形式,按封裝的外形、尺寸、結(jié)構(gòu)分類可分為引腳插入型、表面貼裝型和高級封裝三類。從DIP、SOP、QFP、PGA、BGA到CSP再到SIP,技術(shù)指標(biāo)一代比一代先進(jìn)。

2023-08-14 09:59:17 2723

2723

左右,同時CSP的抗噪能力強(qiáng),開關(guān)噪聲只有DIP(雙列直插式封裝)的1/2。這些主要電學(xué)性能指標(biāo)已經(jīng)接近裸芯片的水平,在時鐘頻率己超過雙G的高速通信領(lǐng)域,LSI芯片的CSP將是十分理想的選擇。

2023-08-20 09:42:07 4008

4008

CSP是近幾年才出現(xiàn)的一種集成電路的封裝形式,目前已有上百種CSP產(chǎn)品,并且還在不斷出現(xiàn)一些新的品種。盡管如此,CSP技術(shù)還是處于發(fā)展的初期階段,因此還沒有形成統(tǒng)一的標(biāo)準(zhǔn)。不同的廠家生產(chǎn)不同的CSP

2023-09-08 14:09:40 1230

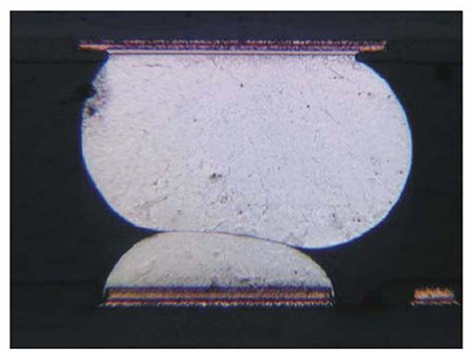

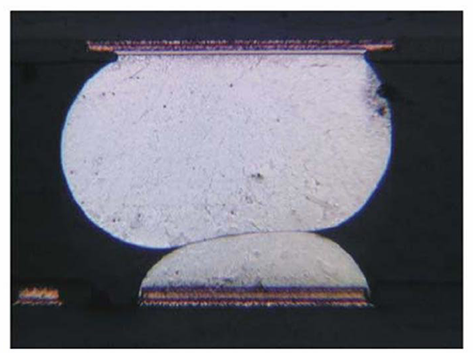

1230 BGA和CSP封裝技術(shù)詳解

2023-09-20 09:20:14 4692

4692

焊盤整理完成之后就可以重新貼裝元件了。這時我們又面臨了新的問題:如果選擇錫膏裝配的話,如何印刷錫膏呢?對于密間距的晶圓級CSP來說,這的確是一個難題。

2023-09-28 15:45:12 1277

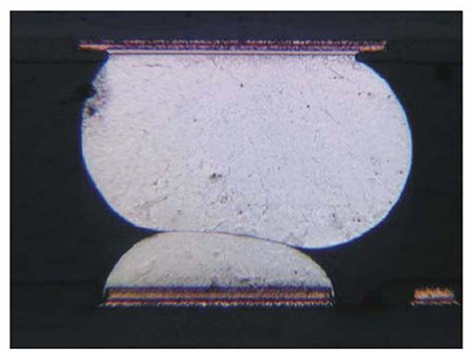

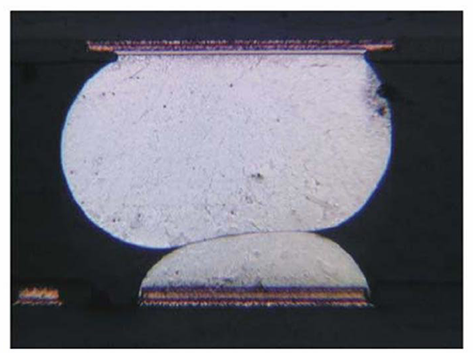

1277 簡要解讀BGA、CSP封裝中的球窩缺陷

2023-10-08 08:47:53 1615

1615

CSP的高效優(yōu)點(diǎn)體現(xiàn)在:用于板級組裝時,能夠跨出細(xì)間距(細(xì)至0.075mm)周邊封裝的界限,進(jìn)入較大間距(1,0.8,0.75,0.5,0.4mm)區(qū)域陣列結(jié)構(gòu)。 已有許多CSP器件在消費(fèi)類電信領(lǐng)域

2023-10-17 14:58:21 1347

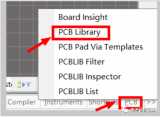

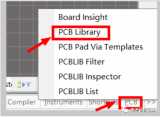

1347 雖然很多封裝都可以在網(wǎng)上找到,但是有些封裝還是需要自己動手來畫,可以直接看到成品圖,跟結(jié)構(gòu)校對也比較方便。

2023-10-23 09:14:14 25985

25985

為了實現(xiàn)集成電路芯片的電通路,一般需要將芯片裝配到在塑料或陶瓷載體上,這一過程可以稱為CSP。CSP的尺寸只是略大于芯片,通常封裝尺寸不大于芯片面積的1.5倍或不大于芯片寬度或長度的?1.2?倍

2023-12-22 09:08:31 4183

4183

在半導(dǎo)體封裝領(lǐng)域,很多封裝類型會使用到封裝基(載)板,比如BGA(Ball Grid Array),PGA,QFP,CSP,SiP,PoP等。

2023-12-25 09:49:06 4273

4273

立錡推出的低壓輸入、CSP 小封裝降壓轉(zhuǎn)換器系列,不僅滿足各式小型穿戴式和 IoT 物聯(lián)網(wǎng)應(yīng)用的需求,更在性能和尺寸上取得了絕佳平衡。

2024-03-14 15:03:10 1173

1173 隨著BGA、CSP封裝器件向密間距、微型化的方向發(fā)展,無鉛制程的廣泛應(yīng)用給電子裝聯(lián)工藝帶來了新的挑戰(zhàn)。球窩(Pillow-head Effect)缺陷是BGA、CSP類器件回流焊接中特有的一種缺陷

2024-04-10 09:08:24 1616

1616

瑞沃微CSP封裝技術(shù)在手機(jī)閃光燈照明領(lǐng)域具有廣泛的應(yīng)用前景和顯著的優(yōu)勢。隨著技術(shù)的不斷進(jìn)步和消費(fèi)者需求的不斷提升,瑞沃微CSP封裝技術(shù)將繼續(xù)在手機(jī)閃光燈照明領(lǐng)域發(fā)揮重要作用

2024-08-28 16:30:09 1242

1242 近日,納芯微正式推出了CSP封裝12V共漏極雙N溝道MOSFET——NPM12023A系列產(chǎn)品。這款新品以其優(yōu)異的短路過流能力與雪崩過壓能力,以及更強(qiáng)的機(jī)械壓力耐受能力,為便攜式鋰電設(shè)備的充放電提供了全面的保護(hù)。

2024-10-17 15:59:21 1391

1391 在半導(dǎo)體技術(shù)的快速發(fā)展中,封裝技術(shù)作為連接芯片與外部世界的橋梁,其重要性不言而喻。CSP(Chip Scale Package),即芯片級封裝技術(shù),正是近年來備受矚目的一種先進(jìn)封裝技術(shù)。今天,請跟隨瑞沃微的腳步,一起深入了解CSP芯片級封裝工藝的奧秘。

2024-11-06 10:53:34 4749

4749

納芯微正式發(fā)布全新一代CSP封裝12V共漏極雙N溝道MOSFET——NPM12017A系列,該系列產(chǎn)品是對納芯微已量產(chǎn)的CSP MOS的完美升級與補(bǔ)充。新一代CSP MOS進(jìn)一步優(yōu)化了性能表現(xiàn),顯著

2025-03-12 10:33:11 2854

2854 瑞沃微作為半導(dǎo)體封裝行業(yè)上先進(jìn)封裝高新技術(shù)企業(yè),對CSP(芯片級封裝)技術(shù)在不同領(lǐng)域的應(yīng)用有不同見解。CSP封裝憑借其極致小型化、高集成度和性能優(yōu)越性,在LED、SI基IC等領(lǐng)域展現(xiàn)出獨(dú)特優(yōu)勢,但也存在一定劣勢。

2025-05-16 11:26:25 1124

1124

瑞沃微CSP封裝光學(xué)技術(shù)憑借其極致小型化、高集成度、優(yōu)良電學(xué)性能和散熱性能,在照明、顯示及高端電子領(lǐng)域展現(xiàn)出顯著優(yōu)勢。

2025-06-24 16:54:18 645

645

在半導(dǎo)體產(chǎn)業(yè)的宏大版圖中,封裝技術(shù)作為連接芯片與應(yīng)用終端的關(guān)鍵紐帶,其每一次的革新都推動著電子產(chǎn)品性能與形態(tài)的巨大飛躍。當(dāng)下,瑞沃微的CSP先進(jìn)封裝技術(shù)在提升良率和量產(chǎn)成本方面展現(xiàn)出了突破傳統(tǒng)技術(shù)

2025-07-17 15:39:17 783

783

電子發(fā)燒友App

電子發(fā)燒友App

評論