為了實現集成電路芯片的電通路,一般需要將芯片裝配到在塑料或陶瓷載體上,這一過程可以稱為CSP。CSP的尺寸只是略大于芯片,通常封裝尺寸不大于芯片面積的1.5倍或不大于芯片寬度或長度的1.2倍。體積要比QFP和BGA小數倍,因此能在電路板上實現更高的元器件安裝密度。CSP還比QFP和PGA封裝有著更高的硅占比(硅與封裝面積的比例)。QFP的硅占比大約在10–60%,而CSP的單個芯片硅占比高達60–100%。

CSP和其他單片機封裝形式類似,也是通過引線鍵合和倒裝鍵合實現芯片與基板的互連。使用粘接劑將芯片與基板結合。CSP的封裝結構類型有引線框架CSP,剛性基板CSP,柔性基板CSP和晶圓級CSP。

引線框架CSP

引線框架CSP是一種常見CSP類型,可以實現無引腳封裝。引線框架CSP需要用到引線鍵合技術將芯片與銅引線框架基板連接到一起。在完成鍵合后芯片會被塑料封裝起來隔絕外界干擾。引線框架CSP的焊盤位于封裝的外邊緣,通過將CSP器件裸露的焊盤貼合到PCB焊盤的預涂覆錫膏上實現焊接安裝。

引線框架CSP與普通塑料封裝相比具有許多顯著優勢。由于封裝尺寸與芯片尺寸很接近電路徑得到進一步減小,因此改善了電氣性能。無插裝引腳使設備能夠采用標準SMT設備進行貼裝并使用錫膏焊接,更加節約了PCB的空間。

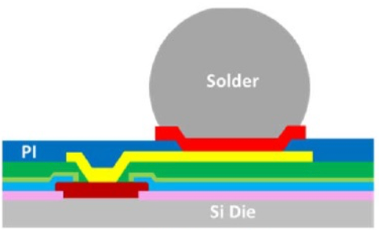

圖1.引線框架CSP結構。

剛性基板CSP和柔性基板CSP

剛性基板CSP采用的是陶瓷或塑料層壓板作為基板材料,例如雙馬來酰亞胺三嗪(BT)。柔性基片CSP是一種市場領先的技術,其芯片基板是用柔性材料制成的,可以是塑料薄膜。柔性基板CSP使用具有焊料球或金屬凸點的柔性電路作為芯片和下一層電路板之間的互連中介層。引線鍵合的柔性基板CSP在內存行業使用性很高。此外由于柔性基板能夠提供更靈活的布線能力,因此非常適用于高I/O的邏輯設備。

晶圓級CSP

晶圓級CSP顧名思義可以理解為在晶圓的時候就完成批量封裝,可以降低成本并提高產量。 在CSP的制造過程中需要重布I/O焊盤,涂覆聚合物薄膜,進行UBM制備和植球形成凸點。 然后制備了凸點的單個芯片會被封裝,在測試完成后被切割出來。重布焊盤是為了滿足焊料球的間距及排布要求。在重布焊盤和制備凸點時,能夠使用與制造IC的光刻工藝類似的光刻工藝。晶圓級CSP能應用在很多半導體設備,包括電源管理,閃存/EEPROM,集成無源網絡以及汽車電子元件。

圖2.晶圓級CSP結構。

深圳市福英達能夠提供半導體焊接用的錫膏產品,能夠用于集成電路芯片倒裝焊接和元器件表面貼裝等工藝。此外錫膏還能夠取代植球制備凸點。

審核編輯 黃宇

-

芯片

+關注

關注

463文章

54007瀏覽量

465952 -

集成電路

+關注

關注

5452文章

12571瀏覽量

374523 -

封裝

+關注

關注

128文章

9248瀏覽量

148614 -

CSP

+關注

關注

0文章

129瀏覽量

29485

發布評論請先 登錄

陶瓷片式電容器:從規格參數到封裝設計的全方位解析

詳解WLCSP三維集成技術

詳解芯片封裝的工藝步驟

風華高科貼片電感型號封裝尺寸

封裝業“成本分水嶺”——瑞沃微CSP如何讓傳統、陶瓷封裝漸成 “前朝遺老”?

扇出型晶圓級封裝技術的工藝流程

詳解芯片尺寸封裝(CSP)類型

詳解芯片尺寸封裝(CSP)類型

評論