晶心科技今天宣布推出AndesCore? 27系列處理器核心,成為RISC-V指令集架構(gòu)中領(lǐng)先支持向量擴(kuò)展架構(gòu)(RISC-V V-extension)的處理器。

2020-01-03 14:56:38 3521

3521 領(lǐng)先的嵌入式分析技術(shù)開發(fā)商UltraSoC日前宣布:其RISC-V處理器跟蹤解決方案開始全面供貨,這是業(yè)界首款商用RISC-V處理器跟蹤IP產(chǎn)品,也是RISC-V生態(tài)系統(tǒng)中關(guān)鍵的推動(dòng)性技術(shù)。該跟蹤功能的加入意味著UltraSoC可以提供最全面的RISC-V商業(yè)化調(diào)試解決方案。

2018-02-09 10:26:25 8281

8281 本文是RISC-V基礎(chǔ)知識(shí)的入門篇。介紹了開放式架構(gòu)理念,模塊化ISA的技術(shù)描述,以及一些商業(yè)RISC-V微處理器實(shí)現(xiàn)。 RISC-V開放式指令集架構(gòu)是當(dāng)今專有架構(gòu)(如ARM架構(gòu))的流行替代方案。自

2022-07-06 14:52:24 1647

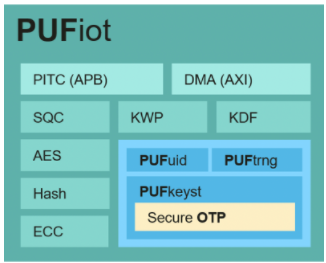

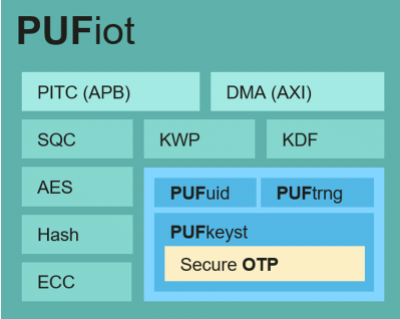

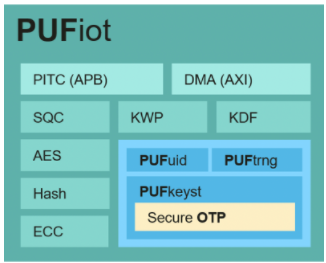

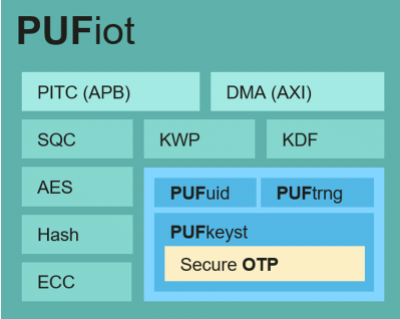

1647 為了保護(hù) IoT 應(yīng)用程序,PUFsecurity 利用芯片指紋技術(shù)來強(qiáng)化信任根,并開發(fā)了 PUFiot,這是一種具有廣泛安全邊界的安全協(xié)處理器,可以輕松地集成到安全的 RISC-V 系統(tǒng)中。

2022-08-16 09:31:11 2189

2189

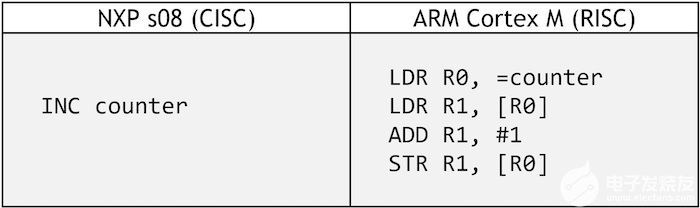

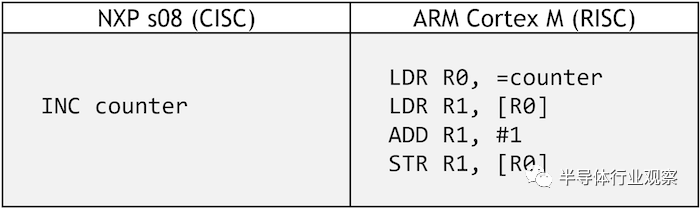

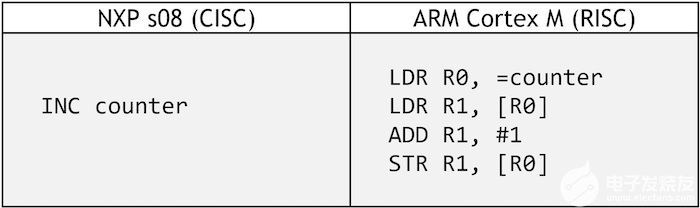

RISC-V、ARM 和x86微處理器之間的許多差異都很細(xì)微,并且與內(nèi)存尋址方式、分支執(zhí)行方式、異常處理方式等有關(guān)。本文將考慮更高層次的差異,并將簡(jiǎn)要比較精簡(jiǎn)指令集計(jì)算(RISC)和復(fù)雜指令集計(jì)算

2023-07-06 11:32:56 5796

5796

芯片設(shè)計(jì)工作中必不可少的就是IP核,為此不少企業(yè)推出了自己的RISC-V處理器IP。但單靠IP并不足以支撐龐大的RISC-V生態(tài),為了實(shí)現(xiàn)生態(tài)發(fā)展與統(tǒng)一,許多專注于RISC-V處理器IP的公司也各自發(fā)布了自己的對(duì)策。

2020-10-08 00:09:50 12504

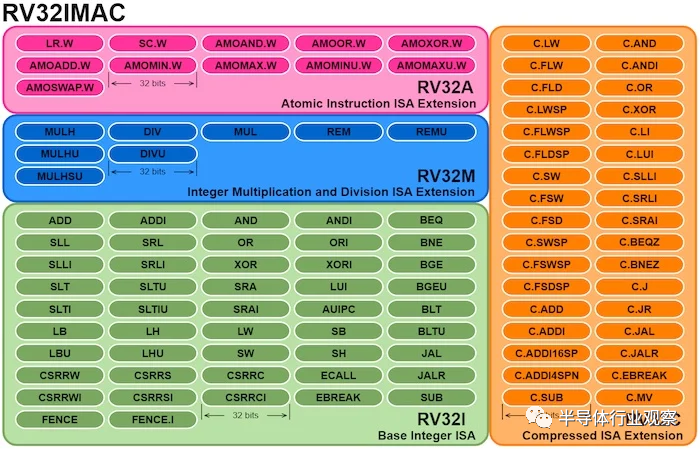

12504 RISC-V ISA 命名規(guī)范RISC-V ISA 采用模塊化的方式進(jìn)行組織,每一個(gè)模塊使用一個(gè)英文字母表示,其命名格式可以參考如下:RV[字寬][指令集模塊]RV:RISC-V字寬(處理器寄存器

2021-12-09 06:31:44

話下。

還有個(gè)Sipeed Longan Nano開發(fā)板,用的是SiFive的RISC-V處理器核心,給開發(fā)者提供了一個(gè)平臺(tái),能讓他們?nèi)ヌ剿?b class="flag-6" style="color: red">RISC-V架構(gòu)和應(yīng)用開發(fā)。這個(gè)開發(fā)板也能用來驗(yàn)證RISC-V MCU的性能和功能,推動(dòng)相關(guān)技術(shù)不斷往前發(fā)展。

2025-01-19 11:50:11

縮寫

[###]

用于標(biāo)識(shí)處理器位寬,取值[32, 64,128],也就是處理器的寄存器位寬

[abc...xyz]

標(biāo)識(shí)該處理器支持的指令模塊集合

比如:RV64IMAC, 表示64 位 RISC-V

2024-03-12 10:25:21

RISC-V處理器是開源的,那開發(fā)環(huán)境需要廠商自己開發(fā)還是沿用傳統(tǒng)的開發(fā)環(huán)境呢?比如keil

2024-01-13 19:18:35

精簡(jiǎn)指令集計(jì)算機(jī)。RISC-V是基于RISC原理建立的免費(fèi)開放指令集架構(gòu)(ISA),V是羅馬字母,代表第五代RISC(精簡(jiǎn)指令集計(jì)算機(jī)),可讀作RISC-FIVE。通過開放式標(biāo)準(zhǔn)協(xié)作實(shí)現(xiàn)處理器創(chuàng)新的新時(shí)代

2020-08-13 15:13:41

RISC-V和開源處理器之間是什么關(guān)系?

2023-03-09 10:06:52

本文是RISC-V基礎(chǔ)知識(shí)的入門篇。介紹了開放式架構(gòu)理念,模塊化ISA的技術(shù)描述,以及一些商業(yè)RISC-V微處理器實(shí)現(xiàn)。RISC-V開放式指令集架構(gòu)是當(dāng)今專有架構(gòu)(如ARM架構(gòu))的流行替代方案。自

2022-12-23 17:51:49

本期文章目錄一個(gè)小型RISC-V開源處理器核介紹!#SOC#FPGA#RISC-V點(diǎn)擊閱讀數(shù)字積木從零開始寫RISC-V處理器(超詳細(xì))#RISC-V點(diǎn)擊閱讀數(shù)字積木為什么說模擬工程...

2021-07-23 09:42:00

RISC-V是什么?有哪些特點(diǎn)?如何去設(shè)計(jì)RISC-V處理器?

2021-06-18 09:24:03

面積降低制造成本,實(shí)現(xiàn)低功耗的微處理器,也可以用于實(shí)現(xiàn)高性能的應(yīng)用處理器。他進(jìn)一步指出,通過RISC-V,全球可以創(chuàng)建一個(gè)充滿活力的生態(tài)系統(tǒng),集合設(shè)計(jì)工具硬件軟件等,以經(jīng)濟(jì)高效的方式進(jìn)入迅速發(fā)展的新興市場(chǎng)

2020-06-22 16:55:03

模塊化設(shè)計(jì)提高了RISC-V的適應(yīng)性和靈活性。

簡(jiǎn)潔的指令集:RISC-V的設(shè)計(jì)簡(jiǎn)潔,指令數(shù)量相對(duì)較少,這有助于提高處理器的執(zhí)行速度和降低功耗。

強(qiáng)大的社區(qū)支持:RISC-V擁有龐大的社區(qū)支持,包括學(xué)術(shù)界

2024-04-28 09:03:24

。這種模塊化設(shè)計(jì)提高了RISC-V的適應(yīng)性和靈活性。

簡(jiǎn)潔的指令集 :RISC-V的設(shè)計(jì)簡(jiǎn)潔,指令數(shù)量相對(duì)較少,這有助于提高處理器的執(zhí)行速度和降低功耗。

強(qiáng)大的社區(qū)支持 :RISC-V擁有龐大的社區(qū)支持

2024-04-28 08:51:42

RISC-V架構(gòu) RISC-V(發(fā)音為“risk-five”)是一個(gè)基于精簡(jiǎn)指令集(RISC)原則的開源指令集架構(gòu)(ISA)。 與大多數(shù)指令集相比,RISC-V指令集可以自由地用于任何目的

2023-04-03 15:29:09

或許可費(fèi)。這確保了ARM的穩(wěn)定性和可靠性,以及高質(zhì)量的技術(shù)支持和生態(tài)系統(tǒng)。

指令集與實(shí)現(xiàn)

RISC-V :RISC-V是一種模塊化的架構(gòu),由一個(gè)基本指令集和多個(gè)可選指令集擴(kuò)展組成。這允許RISC-V根據(jù)

2024-05-27 15:58:04

公司從成立之初就一直堅(jiān)持使用自主產(chǎn)權(quán)的內(nèi)核和MCU所需要的各種IP。雖然通過技術(shù)研發(fā)創(chuàng)新來實(shí)現(xiàn)微處理器的自主可控十分艱難,但堅(jiān)持下來的價(jià)值和優(yōu)勢(shì)也十分明顯。針對(duì)目前RISC-V MCU的發(fā)展痛點(diǎn),愛普特

2023-04-05 12:16:42

RISC-V架構(gòu)秉承簡(jiǎn)單的設(shè)計(jì)哲學(xué)。體現(xiàn)為:在處理器領(lǐng)域,主流的架構(gòu)為x86與ARM架構(gòu)。x86與ARM架構(gòu)的發(fā)展的過程也伴隨了現(xiàn)代處理器架構(gòu)技術(shù)的不斷發(fā)展成熟,但作為商用的架構(gòu),為了能夠保持架構(gòu)的向后兼容性

2021-06-18 19:41:21

RISC-V簡(jiǎn)介??RISC-V 是一個(gè)自由和開放的 ISA(開源指令集架構(gòu)),通過開放的標(biāo)準(zhǔn)協(xié)作實(shí)現(xiàn)處理器創(chuàng)新的新時(shí)代。RISC-V ISA在架構(gòu)上提供了一個(gè)新的自由、可擴(kuò)展的軟件和硬件自由級(jí)別

2023-02-27 19:56:30

10 月 19 日,2021 云棲大會(huì)上,平頭哥開源了玄鐵RISC-V系列處理器,并開放了工具及系統(tǒng)軟件。這次的開源對(duì)國(guó)內(nèi)的RISC-V生態(tài)圈具有非常重要的意義。關(guān)注了一下這次開源發(fā)布的東...

2022-02-28 08:15:04

計(jì)算機(jī)由控制整體的CPU(中央處理器)和加速器兩部分構(gòu)成。在AI計(jì)算中,功耗和效率是兩個(gè)關(guān)鍵因素。RISC-V架構(gòu)通過其簡(jiǎn)潔的設(shè)計(jì)和定制化的擴(kuò)展,可以實(shí)現(xiàn)高效的能量使用。該架構(gòu)能夠通過小型且高效的處理單元

2024-10-31 16:06:57

能與RISC-V的起步較晚、生態(tài)系統(tǒng)支持不足等因素有關(guān)。為了進(jìn)一步提高市場(chǎng)份額和認(rèn)可度,RISC-V需要不斷加強(qiáng)自身的技術(shù)實(shí)力和生態(tài)建設(shè)。

4. 技術(shù)挑戰(zhàn)

技術(shù)復(fù)雜性和實(shí)現(xiàn)難度:盡管RISC-V

2024-07-29 17:18:30

、RISC-V在人工智能圖像處理中的應(yīng)用案例

目前,已有多個(gè)案例展示了RISC-V在人工智能圖像處理中的應(yīng)用潛力。例如:

Esperanto技術(shù)公司 :該公司制造的首款高性能RISC-V AI處理器旨在

2024-09-28 11:00:52

RISC-V是一個(gè)開源的指令集架構(gòu),它屬于一個(gè)開放的、非營(yíng)利性質(zhì)的基金會(huì),而基金會(huì)將謹(jǐn)慎地發(fā)展和維護(hù)這個(gè)開源的指令集架構(gòu)。 計(jì)算機(jī)體系結(jié)構(gòu)的傳統(tǒng)方法是增量ISA,新處理器不僅必須實(shí)現(xiàn)新的ISA擴(kuò)展,還必須實(shí)現(xiàn)

2023-03-30 16:40:41

自己特色,根據(jù)不同用途有不同型號(hào)的處理器架構(gòu)。 關(guān)于RISC-V RISC:Reduced Instruction Set Computer,即精簡(jiǎn)指令集計(jì)算機(jī)。 RISC-V是基于RISC原理建立

2021-04-25 09:13:19

設(shè)計(jì)RISC微處理器需要遵循哪些原則?基于FPGA技術(shù)用VHDL語言實(shí)現(xiàn)的8位RISC微處理器

2021-04-13 06:11:51

MIPS Technologies不再設(shè)計(jì)MIPS處理器。相反,它加入了RISC-V陣營(yíng),放棄了具有悠久歷史和技術(shù)聯(lián)系的同名架構(gòu)。此舉顯然預(yù)示著MIPS作為CPU系列的終結(jié),并進(jìn)一步減少了可用處理器

2021-03-09 19:30:07

位 FPU,以及兩顆來自美光的 16GB HBM2e 內(nèi)存。處理器的內(nèi)核通過中介層實(shí)現(xiàn)互連,雙塊 CPU 可提供 0.75 FP64 TFLOPS 的性能和 6 FP8 TFLOPS 算力。那么Occamy RISC-V 前景如何呢?

2023-05-13 08:44:36

的處理器指令集,是構(gòu)建芯片生態(tài)和發(fā)展芯片技術(shù)的核心部分,其重要性不言而喻。在此背景下,RISC-V有望成為新的選擇。盡管具有通用、開放與免費(fèi)的先期優(yōu)勢(shì),但相比已經(jīng)成熟的Arm和Intel x86,國(guó)內(nèi)

2020-11-14 09:26:41

瑞薩電子推出圍繞64位RISC-V CPU內(nèi)核構(gòu)建的RZ/5個(gè)通用微處理器單元(MPU),具體的型號(hào)是多少?性能怎么樣?

2024-01-11 13:03:31

,創(chuàng)建實(shí)現(xiàn)自有加速器算法的自定義異構(gòu)集群。RISC-V作為一種ISA,我們一開始是在處理器內(nèi)核中采用吸引人的通用構(gòu)建塊,然后在此基礎(chǔ)上進(jìn)行構(gòu)建,同時(shí)還利用最好的商業(yè)工具增強(qiáng)使用者的信心。所以,IP

2024-11-26 20:20:35

本文描述了RISC-V非特權(quán)體系結(jié)構(gòu)。標(biāo)記為“已批準(zhǔn)”的ISA模塊此時(shí)已被批準(zhǔn)。標(biāo)記為凍結(jié)的模塊,在提交批準(zhǔn)之前,預(yù)計(jì)不會(huì)有重大變化。標(biāo)記的模塊草案有望在批準(zhǔn)前修改。本文件包含RISC-V ISA模塊的以下版本:

2020-08-28 14:57:40

(Integer)指令集用字母“ I ”表示,這是RISC-V處理器最基本也是唯一強(qiáng)制要求實(shí)現(xiàn)的指令集。其他指令集均為可選模塊,可自行選擇是否支持。RISC-V指令模塊描述如下:類型指令集指令數(shù)狀態(tài)描述

2023-03-28 16:57:06

,然后返回到內(nèi)存中。RISC-V 和 ARM 都支持 32 位或 64 位指令集。

二、RISC-V 和 ARM 的區(qū)別

盡管 RISC-V 和 ARM 處理器技術(shù)的功能相似,但也有顯著區(qū)別。

1.

2023-06-21 20:31:32

RISC-V(“RISC five”)的目標(biāo)是成為一個(gè)通用的指令集架構(gòu)(ISA):①、它要能適應(yīng)包括從最袖珍的嵌入式控制器,到最快的高性能計(jì)算機(jī)等各種規(guī)模的處理器。②、它應(yīng)該能兼容各種流行的軟件棧

2024-07-27 15:05:23

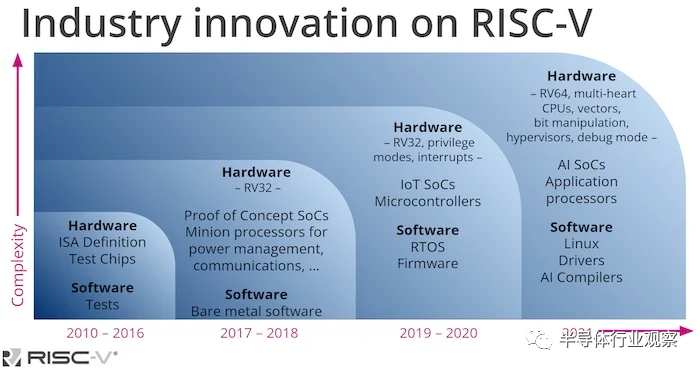

RISC-V是一種開放式ISA(指令集體系結(jié)構(gòu)),為處理器體系結(jié)構(gòu)的創(chuàng)新開創(chuàng)了新紀(jì)元。RISC-V基金會(huì)由325多家成員公司組成。這是該技術(shù)的主要優(yōu)勢(shì)。軟件架構(gòu)師/固件工程師/軟件開發(fā)

2020-07-27 17:38:30

來源:liangkangnan的博客更新于 2021-01-31tinyriscv 一個(gè)從零開始寫的極簡(jiǎn)易懂的RISC-V處理器核從零開始寫RISC-V處理器之一 前言從零開始寫RISC-V處理器

2022-08-22 18:25:55

分析/監(jiān)控工具成了處理器開發(fā)時(shí)必不可少的軟件。盡管RISC-V的ISA規(guī)范已經(jīng)定義了硬件性能監(jiān)控(HPM),但總體支持程度上仍未完善。就以Linux上的性能分析工具Perf為例,該工具可以借助PMU

2021-12-27 08:00:00

解RISC-V與開源處理器。以下為幾個(gè)要點(diǎn):指令集規(guī)范(Specification)和處理器實(shí)現(xiàn)(Implementation)是兩個(gè)不同層次的概念,要區(qū)分開。指令集(ISA)是規(guī)范標(biāo)準(zhǔn),往往用一本書或幾張紙

2020-06-22 16:47:55

RISC-V指令集體系結(jié)構(gòu)(ISA)易于擴(kuò)展,并且沒有指定關(guān)于特定RISC-V微控制器或片上系統(tǒng)(SoC)實(shí)現(xiàn)的所有內(nèi)容。因此,F(xiàn)reeRTOS RISC-V移植也是可擴(kuò)展的-它提供了一個(gè)處理所有

2019-11-29 15:54:41

,并涌現(xiàn)了眾多開源處理器及SoC采用RISC-V架構(gòu),這些處理器既有標(biāo)量處理器,也有超標(biāo)量處理器,既有單核處理器,也有多核處理器,本文接下來將簡(jiǎn)單介紹RISC-V架構(gòu)的基本設(shè)計(jì),隨后將詳細(xì)描述目前采用

2020-07-27 18:09:27

使用,同時(shí)也容許企業(yè)添加自有指令集拓展而不必開放共享以實(shí)現(xiàn)差異化發(fā)展。 架構(gòu)簡(jiǎn)單 RISC-V架構(gòu)秉承簡(jiǎn)單的設(shè)計(jì)哲學(xué)。體現(xiàn)為: 在處理器領(lǐng)域,主流的架構(gòu)為x86與ARM架構(gòu)。x86與ARM架構(gòu)的發(fā)展的過程

2023-03-19 10:52:16

協(xié)處理器進(jìn)行g(shù)pio操作,執(zhí)行完成后 ULP RISC-V 協(xié)處理器退出,等待下一個(gè)ULP喚醒周期。可當(dāng)在主MCU程序中使能 esp_sleep_enable_ulp_wakeup() 函數(shù)后,每當(dāng)

2023-02-09 06:52:26

推動(dòng)未來的指令集體系結(jié)構(gòu)(ISA)的演進(jìn)。活動(dòng)會(huì)議的特色是主要的技術(shù)公司和研究機(jī)構(gòu)討論:RISC-V體系結(jié)構(gòu)、商業(yè)和開源實(shí)施、軟件和硅半導(dǎo)體、向量和安全、應(yīng)用程序和加速器、模擬基礎(chǔ)設(shè)施等。訪問事件處理

2020-08-02 11:50:33

精簡(jiǎn)指令集計(jì)算機(jī)。RISC-V是基于RISC原理建立的免費(fèi)開放指令集架構(gòu)(ISA),V是羅馬字母,代表第五代RISC(精簡(jiǎn)指令集計(jì)算機(jī)),可讀作RISC-FIVE。通過開放式標(biāo)準(zhǔn)協(xié)作實(shí)現(xiàn)處理器創(chuàng)新的新時(shí)代

2019-07-29 07:57:16

如題,現(xiàn)在risc-v發(fā)展的如此迅猛,不知道這些處理器主要應(yīng)用在哪些行業(yè)比較多呢?

2023-12-09 18:37:01

我在ULP RISC-V協(xié)處理器的例程中,沒有發(fā)現(xiàn)有對(duì)ADC的操作,請(qǐng)問RISC-V協(xié)處理器目前還不支持嗎?使用的IDF版本為4.4.2。我想在ULP模式下,通過ADC來讀取外部器件的數(shù)據(jù)。

2023-02-13 06:34:36

我在ULP RISC-V協(xié)處理器的例程中,沒有發(fā)現(xiàn)有對(duì)ADC的操作,請(qǐng)問RISC-V協(xié)處理器目前還不支持嗎?使用的IDF版本為4.4.2。我想在ULP模式下,通過ADC來讀取外部器件的數(shù)據(jù)。

2023-03-06 06:33:44

本帖最后由 余一yui 于 2023-4-26 10:44 編輯

《玄鐵RISC-V處理器入門與實(shí)戰(zhàn)》是一本介紹開源ISA(指令集架構(gòu))RISC-V的電子書。RISC-V是由加州大學(xué)伯克利分校

2023-04-12 11:16:58

的授權(quán),同時(shí)會(huì)產(chǎn)生一些費(fèi)用,這也帶來了一個(gè)問題:假如有一天ARM公司不授權(quán)怎么辦?RISC-V架構(gòu)就是為了解決這個(gè)問題的!RISC-V最早在2010年起源于加州大學(xué)伯克利分校,由于受夠了現(xiàn)有處理器架構(gòu)

2023-04-14 22:10:56

面臨應(yīng)用碎片化、開發(fā)效率低、軟硬件適配難等問題,軟硬件生態(tài)尚未成熟。玄鐵RISC-V系列處理器采用自研技術(shù),覆蓋從低功耗到高性能的各類場(chǎng)景,支持AliOS、FreeRTOS、RT-Thread

2021-10-20 14:09:00

https://github.com/JiaoXianjun/XiangShan談到RISC-V,應(yīng)該都會(huì)想到香山處理器。其經(jīng)歷了幾代的演進(jìn),性能越來越高。采用Chisel Rocketchip框架,能夠方便的定制屬于你的RISC-V處理器。對(duì)此,你有什么看法?

2023-04-14 15:51:59

英國(guó)劍橋—2017年7月3日—領(lǐng)先的嵌入式分析技術(shù)開發(fā)商UltraSoC日前宣布:公司已經(jīng)開發(fā)出處理器跟蹤技術(shù),可支持基于開源RISC-V架構(gòu)的產(chǎn)品。UltraSoC公司已經(jīng)為處理器跟蹤技術(shù)

2017-07-03 16:14:54 1046

1046 合作,努 力延續(xù)這一不可思議的發(fā)展勢(shì)頭,集結(jié)軟硬件創(chuàng)新人士加入這個(gè)開放、協(xié)作的社區(qū),借助RISC-V生態(tài)系統(tǒng)實(shí)現(xiàn)嶄新的處理器創(chuàng)新水平。”

RISC-V基金會(huì)董事會(huì)主席Krste

2018-11-08 11:39:11 8976

8976 領(lǐng)先的嵌入式分析技術(shù)開發(fā)商UltraSoC日前宣布:其RISC-V處理器跟蹤解決方案開始全面供貨,這是業(yè)界首款商用RISC-V處理器跟蹤IP產(chǎn)品,也是RISC-V生態(tài)系統(tǒng)中關(guān)鍵的推動(dòng)性技術(shù)。

2019-12-05 14:24:31 1120

1120 大型技術(shù)公司已開始涉足RISC-V,該技術(shù)以免費(fèi)標(biāo)準(zhǔn)代替了芯片設(shè)計(jì)過程中的關(guān)鍵專有技術(shù)。盡管RISC-V還處于初期階段,但利用RISC-V卻可能會(huì)創(chuàng)造出一批新的處理器,這些處理器可以與英特爾的產(chǎn)品進(jìn)行競(jìng)爭(zhēng),還可以削弱Arm的授權(quán)業(yè)務(wù)。

2020-02-20 16:57:29 3615

3615 Silicon Labs首席技術(shù)官Alessandro Piovaccari 關(guān)于RISC-V架構(gòu)的理解Alessandro: RISC-V是一種指令集架構(gòu)(ISA),不關(guān)注RISC-V處理器微架構(gòu)

2020-06-08 16:48:05 9159

9159 隨著這些年的發(fā)展,RISC-V的受重視程度與與日俱增。這主要因?yàn)樗敲赓M(fèi)的、靈活的,并且速度很快。這使RISC-V成為許多開發(fā)人員的安全便捷選擇。但是您會(huì)認(rèn)為RISC-V是通用RISC處理器還是定制的隨心所欲處理器?

2020-11-17 16:11:56 4207

4207 對(duì)x86處理器來說,開源的RISC-V處理器威脅越來越大,它不僅能實(shí)現(xiàn)5GHz的超高頻率,現(xiàn)在多核并行上也甩開了x86,Esperanto公司已經(jīng)實(shí)現(xiàn)了1000多核RISC-V處理器。

2020-12-10 09:23:12 2881

2881 對(duì)x86處理器來說,開源的RISC-V處理器威脅越來越大,它不僅能實(shí)現(xiàn)5GHz的超高頻率,現(xiàn)在多核并行上也甩開了x86,Esperanto公司已經(jīng)實(shí)現(xiàn)了1000多核RISC-V處理器。

2020-12-10 14:12:32 1352

1352 最近一直在學(xué)習(xí)有關(guān)RISC-V指令集體系結(jié)構(gòu)(ISA)的更多信息,以下是作者對(duì)RISC-V ISA最印象深刻的一些方面:1.這是一個(gè)RISC指令集,它很小且易于學(xué)習(xí)(基礎(chǔ)為47個(gè))。對(duì)于任何對(duì)學(xué)習(xí)微處理器感興趣的人都非常友好。 2.大學(xué)中用于數(shù)字設(shè)計(jì)教學(xué)的主導(dǎo)架構(gòu)。 3.它經(jīng)

2020-12-31 10:20:00 5477

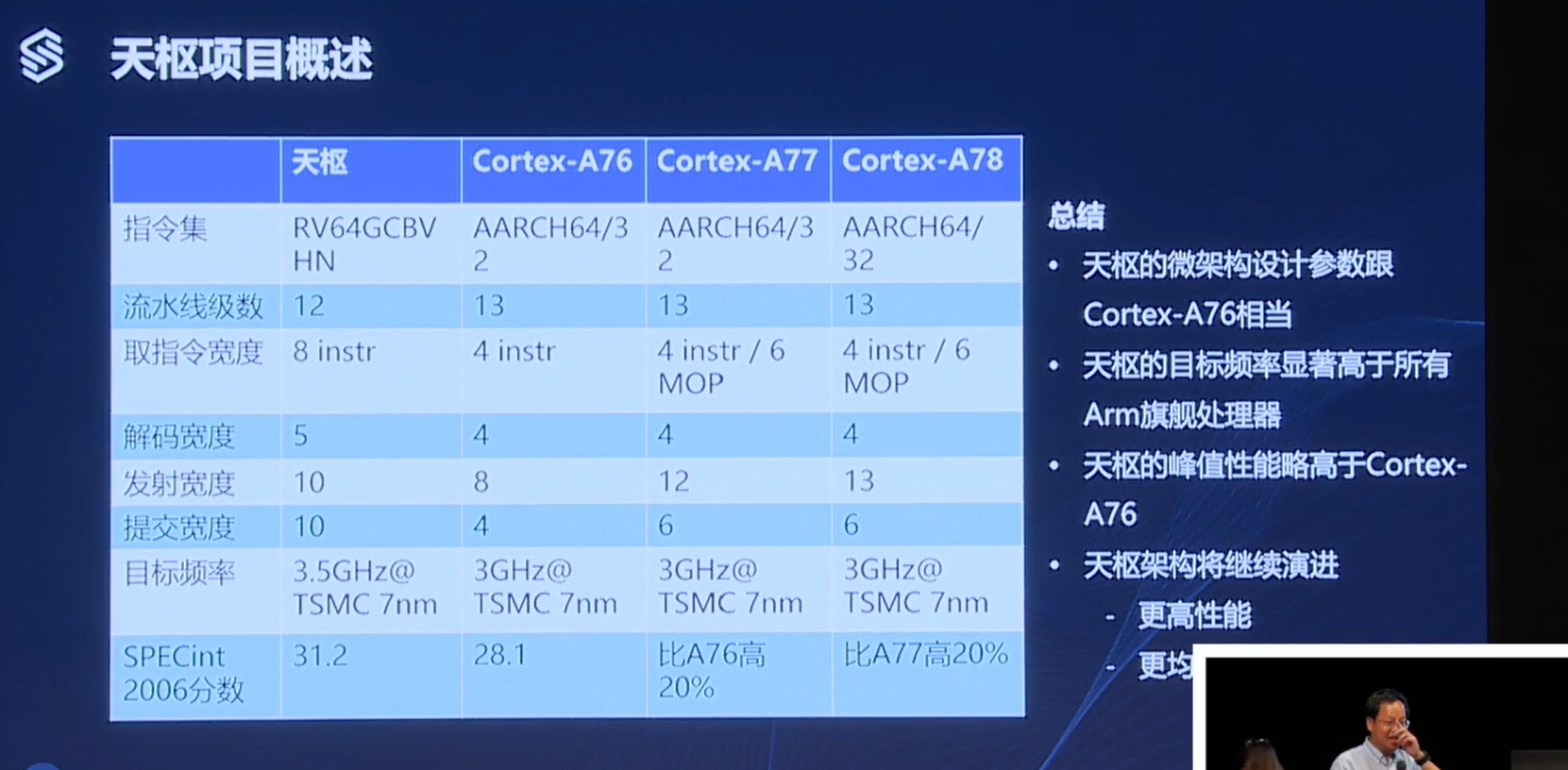

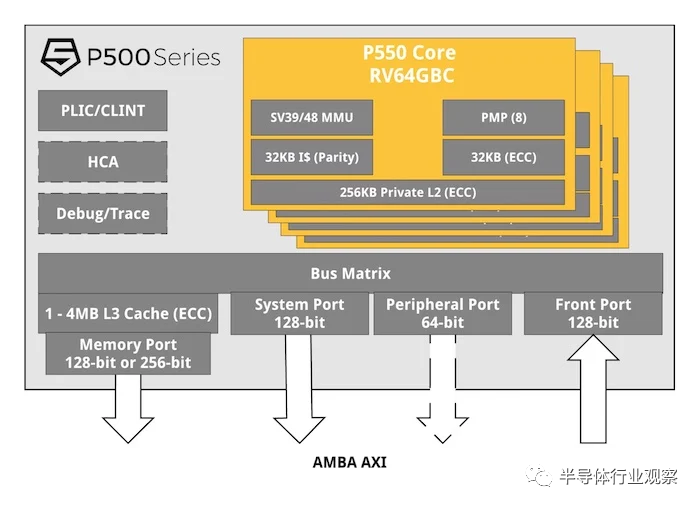

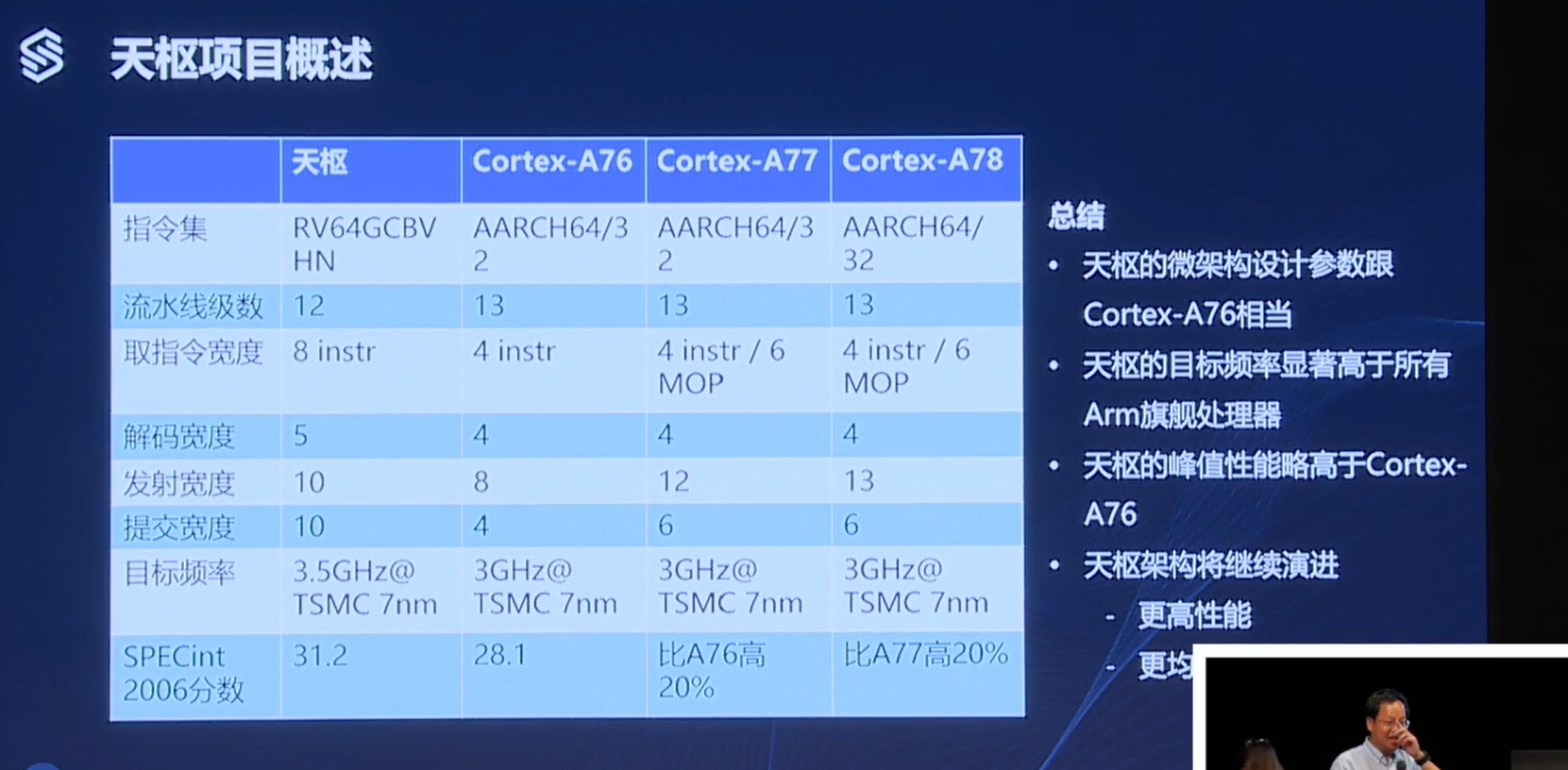

5477 首屆risc-v峰會(huì)在上海正式舉辦,以下內(nèi)容是賽昉科技天樞項(xiàng)目的介紹,分別從微架構(gòu)、應(yīng)用場(chǎng)景以及典型用法幾個(gè)方面分析這款高性能RISC-V處理器。

2021-06-22 17:36:34 3855

3855

RISC-V ISA 命名規(guī)范RISC-V ISA 采用模塊化的方式進(jìn)行組織,每一個(gè)模塊使用一個(gè)英文字母表示,其命名格式可以參考如下:RV[字寬][指令集模塊]RV:RISC-V字寬(處理器寄存器

2021-11-26 16:36:13 6

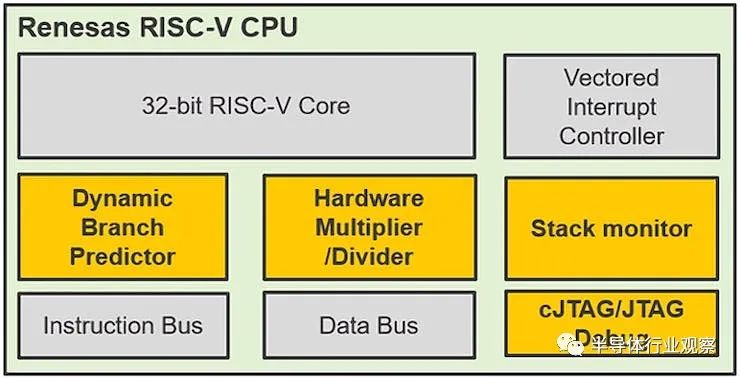

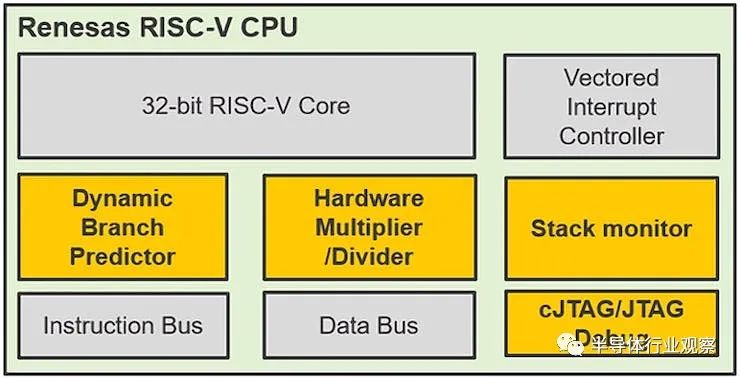

6 全球半導(dǎo)體解決方案供應(yīng)商瑞薩電子集團(tuán)(TSE:6723)今日宣布,推出基于64位RISC-V CPU內(nèi)核的RZ/Five通用微處理器(MPU)——RZ/Five采用Andes AX45MP

2022-03-02 10:13:02 1322

1322 RISC-V是這兩年才開始迅速發(fā)展的,因此關(guān)于RISC-V的學(xué)習(xí)參考資料目前還很少,特別是適合入門的資料,因此學(xué)習(xí)起來進(jìn)度很緩慢,于是萌生了自己從零開始寫RISC-V處理器核的想法。 本人是一名FPGA小白,為了快速入門、深入掌握RISC-V,我開始了學(xué)習(xí)FPGA和verilog的"艱難&am

2022-03-17 09:46:39 116

116 為了保護(hù) IoT 應(yīng)用程序,PUFsecurity 利用芯片指紋技術(shù)來強(qiáng)化信任根,并開發(fā)了 PUFiot,這是一種具有廣泛安全邊界的安全協(xié)處理器,可以輕松集成到安全的 RISC-V 系統(tǒng)中。

2022-06-01 11:06:19 4279

4279

本文是 RISC-V 基礎(chǔ)知識(shí)的入門讀物。公開了開放式架構(gòu)理念,以及模塊化 ISA 的技術(shù)描述,以及一些商業(yè) RISC-V 微處理器實(shí)現(xiàn)。 RISC-V 開放指令集架構(gòu)是當(dāng)今可用的專有架構(gòu)(例如

2022-08-25 17:10:57 3676

3676

抽象-RISC-V是一種開放ISA(指令集架構(gòu))實(shí)現(xiàn)了處理器架構(gòu)創(chuàng)新的新時(shí)代。RISC-V包括開源處理器內(nèi)核、工具鏈、,模擬器和其他關(guān)鍵支持組件。RISC-V生態(tài)系統(tǒng)使處理器創(chuàng)新達(dá)到新水平體系結(jié)構(gòu)將是實(shí)現(xiàn)所需收益的關(guān)鍵驅(qū)動(dòng)因素未來十年的性能和能效。

2022-11-23 16:56:56 4

4 太空級(jí)處理器。 NOEL-V 是一個(gè)實(shí)現(xiàn) RISC-V 架構(gòu)的處理器的可綜合 VHDL 模型。該模型可高度配置,提供了從高性能支持 Linux 架構(gòu)到面積優(yōu)化的微控制器解決方案等配置。不僅如此,NOEL-V 設(shè)計(jì)還包含容錯(cuò)功能,自動(dòng)糾

2022-12-23 17:15:52 2748

2748 英特爾的 x86 或 ARM 的 RISC 處理器的專有 ISA 一直是 Apple、戴爾、三星等 OEM 的選擇,但現(xiàn)在為什么我們需要像 RISC-V 這樣的開放 ISA,而不是所有這些經(jīng)過充分驗(yàn)證的ISA。

2022-12-27 09:10:31 5574

5574 自從RISC-V 2015年公開發(fā)布以來,它作為一種開放、協(xié)作和可擴(kuò)展的微處理器獲得了大量關(guān)注。相比其它專有處理器架構(gòu),RISC-V確保任何人都可以使用該架構(gòu)來促進(jìn)工程和計(jì)算社區(qū)的開發(fā)和增長(zhǎng)。

2023-01-06 10:58:01 1559

1559 處理器驗(yàn)證是一個(gè)全新的領(lǐng)域。我們知道 Arm 和 Intel 對(duì)處理器質(zhì)量的期望設(shè)置了很高的標(biāo)準(zhǔn)。在 RISC-V 中,我們必須嘗試并遵循這一點(diǎn)。

2023-03-22 15:19:32 1001

1001 的客戶現(xiàn)在可以根據(jù)同一授權(quán)協(xié)議和合同去購(gòu)買一系列精選的SmartDV外設(shè)IP的授權(quán)。這一合作伙伴關(guān)系支持使用Codasip RISC-V處理器的芯片設(shè)計(jì)人員,通過使用已驗(yàn)證過兼容性和集成便捷性等特性

2023-07-03 16:13:04 1320

1320 RISC-V的開放性允許定制和擴(kuò)展基于 RISC-V 內(nèi)核的架構(gòu)和微架構(gòu),以滿足特定需求。這種對(duì)設(shè)計(jì)自由的渴望也正在將驗(yàn)證部分的職責(zé)轉(zhuǎn)移到不斷壯大的開發(fā)人員社群。然而,隨著越來越多的企業(yè)和開發(fā)人員轉(zhuǎn)型RISC-V,大家才發(fā)現(xiàn)處理器驗(yàn)證絕非易事。

2023-07-10 09:42:08 1469

1469

為什么IAR編譯器對(duì)開源ISA:RISC-V業(yè)務(wù)至關(guān)重要? 演講ppt分享

2023-07-14 17:15:32 2

2 嵌入式硬件專家瑞薩電子宣布推出首款基于免費(fèi)開放的 RISC-V 指令集架構(gòu) (ISA) 的完全自主研發(fā)的處理器內(nèi)核。

2023-12-01 17:28:18 2346

2346

RISC-V不僅僅是一個(gè)流行語;它建立在堅(jiān)實(shí)的技術(shù)基礎(chǔ)之上,使其有別于其他指令集架構(gòu) (ISA)。RISC-V的核心是基于精簡(jiǎn)指令集計(jì)算(RISC)原則,強(qiáng)調(diào)效率和性能。

2024-03-26 09:34:12 5729

5729 FPGA(現(xiàn)場(chǎng)可編程門陣列)和RISC-V處理器在多個(gè)方面存在顯著的區(qū)別。

2024-03-27 14:21:11 2498

2498 4月2日,RED Semiconductor(以下簡(jiǎn)稱 "RED")宣布推出算法微處理器 ISA(指令集架構(gòu))和硬件設(shè)計(jì) VISC,將 RISC-V 的功能擴(kuò)展到邊緣人工智能、自動(dòng)駕駛和密碼學(xué)領(lǐng)域。

2024-04-03 17:31:22 1433

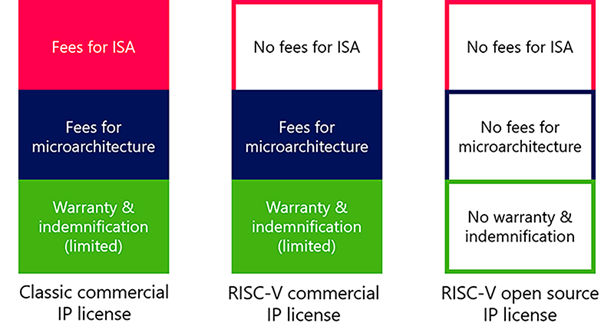

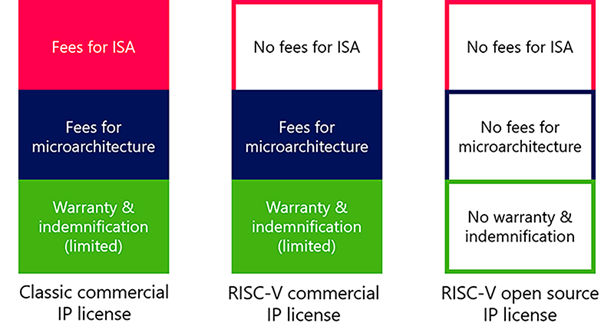

1433 RISC-V 是一個(gè)開放的 ISA,任何人都可以接受它并實(shí)現(xiàn)處理器。但RISC-V市場(chǎng)的領(lǐng)導(dǎo)者知道,僅僅因?yàn)樗麄儾恍枰Ц对S可使用費(fèi),并不意味著RISC-V是便宜的選擇。

2024-04-15 11:34:17 1516

1516

RISC-V創(chuàng)新應(yīng)用論壇RISC-V@ExhibitorForumRISC-V已迅速成為世界范圍內(nèi)處理器設(shè)計(jì)和實(shí)現(xiàn)領(lǐng)域領(lǐng)先的標(biāo)準(zhǔn)指令集架構(gòu)(ISA)。與專有架構(gòu)不同,RISC-V是一種向任何人開放

2024-06-13 08:36:29 1034

1034

ARM和RISC-V同為精簡(jiǎn)指令集(RISC)架構(gòu),這意味著它們都基于相似的設(shè)計(jì)理念:通過簡(jiǎn)化指令集來提高處理器的效率和執(zhí)行速度。然而,即使同為RISC架構(gòu),ARM和RISC-V的指令集在設(shè)計(jì)細(xì)節(jié)

2024-09-10 09:26:15 2463

2463 1.前言RISC-V旨在支持廣泛的定制和專業(yè)化。RISC-V的ISA是由一個(gè)基本整型ISA和其它對(duì)基本ISA的可選擴(kuò)展組成。每個(gè)整型ISA可以使用一個(gè)或多個(gè)可選的ISA擴(kuò)展進(jìn)行擴(kuò)展。基本整型ISA

2024-11-12 01:08:33 2099

2099

Andes晶心科技(TWSE:6533; SIN US03420C2089; ISIN:US03420C1099)是全球高效能、低功耗 32/64 位 RISC-V 處理器的領(lǐng)導(dǎo)廠商,也是

2024-12-26 10:54:03 1617

1617 人工智能、自動(dòng)駕駛汽車等技術(shù)正迅速發(fā)展,市場(chǎng)對(duì)定制可擴(kuò)展處理器的需求也隨之不斷攀升。RISC-V開放標(biāo)準(zhǔn)指令集架構(gòu)(ISA)以其模塊化設(shè)計(jì)和協(xié)作社區(qū),引領(lǐng)了處理器設(shè)計(jì)新潮流,助力實(shí)現(xiàn)技術(shù)愿景。相應(yīng)

2025-02-10 16:52:08 1174

1174

Condor 是一家美國(guó)初創(chuàng)企業(yè),致力于開發(fā)高性能 RISC-V 微處理器。公司的目標(biāo)是通過創(chuàng)新技術(shù)徹底革新整個(gè)行業(yè),打破高性能計(jì)算的極限。

2025-05-08 09:03:34 880

880 沁恒微電子邀您共襄盛舉沁恒微電子專注于連接技術(shù)和微處理器內(nèi)核研究,基于多層次青稞RISC-V微處理器、多類型物理層收發(fā)器構(gòu)建USB/藍(lán)牙/以太網(wǎng)接口芯片和青稞RISC-V系列MCU/SoC,產(chǎn)品品類

2025-06-26 09:52:50 1382

1382

RISC-V是一種開放(Open)指令集架構(gòu)(ISA)標(biāo)準(zhǔn)。本報(bào)告探討了RISC-V指令集架構(gòu)標(biāo)準(zhǔn)區(qū)別于其它主流ISA的不同特點(diǎn),以及這些特點(diǎn)對(duì)于國(guó)產(chǎn)微處理器芯片(CPU)

2025-07-14 17:34:49 1092

1092

是一種開放(Open)指令集架構(gòu)(ISA)標(biāo)準(zhǔn)。本報(bào)告探討了RISC-V指令集架構(gòu)標(biāo)準(zhǔn)區(qū)別于其它主流ISA的不同特點(diǎn),以及這些特點(diǎn)對(duì)于國(guó)產(chǎn)微處理器芯片(CPU)的重

2025-07-29 17:02:45 1142

1142

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論