本文是 RISC-V 基礎知識的入門讀物。公開了開放式架構理念,以及模塊化 ISA 的技術描述,以及一些商業 RISC-V 微處理器實現。

RISC-V 開放指令集架構是當今可用的專有架構(例如 ARM 的那些)的流行替代方案。自誕生以來,RISC-V 穩步獲得了學術和商業上的普及。

了解 RISC 與 CISC

RISC 是 1980 年代提出的一種計算機架構哲學,作為英特爾、摩托羅拉和幾乎所有其他人當時提供的商業架構的替代方案。這種架構最初被稱為“復雜指令集計算機”或 CISC,它依靠密集指令集來實現被認為有用和必要的各種操作。然而,包括IBM和加州大學伯克利分校在內的許多研究團隊發現,編譯器通常最終使用這些復雜指令集的一小部分。這一發現和其他發現引發了對更大指令集的需求的質疑,將重點放在簡單性作為提高效率的一種手段。

總體而言,RISC 在許多方面與 CISC 是相反的。通常,CISC中央處理單元 (CPU)有一些寄存器和大量指令,其中大部分都可以訪問內存,而 RISC CPU 有很多寄存器和非常有限的指令集,內存訪問僅限于少數加載和存儲指示。

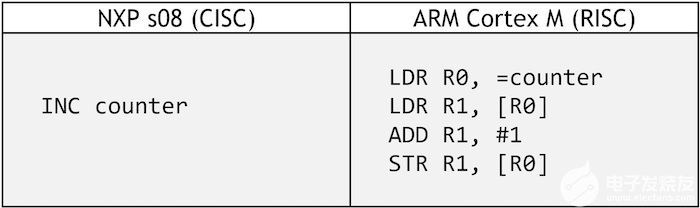

為了說明復雜指令和簡單指令之間的區別,表 1 顯示了使用 CISC CPU( NXP 的 s08)和 RISC CPU(ARM Cortex M0+ )遞增計數器變量的代碼比較。

表 1.CISC 和 RISC 代碼之間的示例比較。

在該表中,CISC 允許在單條指令中遞增變量,而 RISC 需要通過加載和存儲來訪問內存。盡管這顯示了代碼大小的差異,但這并不是蘋果對蘋果的比較,因為架構之間存在許多差異,因此這并不能證明一個在技術上比另一個更好。

今天,英特爾 x86/x64 架構證明了 CISC 微處理器沒有被 RISC 取代,而 ARM 架構證明了 RISC 已經主導了移動設備市場。

RISC-V 歷史

RISC 的首字母縮寫詞是 1980 年左右由加州大學伯克利分校的 David Patterson 教授創造的,他與斯坦福大學的 John Hennessy 教授合作產生了他們著名的著作《計算機組織與設計》和《計算機架構:一種定量方法》。由于他們在 RISC 架構上的工作,他們在 2017 年獲得了ACM AM 圖靈獎。

從 1980 年快進到 2010 年,第五代 RISC 研究項目的開發開始了,最終被稱為 RISC-V(發音為“risk-5”)。

RISC-V International——一個開放的 ISA

RISC-V 是一種開放指令集架構 (ISA),這意味著您可以自由地在微處理器或微控制器中實現 RISC-V CPU,而無需向使用此 ISA 的任何人支付版稅。

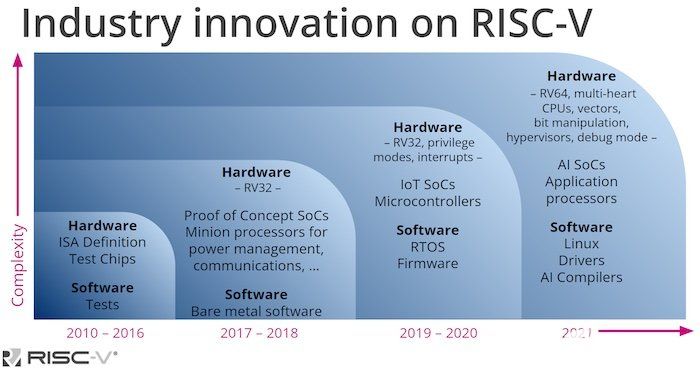

RISC-V International 是一家全球非營利組織,擁有并維護 RISC-V ISA 知識產權。其主要目標之一是保持 RISC-V 的設計基于簡單性和性能,而不是專注于商業利益。出于這個原因,RISC-V International依賴于其代表微處理器生態系統群體的成員,從個人到谷歌、英特爾和英偉達等組織。成為會員有很多好處,包括為 ISA 的設計做出貢獻的可能性,以及投票批準提議的更改。在下面的圖 1 中,您可以看到多年來 RISC-V 發展的高級時間表。

圖 1.自 2010 年問世以來,RISC-V 一直受到微處理器行業的好評,在硬件和軟件方面的采用率一直在穩步增長。圖片由RISC-V International提供

RISC-V ISA 和擴展的約定

作為始于 1980 年的第五代研究項目,RISC-V 是一種經驗豐富的架構,旨在在其他人過去可能失敗的情況下取得成功,RISC-V 旨在從任何潛在的過去錯誤中學習。

出于這個原因,RISC-V 被設計為模塊化 ISA,而不是傳統的增量 ISA。這意味著 RISC-V 實現由強制的基本 ISA 和許多 ISA 擴展組成,因此可以根據應用程序的需要定制定制 CPU。

自定義 ISA的命名約定由字母 RV(用于 RISC-V)后跟位寬和變體標識符組成。

例如,圖 2 所示的 RV32IMAC 表示:

RV32I:帶有基本整數 ISA 的 32 位 CPU

M:整數乘除法擴展

A:原子指令擴展

C:壓縮指令擴展

圖 2.RV32IMAC ISA 的指令集顯示了 RISC-V 的模塊化(非增量)特性。強制性基本 ISA 與一組擴展相結合 [點擊放大]。

編譯器被告知目標 CPU 中包含的擴展,以便它生成可能的最佳代碼。如果代碼包含缺少擴展的指令,則硬件會捕獲并執行標準庫中的軟件功能。

基本整數 ISA

只有 47 條指令,RV32I 基本整數 ISA 實現了絕對必要的操作,以實現 32 位整數的基本功能(其 64 位變體是 RV64I)。此 ISA 以 32 位編碼,包括以下指令:

添加

減法

位運算

加載和存儲

跳躍

分支機構

基本 ISA 還指定了 32 個 CPU 寄存器,它們都是 32 位寬,加上程序計數器。唯一的特殊寄存器是 x0,它總是讀取 0,正如在許多以前的 RISC ISA 中實現的那樣。

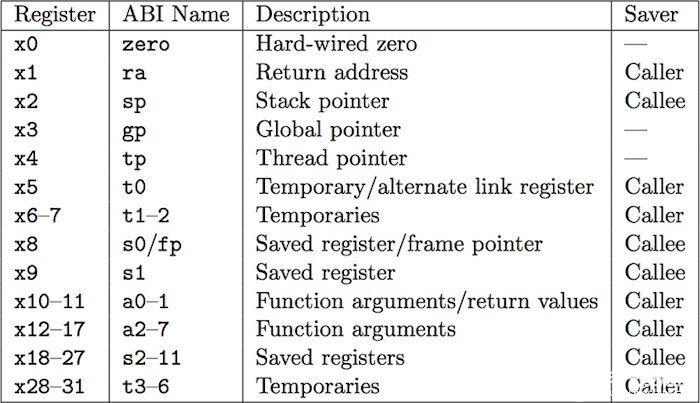

盡管表 2 中顯示的所有寄存器都可用于一般用途,但應用程序二進制接口 (ABI) 根據其調用約定為每個寄存器指定了用途。這意味著一些寄存器應該保存臨時或保存的數據、指針、返回地址等。

表 2.RV32I 寄存器文件顯示硬件寄存器名稱及其在 RISC-V 應用程序二進制接口中指定的功能。圖片由Krste Asanovi? 和 Randy H. Katz提供

RISC-V 乘法和浮點

RV32M 擴展實現了 8 條指令來對整數執行乘法和除法(RV64M 在這 8 條指令的基礎上增加了 5 條指令)。

RV32F 擴展為 32 位浮點數和 26 條浮點指令增加了 32 個獨立的寄存器。同樣,RV32D 擴展使用 32 個 64 位浮點寄存器,支持雙精度 64 位浮點數。

RISC-V 壓縮指令

RV32C 擴展是對 RISC-V ISA 的巧妙補充,因為它為現有指令的特殊子集提供了另一種 16 位編碼。

在分析了現代優化編譯器生成的無數行代碼后,RISC-V 的創建者確定了最流行的指令,并創建了 16 位版本,放棄了其完整 32 位版本的部分功能,這些功能在無論如何,RV32I 基礎 ISA。

由于以下說明,這種壓縮是可能的:

有些寄存器比其他寄存器更受歡迎。

一個操作數通常會被覆蓋。

有一些首選的立即數。

這允許將有限數量的寄存器的指令編碼為操作數,僅指定 2 個寄存器而不是 3 個,使用小的立即數,所有這些都在 16 位中。

通過壓縮最常用的指令,您有更好的機會顯著壓縮程序。

其他 RISC-V 擴展

還有許多額外的擴展,它們實現了現代微處理器所期望的所有功能。這包括嵌入式基礎 ISA (RV32E)、原子操作 (A)、位操作 (B)、向量操作 (V) 的擴展,等等。

RISC-V 實現

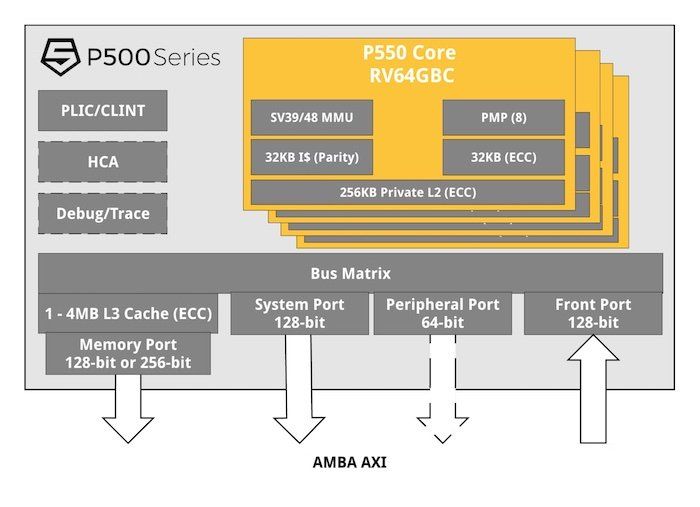

許多公司在其微控制器、微處理器和 SoC 中制造各種 RISC-V 內核。一個例子是 SiFive,第一家制造基于 RISC-V ISA 的硅的公司。他們的芯片范圍從低端微控制器一直到高性能 SoC。

圖 3.RISC-V 框圖示例,即 P550 高性能應用處理器的框圖。圖片由SiFive提供

然而,實際的 RISC-V 項目并不局限于集成電路。在許多領域,如編譯器、模擬器、開發環境、操作系統等,有大量正在進行的項目。有關項目的詳細列表,您可以訪問此 GitHub以了解更多信息。

總而言之,RISC-V 是計算機體系結構世界中一個令人興奮的話題,今天是參與其中的好時機。如果您想了解有關此運動的更多信息,請務必訪問RISC-V 國際網站。

審核編輯 黃昊宇

-

ISA

+關注

關注

0文章

57瀏覽量

44535 -

RISC

+關注

關注

6文章

485瀏覽量

86796 -

架構

+關注

關注

1文章

534瀏覽量

26631 -

RSIC-V

+關注

關注

4文章

17瀏覽量

6983

發布評論請先 登錄

新思科技ImperasDV解決方案讓RISC-V處理器驗證效率翻倍

RT-Thread 邀您參與“開放?連接”2026玄鐵 RISC-V 生態大會,攜手共鑄 RISC-V“芯”紀元

RISC-V,正式崛起

重磅合作!Quintauris 聯手 SiFive,加速 RISC-V 在嵌入式與 AI 領域落地

為什么RISC-V是嵌入式應用的最佳選擇

深度數智亮相2025年RISC-V北美峰會,攜手共創開放式AI計算未來

大灣區RISC-V生態全景展示:RISC-V生態發展論壇、開發者Workshop和生態應用專區

明晚開播 |開源芯片系列講座第28期:高性能RISC-V微處理器芯片

RISC-V 手冊

RISC-V 的平臺思維和生態思維

RISC-V International CEO:RISC-V 應用全面開花,2031 年滲透率將達 25.7%

直播預約 |開源芯片系列講座第28期:高性能RISC-V微處理器芯片

RISC-V賽道的“硬核”突圍之路

FPGA與RISC-V淺談

RISC-V 簡介——理解 RISC 的開放式 ISA

RISC-V 簡介——理解 RISC 的開放式 ISA

評論