Cadence設(shè)計系統(tǒng)公司公布一個新版的尖端功能驗證平臺與方法學(xué),擁有全套最新增強功能,與之前發(fā)布的版本相比,可將SoC驗證效率提高一倍。 Incisive ?12.2提供了兩倍性能,全新Incisive調(diào)試分析器產(chǎn)品,全新低功耗建模,以及當(dāng)今復(fù)雜IP與SoC高效驗證所需的數(shù)百種其他功能。

2013-01-27 10:44:38 1909

1909

全球電子設(shè)計創(chuàng)新領(lǐng)先企業(yè)Cadence設(shè)計系統(tǒng)公司(NASDAQ: CDNS),近日推出新版本Incisive Enterprise Simulator,該版本將復(fù)雜SoC的低功耗驗證效率提高了30

2013-05-14 10:31:40 2676

2676 意味著通過臺積電嚴(yán)格的EDA工具驗證過的Cadence Tempus 時序簽收解決方案能夠確保客戶實現(xiàn)先進(jìn)制程節(jié)點的最高精確度標(biāo)準(zhǔn)。

2013-05-24 11:31:17 1786

1786 了芯片復(fù)雜性的增加和片上系統(tǒng)(SoC)設(shè)計要求的變化,例如重新架構(gòu)(特別是傳統(tǒng)控制器局域網(wǎng)(CAN)的車載電氣/電子(E/E)架構(gòu))、車載以太網(wǎng)的引入、更高的速度以及與各種標(biāo)準(zhǔn)兼容的實時控制。驗證這些復(fù)雜的SOC可能會占用高達(dá)70%的

2024-04-08 18:38:06 3248

3248

Cadence設(shè)計系統(tǒng)公司發(fā)布了Cadence Allegro系統(tǒng)互連設(shè)計平臺針對印刷電路板(PCB)設(shè)計進(jìn)行的全新產(chǎn)品和技術(shù)增強。改進(jìn)后的平臺為約束驅(qū)動設(shè)計提供了重要的新功能,向IC、封裝和板

2018-11-23 17:02:55

解決方案的基礎(chǔ),通過集成的散熱、功率消耗和靜態(tài)時序分析功能,為客戶提供系統(tǒng)驅(qū)動的功率、性能和面積 (PPA),用于單個小芯片。 Cadence? Integrity? 3D-IC 平臺是業(yè)界首個綜合性

2021-10-14 11:19:57

%, 使用戶得以更快、更有預(yù)見性地創(chuàng)建產(chǎn)品。同時,新型信號集成流引入了更高層次的自動化水平,使得快速設(shè)計所需要的預(yù)布線拓?fù)洹⒓s束開發(fā)和發(fā)展的性能導(dǎo)向數(shù)字電路模擬具有了更好的可用性和生產(chǎn)率。在新版本的發(fā)布會

2012-12-18 10:18:07

及屬性提供了位置。 提升的生產(chǎn)率和仿真精確性 新發(fā)布的Allegro平臺在Allegro PCB SI 及PCB PI中提供了新的功能,可縮短互連設(shè)計時間并提升產(chǎn)品性能和可靠性。這些性能包括了串行

2018-08-28 15:28:45

和解決這些不斷增加的復(fù)雜度難題的流程和方法學(xué),從而樹立了全新PCB設(shè)計典范。 “新的Allegro平臺版本引入了很多新的生產(chǎn)率特性,將為象我一樣的設(shè)計師帶來優(yōu)勢,”加拿大Kaleidescape高級

2008-06-19 09:36:24

先進(jìn)的設(shè)計與仿真驗證方法成為SoC設(shè)計成功的關(guān)鍵。一個簡單可行的SoC驗證平臺,可以加快SoC系統(tǒng)的開發(fā)與驗證過程。FPGA器件的主要開發(fā)供應(yīng)商都針對自己的產(chǎn)品推出了SoC系統(tǒng)的開發(fā)驗證平臺,如

2019-10-11 07:07:07

聯(lián)合開發(fā),以促進(jìn)真正的 SystemVerilog 與標(biāo)準(zhǔn)庫和經(jīng)過驗證的方法的互操作性。它完全開放,結(jié)合了 Cadence? Incisive? Plan-to-Closure Universal

2022-02-13 17:03:49

未來的FPGA,將會采用創(chuàng)新的迭堆式封裝(SIP),即在一個封裝里放多個裸片的技術(shù),到那時,F(xiàn)PGA將成為一個標(biāo)準(zhǔn)的、虛擬的SoC平臺來應(yīng)用。” 半導(dǎo)體行業(yè)最讓人稱道的是,能把沙子做成比金子還要貴

2019-07-17 07:08:07

DN206-LTC1702 / LTC1703開關(guān)穩(wěn)壓器控制器為瞬態(tài)響應(yīng)設(shè)定了新標(biāo)準(zhǔn)

2019-07-15 08:15:22

USB Type-C?、USB PD 和 USB 3.1 第 2 代:速度和功率的新標(biāo)準(zhǔn)

2021-01-21 06:01:47

隨著現(xiàn)代集成電路技術(shù)的發(fā)展,尤其是IP的大量使用,芯片的規(guī)模越來越大,系統(tǒng)功能越來越復(fù)雜,普通的EDA和FPGA仿真在速度和性能上已經(jīng)無法勝任芯片仿真驗證的要求,功能驗證已經(jīng)成為大規(guī)模芯片設(shè)計的一個

2010-05-28 13:41:35

表面不受雨水、咸水、油或冰的影響。 營銷總監(jiān)Ian Cro***y評論:“Zytronic已為觸控性能設(shè)定了新標(biāo)準(zhǔn),使傳感器能夠在工業(yè)環(huán)境(先前不能運行的工業(yè)環(huán)境)下可靠地運行。盡管在強電磁干擾

2018-09-25 11:20:50

制化FPGA原型板驗證效率的創(chuàng)新方法,自動化現(xiàn)有的電路仿真(in-circuit emulation)偵錯功能,并提供更高的FPGA能見度。這個以FPGA為基礎(chǔ)的SoC驗證平臺對工研院而言是前景看好

2011-07-24 09:47:50

專家您好! 想請教一下ADPD105 / 108在生產(chǎn)驗證階段,要如何驗證芯片有無問題?像是G-sensor都會訂有容許的誤差標(biāo)準(zhǔn)(例如:+/- 0.1G)之類的~~ ADPD105 / 108有這

2018-07-31 08:45:30

SoC原型的Handel-C描述及其實現(xiàn)流程是怎樣的?利用RC1000和SoC設(shè)計展示評估平臺RC200搭建一個原型驗證系統(tǒng)的樣機?

2021-05-28 06:15:18

的,因為一旦你做到,就可以金石為開。”事實上,設(shè)計和驗證SoC并非易事。一個原因源于選擇和靈活性,凡事有利必有弊,組裝芯片也如此。例如,就ARM而言,企業(yè)既可購買由英國公司設(shè)計的現(xiàn)成處理器,也可自己構(gòu)建運行

2017-04-05 14:17:46

怎樣去修改RK3288平臺HDMI默認(rèn)的顯示分辨率呢?如何去實現(xiàn)呢?

2022-03-03 08:37:52

SoC系統(tǒng)驗證平臺總體框架是怎樣的?SoC系統(tǒng)驗證平臺如何去構(gòu)建?

2021-04-28 07:13:41

講述背提包和旅行箱及其配件的新標(biāo)準(zhǔn) 新的《背提包》標(biāo)準(zhǔn)是對QB/T1333-96《背提包》的修訂。新標(biāo)準(zhǔn)主要對原版本做了以下修訂:對織物面料背提包數(shù)量增加的市場需求,增加織物面料背提包要求。技術(shù)要求

2013-04-12 16:48:14

請問D1平臺tina的kernel和標(biāo)準(zhǔn)的5.4kernel有哪些區(qū)別?改動大嗎?

2021-12-28 07:12:23

。這是雙方工程團(tuán)隊為進(jìn)一步提升良率、增強可靠性并縮短生產(chǎn)周期而努力合作的成果。Virtex-6系列通過生產(chǎn)驗證,意味著聯(lián)華電【關(guān)鍵詞】:生產(chǎn)驗證,高性能,電子,可靠性,生產(chǎn)周期,系列,制造工藝,生產(chǎn)

2010-04-24 09:06:05

常年使用一種 EDA 工具顯然可以提高效率,同時也會讓您習(xí)慣于自己所用的 PCB 設(shè)計工具,接受該工具的所有優(yōu)缺點。不過,隨著當(dāng)今技術(shù)的快速發(fā)展,我們需要考慮做出改變,繼而引入最新的技術(shù)方法。本文經(jīng) PCB 設(shè)計雜志授權(quán)翻印,其中討論了阻礙 PCB 設(shè)計流程的生產(chǎn)率問題。

2019-10-14 06:27:31

本文首先介紹RVM驗證方法學(xué)和覆蓋率驅(qū)動技術(shù),然后詳細(xì)分析如何使用結(jié)合覆蓋率驅(qū)動技術(shù)的RVM驗證方法學(xué)對SOC(System On Chip)進(jìn)行完備的功能驗證, 最

2009-09-05 08:53:00 15

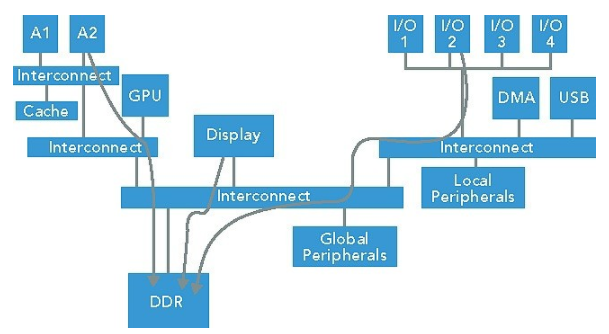

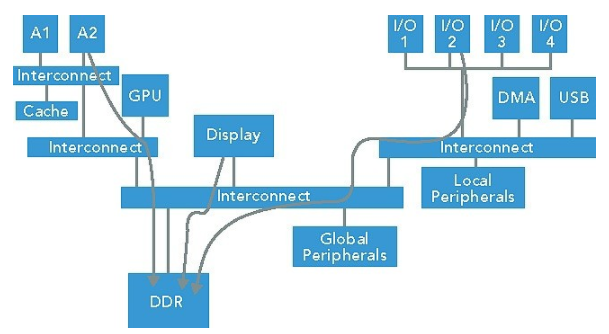

15 本文描述了SOC平臺體系結(jié)構(gòu)之低功耗高性能的數(shù)字信號處理的應(yīng)用。這個平臺是基于AMBA SOC總線協(xié)議,它結(jié)合了新穎的互連規(guī)范,為了能讓高性能的DSP IP核集成到SOC平臺中,這個規(guī)范

2010-02-01 13:58:40 14

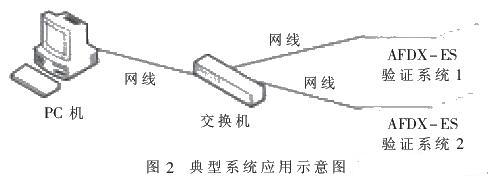

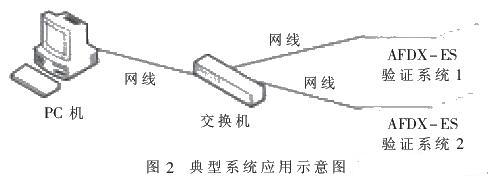

14 以SoC軟硬件協(xié)同設(shè)計方法學(xué)及驗證方法學(xué)為指導(dǎo),系統(tǒng)介紹了以ARM9為核心的AFDX-ES SoC設(shè)計過程中,軟硬件協(xié)同設(shè)計和驗證平臺的構(gòu)建過程及具體實施。應(yīng)用實踐表明該平臺具有良

2010-11-22 15:18:52 56

56 Cadence推出首個TLM驅(qū)動式設(shè)計與驗證解決方案

Cadence設(shè)計系統(tǒng)公司今天推出首個TLM驅(qū)動式協(xié)同設(shè)計與驗證解決方案和方法學(xué),使SoC設(shè)計師們可以盡享事務(wù)級建模(TLM)的好處。

2009-08-07 07:32:00 931

931 Cadence推出首個TLM驅(qū)動式設(shè)計與驗證解決方案提升基于RTL流程的開發(fā)效率

Cadence設(shè)計系統(tǒng)公司推出首個TLM驅(qū)動式協(xié)同設(shè)計與驗證解決方案和方法學(xué),使SoC設(shè)計師們可以盡

2009-08-11 09:12:18 756

756

電池國家最新標(biāo)準(zhǔn)發(fā)布公告

2009-11-02 15:55:24 1163

1163 Cadence為PCI Express 3.0推出首款驗證解決方案

Cadence設(shè)計系統(tǒng)公司宣布其已經(jīng)開發(fā)了基于開放驗證方法學(xué)(OVM)的驗證IP(VIP)幫助開發(fā)者應(yīng)用最新的PCI Express Base Specification

2009-11-04 16:59:59 1531

1531 優(yōu)化上料組合、提高生產(chǎn)率

隨著SIPLACE SiCluster Professional優(yōu)化軟件的面世,西門子電子裝配系統(tǒng)有限公司(

2009-11-24 17:12:56 785

785 GF、ARM共同定義行動技術(shù)平臺新標(biāo)準(zhǔn)

GLOBALFOUNDRIES與ARM日前于2010 MWC中,公布針對新一代無線產(chǎn)品及應(yīng)用開發(fā)的尖端系統(tǒng)單芯片(SoC)平臺全新細(xì)節(jié)資料。全新的芯片生產(chǎn)制

2010-02-26 08:55:44 774

774 芯邦采用Cadence Incisive Xtreme III系統(tǒng)提升SoC驗證實效

全球電子設(shè)計創(chuàng)新領(lǐng)先企業(yè)Cadence設(shè)計系統(tǒng)公司今天宣布,位于中國深圳的、無晶圓廠集成電路設(shè)計領(lǐng)先企業(yè)芯邦科

2010-03-02 10:32:47 836

836 電池輔助無源RFID平臺新標(biāo)準(zhǔn)

Intelleflex是功能增強型RFID( Extened Capability RFID) 平臺的領(lǐng)軍企業(yè),近期宣布推出新一代、標(biāo)準(zhǔn)化電池輔助無源XC3技術(shù)平臺

2010-05-24 11:22:40 792

792 全球電子設(shè)計創(chuàng)新領(lǐng)先企業(yè)Cadence設(shè)計系統(tǒng)公司,今天宣布了業(yè)界最全面的用于系統(tǒng)級芯片(SoC)驗證的通用驗證方法學(xué)(UVM)開源參考流程。為了配合Cadence EDA360中SoC實現(xiàn)能力的策略,

2010-06-28 08:29:14 2864

2864 摘 要: 以SoC軟硬件協(xié)同設(shè)計方法學(xué)及驗證方法學(xué)為指導(dǎo),系統(tǒng)介紹了以ARM9為核心的AFDX-ES SoC設(shè)計過程中,軟硬件協(xié)同設(shè)計和驗證平臺的構(gòu)建過程及具體實施。應(yīng)用實踐表明該

2010-12-08 10:44:41 1443

1443

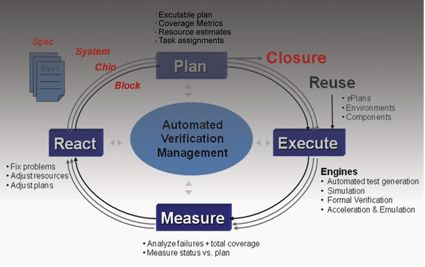

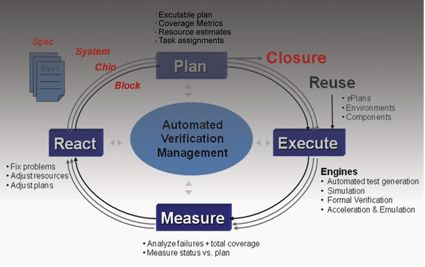

Cadence設(shè)計系統(tǒng)公司600多種新功能擴展了指標(biāo)驅(qū)動型驗證(MDV)的范圍,幫助工程師實現(xiàn)更快、更全面的驗證閉合與硅實現(xiàn)。

2011-01-13 11:26:17 961

961 Cadence Incisive Conformal ASIC是Incisive驗證平臺等效檢查解決方案的一部分,設(shè)計者無需測試向量就能驗證和調(diào)試數(shù)百萬門的設(shè)計。它組合了業(yè)界最優(yōu)的等效檢查工具和擴展功能檢查,數(shù)據(jù)路

2011-04-13 23:40:45 17

17 電子設(shè)計創(chuàng)新企業(yè)Cadence設(shè)計系統(tǒng)公司(NASDAQ: CDNS)今天宣布,中國科學(xué)院計算技術(shù)研究所(簡稱計算所)采用了Cadence? Incisive?Xtreme Ⅲ? 系統(tǒng),來加速其下一代6400萬門以上龍芯3號高級多

2011-05-27 10:49:34 799

799 芯片驗證的工作量約占整個芯片研發(fā)的70%,已然成為縮短芯片上市時間的瓶頸。應(yīng)用OVM方法學(xué)搭建SoC設(shè)計中的DMA IP驗證平臺,可有效提高驗證效率。

2012-06-20 09:03:29 3272

3272 電子設(shè)計創(chuàng)新企業(yè)Cadence設(shè)計系統(tǒng)公司,今天宣布使用ARM AMBA協(xié)議類型的Cadence驗證IP(VIP)實現(xiàn)多個成功驗證項目,這是業(yè)界最廣泛使用的AMBA協(xié)議系列驗證解決方案之一。頂尖客戶,包括

2012-11-07 08:21:52 1357

1357 光刻物理分析器成功完成20納米系統(tǒng)級芯片(SoC)測試芯片流片。雙方工程師通過緊密合作,運用Cadence解決方案克服實施和可制造性設(shè)計(DFM)驗證挑戰(zhàn),并最終完成設(shè)計。

2013-07-09 15:53:24 1053

1053 為專注于解決先進(jìn)節(jié)點設(shè)計的日益復(fù)雜性,全球電子設(shè)計創(chuàng)新領(lǐng)先企業(yè)Cadence設(shè)計系統(tǒng)公司(NASDAQ:CDNS) 今天宣布,臺積電已與Cadence在Virtuoso定制和模擬設(shè)計平臺擴大合作以設(shè)計和驗證其尖端IP。

2013-07-10 13:07:23 1201

1201 2013年9月10日 —— 為了進(jìn)一步縮短半導(dǎo)體和系統(tǒng)制造商的產(chǎn)品上市時間,全球電子設(shè)計創(chuàng)新領(lǐng)先企業(yè)Cadence 設(shè)計系統(tǒng)公司 (NASDAQ:CDNS) 今日推出 Palladium? XP II 驗證計算平臺,它作為系統(tǒng)開發(fā)增強套件的一部分,可顯著加快硬件和軟件聯(lián)合驗證的時間。

2013-09-11 10:10:12 3712

3712 徹底地驗證其片上系統(tǒng)(SoC)是否符合HDMI 2.0規(guī)范,從而加速批量生產(chǎn)的準(zhǔn)備時間。這款用于HDMI 2.0的Cadence VIP支持各種主流邏輯模擬器、驗證語言及包括UVM(Universal Verification Methodology)在內(nèi)的方法學(xué)。

2013-09-27 16:19:08 1215

1215 Workbench搭配Cadence Interconnect Validator,組成了一套完整的功能驗證與性能檢驗解決方案。

2013-11-07 09:34:14 1477

1477 ) 通過采用Cadence?完整的工具流程,已成功完成該公司最大型的SoC (系統(tǒng)單芯片) 項目開發(fā),該項目是用于4G基站的3億門芯片設(shè)計。通過在其分層式 (hierarchical) 設(shè)計流程中部

2013-11-19 10:30:13 1225

1225 全球電子設(shè)計創(chuàng)新領(lǐng)先企業(yè)Cadence設(shè)計系統(tǒng)公司(NASDAQ: CDNS)今天宣布,海思半導(dǎo)體(HiSilicon Semi)進(jìn)一步擴大采用Cadence? Palladium? XP 驗證運算平臺作為其仿真方案,運用于移動和數(shù)字媒體System-on-Chip (SoC) 與 ASIC開發(fā)。

2014-05-13 16:19:03 3372

3372 SoC基于IP設(shè)計的特點使驗證項目中多語言VIP(Verification IP)協(xié)同驗證的需求不斷增加,給驗證工作帶來了很大的挑戰(zhàn)。為了解決多語言VIP在SoC驗證環(huán)境靈活重用的問題。提出了一種

2015-12-31 09:25:13 12

12 2016 年 2 月 26 日─ Imagination Technologies 宣布,推出適用于大眾市場的新系列 PowerVR GPU 產(chǎn)品,為成本敏感市場設(shè)立了性能、功耗與面積的新標(biāo)準(zhǔn)。

2016-02-26 11:11:25 980

980 快速設(shè)定分辨率快速設(shè)定分辨率快速設(shè)定分辨率快速設(shè)定分辨率

2016-04-28 11:45:51 4

4 ? 可以顯著縮短片上系統(tǒng)(SoC)面市時間。較Cadence上一代仿真平臺,Xcelium? 單核版本性能平均可提高2倍,多核版本性能平均可提高5倍以上。

2017-03-01 15:57:05 5721

5721 2017年3月2日,上海——楷登電子(美國 Cadence 公司,NASDAQ: CDNS)今日發(fā)布全新基于FPGA的Protium? S1原型驗證平臺。借由創(chuàng)新的實現(xiàn)算法,平臺可顯著提高工程生產(chǎn)

2017-03-02 11:13:11 3210

3210 設(shè)計了一種基于FPGA的驗證平臺及有效的SoC驗證方法,介紹了此FPGA驗證軟硬件平臺及軟硬件協(xié)同驗證架構(gòu),討論和分析了利用FPGA軟硬件協(xié)同系統(tǒng)驗證SoC系統(tǒng)的過程和方法。利用此軟硬件協(xié)同驗證

2017-11-17 03:06:01 21471

21471

設(shè)計了一種基于FPGA的驗證平臺及有效的SoC驗證方法,介紹了此FPGA驗證軟硬件平臺及軟硬件協(xié)同驗證架構(gòu),討論和分析了利用FPGA軟硬件協(xié)同系統(tǒng)驗證SoC系統(tǒng)的過程和方法。利用此軟硬件協(xié)同驗證

2017-11-17 03:06:01 5211

5211

在系統(tǒng)芯片的設(shè)計中,傳統(tǒng)的激勵發(fā)生機制耗費人工多且難以重用,嚴(yán)重影響了仿真驗證的效率。針對此問題,構(gòu)建了一種基于可重用激勵發(fā)生機制的虛擬SoC驗證平臺。該平臺利用可重用的激勵發(fā)生模塊調(diào)用端口激勵文件

2017-11-28 17:43:39 0

0 為了充分利用系統(tǒng)級芯片(SoC)設(shè)計帶來的優(yōu)點,業(yè)界需要一種可以擴展的驗證解決方案,解決設(shè)計周期中各個階段的問題,縮短驗證鴻溝。本文將探討可擴展驗證解決方案為何能夠以及如何解決SoC設(shè)計目前面臨的功能方面的嚴(yán)峻挑戰(zhàn),以達(dá)到提高設(shè)計生產(chǎn)力、保證設(shè)計質(zhì)量、縮短產(chǎn)品上市時間以及提高投資回報率的目的。

2018-06-04 03:13:00 1261

1261

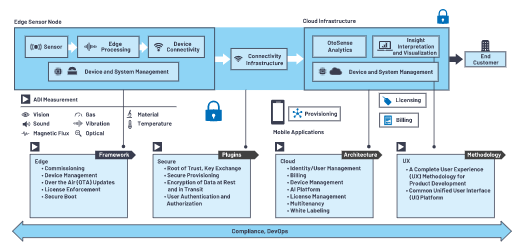

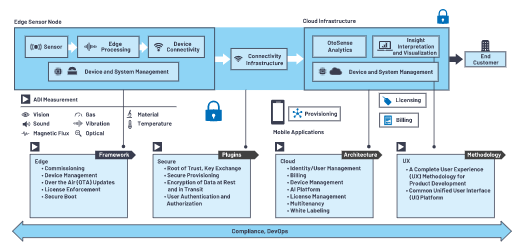

由于卡車運送了如此多的貴重貨物,所以需要您的企業(yè)盡可能地高效管理其車隊并保持低成本和高生產(chǎn)率。 今天,許多企業(yè)正在通過物聯(lián)網(wǎng)(IoT)實現(xiàn)這一目標(biāo)。

2018-07-09 09:43:00 1932

1932 此款混合傳感器結(jié)構(gòu)簡單,性能穩(wěn)定,可使生產(chǎn)率得到大幅提高。Vishay Intertechnology亦供應(yīng)帶引線和連接器的混合傳感器。因無需焊接操作,從而進(jìn)一步簡化了客戶端的處理要求。所用微型信號放大器可作為分立元件或附在傳感器內(nèi)。

2018-09-07 16:13:18 1068

1068 隨著人工智能技術(shù)應(yīng)用到標(biāo)準(zhǔn)化、重復(fù)性的機械自動化過程,銀行和保險等行業(yè)的后勤工作崗位不僅在數(shù)量上逐漸減少,而且在形式上也在發(fā)生改變。“半人馬智能”(即人機合作智能)在軟件編程等核心工作領(lǐng)域逐漸興起。它將人工智能與人類能力相結(jié)合,形成一種共生關(guān)系,推動生產(chǎn)率的顯著提升。

2019-01-17 09:24:53 2629

2629 華威大學(xué)(University of Warwick)的研究發(fā)現(xiàn),快樂能使個人的工作效率提高12%。擁有一支快樂的員工隊伍可能是提高生產(chǎn)率的第一步,但適當(dāng)?shù)墓ぞ吆拖冗M(jìn)的技術(shù)將大大提高生產(chǎn)率,尤其是對工業(yè)制造商而言。本文解釋了制造商如何使用自動機器視覺系統(tǒng)來提高生產(chǎn)率。

2019-03-29 14:46:28 2732

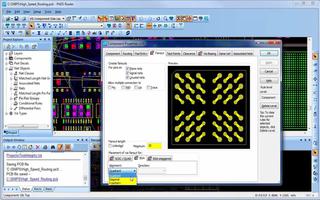

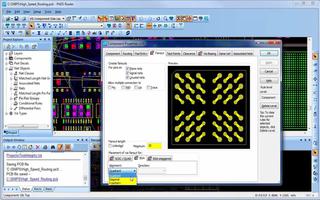

2732 參加本研討會可了解 PADS VX 版如何提高全流程的設(shè)計生產(chǎn)率。

2019-05-20 06:10:00 3569

3569

提高您的工作效率和生產(chǎn)率。在 PADS Standard 中使用簡單易用的約束管理來創(chuàng)建和輸入設(shè)計約束。

2019-05-17 06:22:00 2317

2317

PADS 包括可為射頻和微波設(shè)計提供消除手工操作、提高生產(chǎn)率的高級功能。

2019-05-15 06:16:00 3384

3384

PADS 為高速網(wǎng)絡(luò)布線提供了一個可擴展的環(huán)境,在該環(huán)境中可進(jìn)行交互和自動兩種模式。高速網(wǎng)絡(luò)的規(guī)則,例如匹配長度、差分對等,非常容易設(shè)置。在布線過程中,您將得到針對關(guān)鍵和敏感網(wǎng)絡(luò)的實時布線長度反饋。PADS 高速布線可成為提高您 PCB 設(shè)計生產(chǎn)率的“利器”。

2019-05-14 06:02:00 4343

4343

全球領(lǐng)先的半導(dǎo)體制造設(shè)備及服務(wù)供應(yīng)商泛林集團(tuán)宣布其自維護(hù)設(shè)備創(chuàng)下半導(dǎo)體行業(yè)工藝流程生產(chǎn)率的新標(biāo)桿。通過與領(lǐng)先半導(dǎo)體制造商合作,泛林集團(tuán)成功實現(xiàn)了刻蝕工藝平臺全年無間斷運行。

2019-05-15 17:49:27 1505

1505 Command Center工具的新功能基于客戶對可用性和生產(chǎn)率的反饋,并且引入了幾種關(guān)鍵功能,使場景定義和設(shè)計空間探索既直觀又快速:易于查找的對象、屬性和設(shè)置;“查找”工具配備多個用于派生設(shè)計創(chuàng)建的應(yīng)用程序;輕松地與電子表格工具進(jìn)行交互,以及數(shù)百個模型的高效仿真。

2019-10-11 16:45:02 5403

5403 SAN JOSE - Cadence Design Systems Inc.今天宣布推出基于塊的設(shè)計(BBD)和基于平臺的設(shè)計(PBD) )方法和工具流向蘇格蘭的阿爾巴中心。 BBD和PBD是用于片上系統(tǒng)(SoC)開發(fā)的一套完全編碼和驗證的設(shè)計方法。

2019-08-13 09:03:45 2138

2138 機器人和其他自動化技術(shù)極大地提高了當(dāng)今工廠的生產(chǎn)率。但是,它們?nèi)匀挥幸粋€主要限制:它們要求人們告訴他們該怎么做。

2019-11-13 10:14:11 820

820 在上周發(fā)布iOS 13.2.2正式版之后,蘋果今日停止了對iOS 13.2的驗證,這意味著用戶無法再降級到iOS 13.2。

2019-11-15 15:46:07 3034

3034 傳感器應(yīng)用來自傳感器專家Micro-Epsilon的optoNCDT 1220、1320和1420激光三角測量傳感器為位移和距離測量設(shè)定了新標(biāo)準(zhǔn)。這些小巧、智能、精確的傳感器具有微型光斑尺寸,可以

2020-09-22 15:29:32 3390

3390 的公差范圍內(nèi),則您的電路板可以達(dá)到最佳結(jié)果,并可以達(dá)到最佳良率。在定義如何選擇最佳的 PCB 公差之前,我們應(yīng)明確定義缺陷以及哪種類型會影響我們 100 %生產(chǎn)率的目標(biāo)。 公差如何影響生產(chǎn)率? 完全組裝的 PCB 或 PCBA 的良率通常與建造大量板有關(guān)

2020-09-29 18:24:08 3138

3138 據(jù)國外媒體報道,豐田與松下合資的電動汽車電池公司社長好田博昭日前表示,正在設(shè)法提高公司生產(chǎn)率。 好田博昭表示,若生產(chǎn)率提升至 10 倍,就能勝過中國廠商。 豐田和松下今年早些時候成立了合資公司泰星

2020-10-28 14:04:28 2092

2092 12月4日消息,據(jù)國外媒體報道,巴西農(nóng)業(yè)州戈亞斯州(Goias)周四推出了一個試點項目,通過使用華為提供的5G技術(shù)和設(shè)備來提高生產(chǎn)率,并針對作物疾病采取快速行動。

2020-12-04 11:03:35 1775

1775 Cadence Palladium Z1 企業(yè)級仿真平臺和 Cadence Protium X1 企業(yè)級原型驗證平臺來實現(xiàn)硬件仿真和原型驗證。

2021-03-19 09:37:06 3214

3214 隨著芯片技術(shù)的不斷發(fā)展,特別是芯片工藝水平的提升,芯片規(guī)模越來越大,這也為芯片邏輯功能驗證帶來了很大的挑戰(zhàn)。如何保證產(chǎn)品上市時間(Time?to?Market),快速完成功能驗證和達(dá)成較高的覆蓋率

2021-03-28 10:52:02 5780

5780

Cadence擁有最完整的IP與SoC驗證、硬件與軟件回歸測試及早期軟件開發(fā)的全系列解決方案。

2021-04-06 13:48:53 3438

3438 中國上海,2022年4月21日——楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日宣布推出 Cadence? Fidelity? CFD 軟件平臺,為多物理場仿真的性能和準(zhǔn)確度開創(chuàng)新時代。

2022-04-21 11:36:50 3186

3186 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日宣布推出 15 種新的驗證 IP(VIP)解決方案,助力工程師迅速有效地驗證設(shè)計,以滿足最新標(biāo)準(zhǔn)協(xié)議的要求。

2022-06-06 11:18:21 4799

4799 面對持續(xù)不斷的上市時間壓力和日益復(fù)雜的 SoC 設(shè)計,很難找到不想從設(shè)計周期中縮短時間的工程師。特別是在高級節(jié)點,驗證 SoC 互連已成為一個耗時的步驟。但是,工具現(xiàn)在可以高效且有效地執(zhí)行周期精確的性能分析和互連驗證。

2022-06-14 10:12:17 3131

3131

Infinity探頭通過確保在鋁墊上進(jìn)行更好的測量,減少重新探測和測量數(shù)據(jù)中的誤差,樹立了新的標(biāo)準(zhǔn)。了解它如何提高工程師的生產(chǎn)率。 我們的設(shè)備表征和建模的理想選擇InfinityProbe?系列產(chǎn)品

2022-07-15 14:19:55 1684

1684 設(shè)定新標(biāo)準(zhǔn):高清音頻正在改變著我們的收聽方式

2022-11-03 08:04:38 0

0 來收集設(shè)備數(shù)據(jù)并采用 高級分析和算法,可對 設(shè)備。因此,這種方法有望提高整體工業(yè)水平。 生產(chǎn)率提高 30% 以上。

2022-12-14 14:18:39 1560

1560

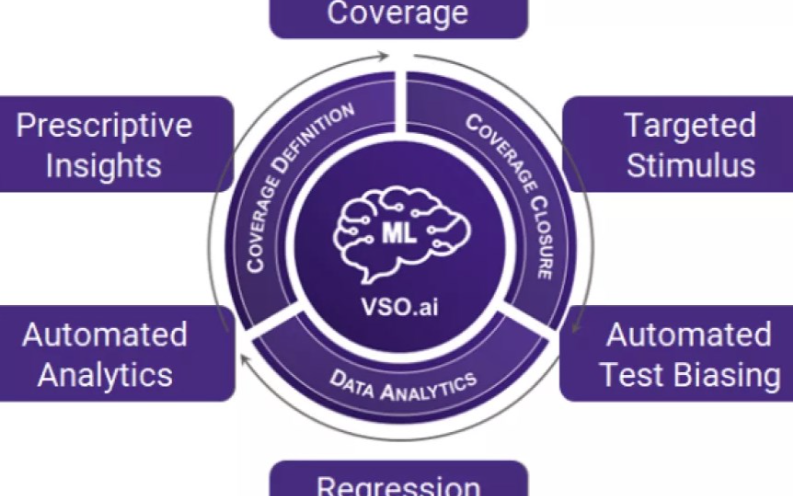

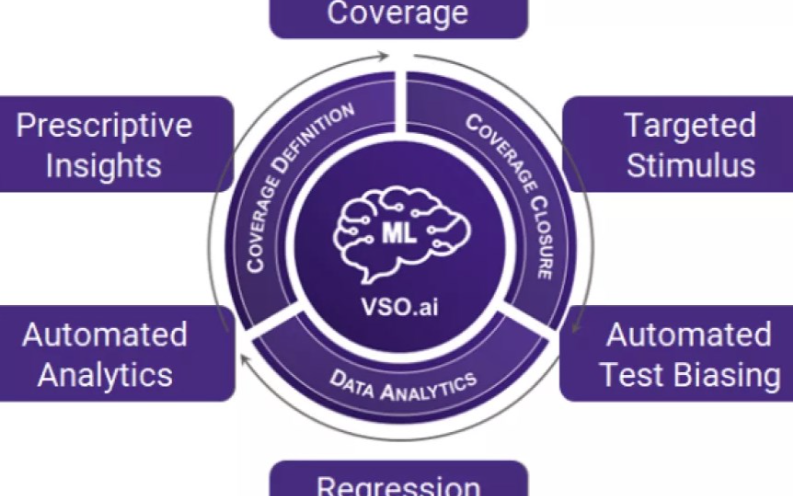

楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日宣布,瑞薩電子(Renesas Electronics)已采用全新的人工智能(AI)驅(qū)動的 Cadence Verisium 驗證

2023-03-15 09:07:00 1513

1513 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布擴大與臺積電和微軟的合作,致力于加快千兆級規(guī)模數(shù)字設(shè)計的物理驗證。通過此次最新合作,客戶可以在帶有 Cadence

2023-04-26 18:05:45 1484

1484 Cadence 在面對 SoC 設(shè)計驗證挑戰(zhàn)下的應(yīng)對之法。 隨著 SoC 設(shè)計的發(fā)展,如何在有限的時間內(nèi)盡可能發(fā)現(xiàn)更多的 bug 和實現(xiàn)更多的溯源分析,讓項目各方面的投資都做到物盡其用,這是驗證工作所面臨

2023-06-07 00:20:03 1659

1659

◆ 高進(jìn)給速度和強力主軸大幅提高了生產(chǎn)率

◆ 降低環(huán)境負(fù)荷和運行成本的環(huán)保操作

2023-02-03 16:16:34 1700

1700

內(nèi)容提要 ●? Cadence Integrity 3D-IC 平臺現(xiàn)已全面支持最新版 3Dblox 2.0 標(biāo)準(zhǔn),涵蓋 TSMC 的 3DFabric 產(chǎn)品 ●? Integrity 3D-IC

2023-10-08 15:55:01 979

979 即用,且通過 ISO 體系認(rèn)證的安全云平臺,可提供一個完全集成且經(jīng)過驗證的環(huán)境,快速啟動產(chǎn)品設(shè)計、驗證和實施工作。在我們演示 Cadence 數(shù)字和模擬設(shè)計流程的生產(chǎn)力功能時,您將看到該平臺的實際應(yīng)用。 線上研討會內(nèi)容要點 ● ?無論是完整還是局部設(shè)計流程,客戶皆可實現(xiàn)在云端加速

2023-10-09 19:25:08 1036

1036

雙方的共同客戶可獲取 Cadence 的全流程系統(tǒng)級設(shè)計驗證和實現(xiàn)解決方案以及接口 IP,依托 Neoverse CSS 加速開發(fā)基于 Arm 的定制 SoC 中國上海,2023 年 10 月 25

2023-10-25 10:40:02 1100

1100

新時代的到來。 該系統(tǒng)是在Cadence業(yè)界領(lǐng)先的Palladium Z2和Protium X2系統(tǒng)的基礎(chǔ)上,針對日益復(fù)雜的系統(tǒng)和半導(dǎo)體設(shè)計需求而研發(fā)的顛覆性數(shù)字孿生平臺。其旨在加速更先進(jìn)的SoC開發(fā)進(jìn)度

2024-12-30 10:37:50 1159

1159 Cadence的統(tǒng)一調(diào)試平臺Verisium Debug,為從IP到SoC級別的復(fù)雜設(shè)計提供了全面的調(diào)試解決方案。該平臺集成了多種調(diào)試功能,包括RTL調(diào)試、UVM仿真平臺調(diào)試、UPF調(diào)試以及DMS

2025-02-17 11:10:06 1389

1389 工智能相結(jié)合,突破了集成電路(IC)驗證流程的極限,提高了工程團(tuán)隊的生產(chǎn)效率。 Questa One提供更快的引擎,使工程師的工作速度更快,所需的工作負(fù)載更少,能夠支持從IP到系統(tǒng)級芯片(SoC)再到系統(tǒng)的最大型、最復(fù)雜的設(shè)計,開發(fā)時還考慮了先進(jìn)的3D-IC、基于芯粒的設(shè)計和

2025-05-27 14:34:04 475

475

電子發(fā)燒友App

電子發(fā)燒友App

評論