“不必?fù)?dān)心‘摩爾定律’(Moore’s law)走到盡頭,因?yàn)樵谡麄€(gè)半導(dǎo)體發(fā)展藍(lán)圖上還有許多好辦法。”被譽(yù)為“FinFET教父”的中研院院士胡正明在日前于美國舉行的“新思科技產(chǎn)品使用者研討會(huì)”(Synopsys Users Group;SNUG)上指出,新的電晶體概念能夠?yàn)樾酒a(chǎn)業(yè)點(diǎn)燃持續(xù)發(fā)展數(shù)十年的動(dòng)力。

在新思科技執(zhí)行長發(fā)表同樣樂觀的看法后,胡正明也引用軟體設(shè)計(jì)工具進(jìn)展,分享了他的想法。

他對(duì)現(xiàn)場的數(shù)百名芯片設(shè)計(jì)人員表示,“我說半導(dǎo)體產(chǎn)業(yè)將再持續(xù)發(fā)展100年時(shí)可是認(rèn)真的,一部份的原因在于目前沒有其他替代方案,而且這個(gè)世界也需要我們。”

“所有的人都知道但卻不愿意說出口的是,電晶體尺寸微縮是一場終將邁向盡頭的競賽,而我們正朝著終點(diǎn)沖刺,”但是,胡正明指出,這并不表示半導(dǎo)體產(chǎn)業(yè)和以其為基礎(chǔ)的高科技領(lǐng)域也將劃下句點(diǎn)。

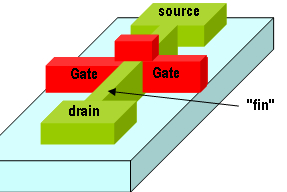

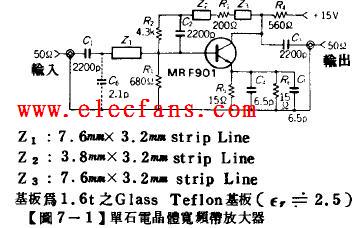

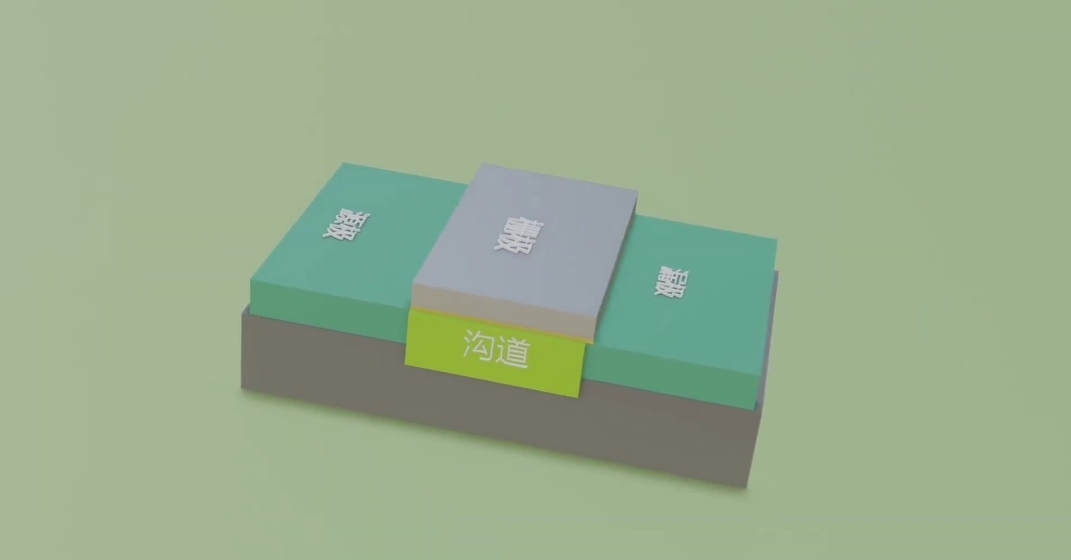

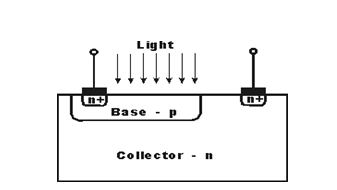

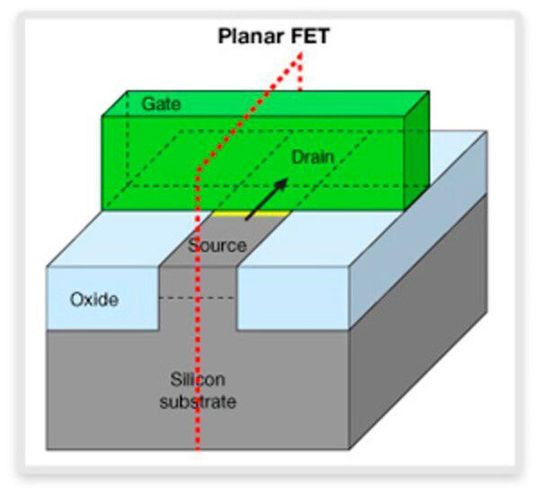

圖1:胡正明認(rèn)為像FinFET和FD-SOI等薄膜電晶體還有很長遠(yuǎn)的未來。 (來源:Synopsys)

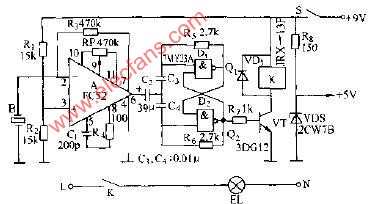

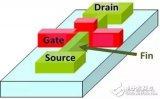

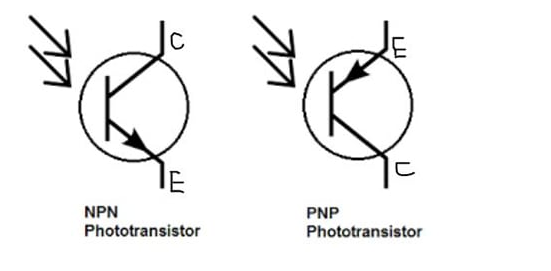

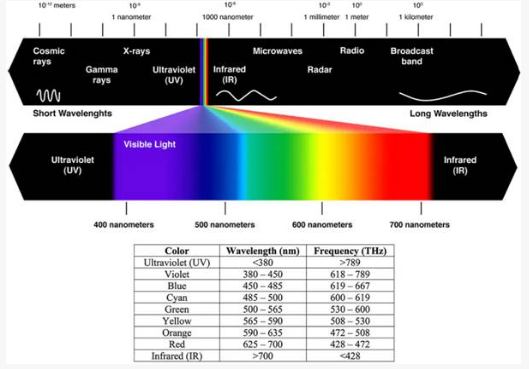

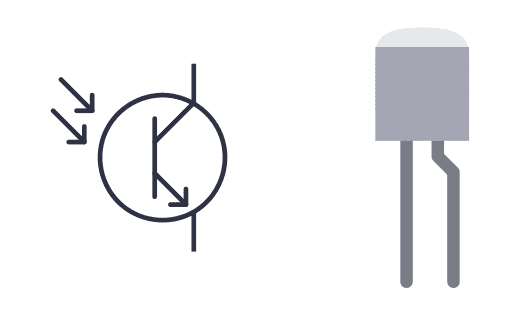

負(fù)電容電晶體(NC-FET)是來自加州大學(xué)柏克萊分校(UC Berkeley)實(shí)驗(yàn)室最新也最重要的概念之一。在該校擔(dān)任教授的胡正明與同事們展示以氧化鉿鋯和創(chuàng)新5nm鐵電層制作的30nm NC-FET研究成果。胡正明解釋,“基本上是將一個(gè)電壓放大器嵌入電介質(zhì)……其想法在于以更低的Vdd獲得相同的性能。”

這種設(shè)計(jì)可以協(xié)助工程師將Vdd電壓降低到0.3V以下,從而克服多方面的極限,為新元件未來數(shù)十年的發(fā)展鋪路。

“NC-FET一直不被看好,因?yàn)槲覀円恢笔且浴靶”窘?jīng)營”的方式進(jìn)行開發(fā),但現(xiàn)在我們認(rèn)為它很有前途,因而正積極尋求支持。”胡正明表示,“對(duì)于自旋電子領(lǐng)域的投資比NC-FET更多幾十倍, 我認(rèn)為我們是這個(gè)產(chǎn)業(yè)中唯一在研究NC-FET的團(tuán)隊(duì)。”

最近,柏克萊分校成立了一座新的研究中心專注于研發(fā)NC-FET。英特爾(Intel)和臺(tái)積電(TSMC)都參加了,也分別投資了14萬美元。“如果我們能吸引更多成員,就能實(shí)現(xiàn)偉大的成果,目前的規(guī)模仍小于一般的政府合約。”

此外,包括Globalfoundries、三星(Samsung)、Synopsys和臺(tái)積電等公司都加入了柏克萊元件建模中心,該中心創(chuàng)建的BSIM模型可以為軟體設(shè)計(jì)工具解讀晶圓廠的實(shí)體資料。

“我們正為免授權(quán)的新元件準(zhǔn)備精簡模型,不過沒有什么東西是真正免費(fèi)的。”他指出,F(xiàn)inFET模型就讓至少12位研究人員花了11年的時(shí)間。

圖2:NC-FET在傳統(tǒng)電晶體上增加了創(chuàng)新的鐵電層

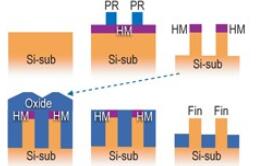

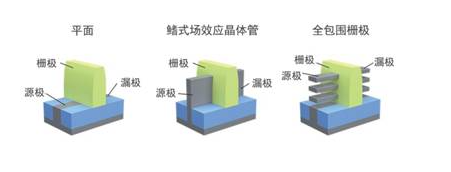

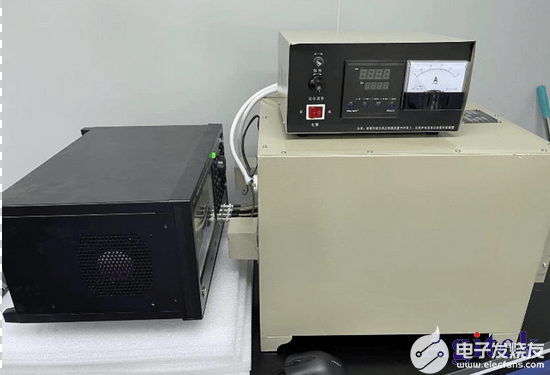

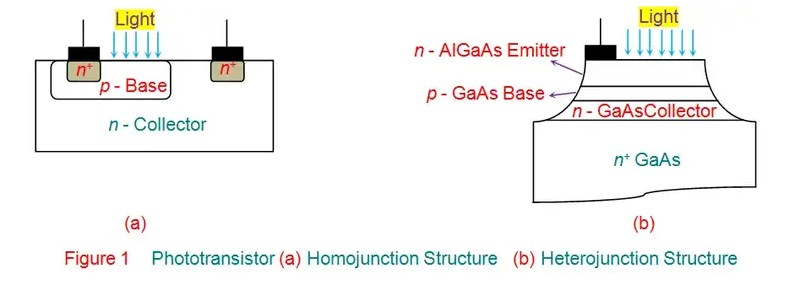

與NC-FET并駕齊驅(qū)的是,研究人員正使用十多種備選材料層來開發(fā)2D半導(dǎo)體,這些材料層能以分子或原子厚度進(jìn)行沈積。胡正明透露,“其中一種材料層可以制造出完美的晶體,最終成為理想的薄體材料,讓我們無需擔(dān)心量子效應(yīng)。”

“2D半導(dǎo)體著實(shí)令人振奮,因?yàn)椴还苁怯糜谟洃涹w還是邏輯單芯片多層整合……以氧化物分隔的電路層……使用像鉬原子等原子自組裝……這真的令人相當(dāng)興奮,可說是讓我們得以繼續(xù)進(jìn)行研究的理想介面。”

胡正明并展示了在于去年12月首次提出的2D NMOS和PMOS元件成果,這些元件被沈積于單矽層上,“并自行堆疊。”這種技術(shù)可使電晶體尺寸縮小45%。

圖3:僅以一個(gè)分子或原子厚的分層即可搭建2D半導(dǎo)體元件

這種新設(shè)計(jì)基本上是目前FinFET和完全耗盡型絕緣矽(FD-SOI)制程中使用的各種薄體元件變異。他預(yù)測這些使用各種新材料的設(shè)計(jì)將具有很長的壽命。

鰭高電晶體由于具有性能方面的優(yōu)勢,可望繼續(xù)流行。未來的制程將混合不同高度的鰭片,以便針對(duì)特定用途最佳化制程,胡正明指出,“我可以預(yù)見薄體設(shè)計(jì)將一直延用到微影技術(shù)。”

當(dāng)今的FinFET和FD-SOI結(jié)構(gòu)“可以一直發(fā)展到全包覆式電晶體(GAA)或柱或?qū)Ь€,取決于哪一種制造起來最經(jīng)濟(jì)實(shí)惠……一切都和成本與性能密不可分。”

胡正明對(duì)于穿隧電晶體和自旋電子的看法就沒那么樂觀。穿隧電晶體的導(dǎo)通電流較當(dāng)今元件的更低,使其僅適用于物聯(lián)網(wǎng)節(jié)點(diǎn)。

自旋電子必須使用全新的邏輯工具組,因而并不實(shí)用。他指出,“我們的設(shè)計(jì)基礎(chǔ)設(shè)施非常昂貴……真的難以用于導(dǎo)入一種使用完全不同概念的電晶體。”

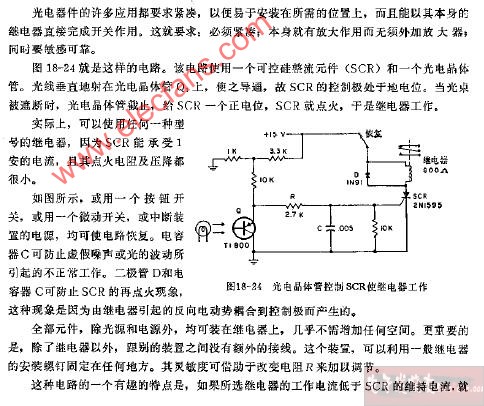

圖4:de Geus表示,在產(chǎn)業(yè)成熟期之后將迎來第二春。

現(xiàn)在正是芯片設(shè)計(jì)業(yè)的艱難時(shí)期。隨著半導(dǎo)體公司持續(xù)整并以因應(yīng)不斷攀升的芯片制造成本,新的設(shè)計(jì)案和EDA工具銷售情況都“很平淡”,Synopsys執(zhí)行長Aart de Geus引用資料指出,芯片業(yè)營收的復(fù)合年成長率(CAGR)為4.4%,而“去年和今年的成長率更趨近于零。”

盡管如此,就像胡正明一樣,de Geus在大會(huì)開幕時(shí)對(duì)于該公司在EDA方面的進(jìn)展仍顯得樂觀。

de Geus表示:“我瞭解這個(gè)產(chǎn)業(yè)正承受經(jīng)濟(jì)的壓力和變化,但我們正處于再次改變世界的浪潮中……讓每樣事物實(shí)現(xiàn)智慧化的機(jī)會(huì)十分巨大,并將徹底改變這個(gè)世界。”。

de Geus并打趣地說,IoT正象征‘無限樂觀思維’(Immensely Optimistic Thinking),因?yàn)椋八m不足以驅(qū)動(dòng)半導(dǎo)體量,但十分適于將我們與真實(shí)世界的實(shí)體特性連接在一起。無論如何,如果我們能將性能功耗比再提高10至100倍,那么IoT將出現(xiàn)令人意料不到的爆炸式成長。”

盡管FinFET還有諸多早期的問題,但Synopsys已經(jīng)以14/16nm制程投片超過50種測試芯片了。例如,瑞薩電子(Renesas Electronics)有一款高階車載資訊娛樂SoC就在臺(tái)積電16FF+制程中導(dǎo)入Synopsys的完整工具流程。

de Geus并引用一些其它進(jìn)展:

今年夏天推出的測試演算法將加快運(yùn)作時(shí)間,并減少25%的測試向量

一款14nm的網(wǎng)路SoC使用IC Compiler II使導(dǎo)線長度縮短了17%

一款7nm測試芯片以ICC II在1%的PTSI內(nèi)完成了99%的端點(diǎn)布線

使用Prime Time系統(tǒng),讓包含5,000萬個(gè)實(shí)例和20個(gè)場景的設(shè)計(jì)在8小時(shí)內(nèi)完成ECO收斂

一款名為Cheetah的最新驗(yàn)證演算法可自動(dòng)適應(yīng)處理器上的CPU和GPU核心,使RTL級(jí)的工作速度快上5倍。De Geus還介紹了Synopsys透過收購包括Coverity等公司,建立了日益 成長中的安全業(yè)務(wù)。

“對(duì)于我們來說,這已經(jīng)是一個(gè)1億美元的業(yè)務(wù)了,因此,它不再只是業(yè)余愛好,而是一個(gè)極其關(guān)鍵的方向,”De Geus表示,“每個(gè)物聯(lián)網(wǎng)裝置相當(dāng)于銀行中的一扇窗戶……事實(shí)上,世界上的所有軟體中都有這樣的窗子。”De Geus指出。

(參考原文:FinFET‘s Father Forecasts Future,by Rick Merritt)

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論